# Sistemas Digitais (SD)

Circuitos Sequenciais Básicos: Flip-Flops

### **Aula Anterior**

#### Na aula anterior:

- ► Elementos básicos de memória

- ▶ Latches

- Latch RS

- Latch RS sincronizado

- Latch D

- ▶ Flip-Flops

### **Planeamento**

| SEMANA          | TEÓRICA 1                                     | TEÓRICA 2                                                                          | PROBLEMAS/LABORATÓRIO |

|-----------------|-----------------------------------------------|------------------------------------------------------------------------------------|-----------------------|

| 01/Mar a 05/Mar | Introdução                                    | Sistemas de Numeração                                                              |                       |

| 08/Mar a 12/Mar | Álgebra de Boole                              | Elementos de Tecnologia                                                            |                       |

| 15/Mar a 19/Mar | Funções Lógicas                               | Minimização de Funções                                                             | VHDL                  |

| 22/Mar a 26/Mar | Minimização de Funções                        | Def. Circuito Combinatório; Análise Temporal                                       | P1                    |

| 29/Mar a 02/Abr | FÉRIAS DA PÁSCOA                              | FÉRIAS DA PÁSCOA                                                                   | FÉRIAS DA PÁSCOA      |

| 05/Abr a 09/Abr | Circuitos Combinatórios                       | Circuitos Combinatórios                                                            | L1                    |

| 12/Abr a 16/Abr | Circuitos Combinatórios                       | Circuitos Sequenciais: Latches                                                     | P2                    |

| 19/Abr a 23/Abr | Circuitos Sequenciais: Flip-Flops             | Caracterização Temporal                                                            | P3                    |

| 26/Abr a 30/Abr | Registos                                      | Contadores                                                                         | L2                    |

| 03/Mai a 07/Mai | Circuitos Sequenciais Síncronos               | Síntese de Circuitos Sequenciais<br>Síncronos                                      | P4                    |

| 10/Mai a 14/Mai | Síntese de Circuitos Sequenciais<br>Síncronos | Memórias                                                                           | L3                    |

| 17/Mai a 21/Mai | Exercícios Tes                                | Máq. Estado Microprogramadas: Circuito de ste 1)dos e Circuito de Controlo         | P5                    |

| 24/Mai a 28/Mai | Máq. Estado Microprogramadas: Microprograma   | Circuitos de Controlo, Transferência e<br>Processamento de Dados de um Processador | P6                    |

| 31/Mai a 04/Jun | Lógica Programável                            | P7                                                                                 | L4                    |

| 07/Jun a 11/Jun |                                               |                                                                                    |                       |

### Sumário

#### ■ Tema da aula de hoje:

- ▶ Flip-Flops

- Flip-flop master-slave

- Flip-flop JK

- Flip-flop edge-triggered

- ▶ Simbologia

### Bibliografia:

- M. Mano, C. Kime: Secções 5.3 e 5.6

- G. Arroz, J. Monteiro, A. Oliveira: Secção 6.4

### Circuitos Síncronos

#### Latches vs. Flip-Flops

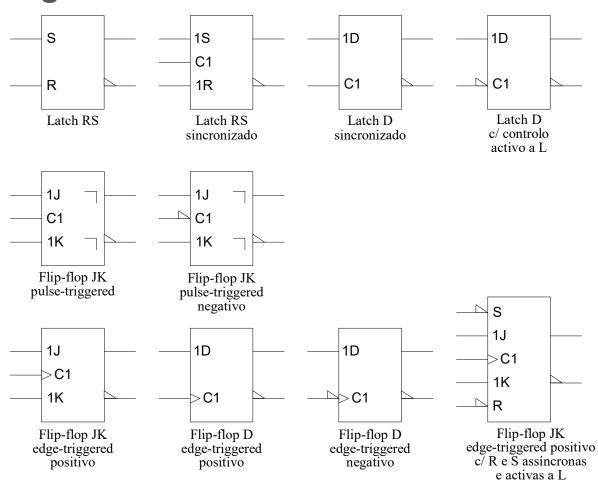

Os circuitos básicos de memória podem ser classificados em latches e flip-flops.

#### Latches:

- Se a entrada de activação (enable) de um latch sincronizado estiver ligada ao sinal de relógio, o seu estado está continuamente a ser actualizado enquanto o relógio estiver a 1.

- Como não é possível garantir que o estado dos latches se mantem estável durante a fase em que o sinal de relógio estiver a 1, não é também possível garantir que todos os latches mudem sincronamente num circuito complexo.

- Os latches têm aplicações muito específicas (menos complexos, mais rápidos), nomeadamente em <u>circuitos assíncronos</u>.

### Circuitos Síncronos

#### Latches vs. Flip-Flops

Os circuitos básicos de memória podem ser classificados em latches e flip-flops.

#### Flip-Flops:

- Os flip-flops mudam as saídas apenas quando há uma variação do relógio (diz-se que são sensíveis ao <u>flanco</u>).

- Este modo de funcionamento garante que o seu estado só é alterado uma única vez em cada período de relógio.

- Esta característica permite que se utilize quase todo o período de relógio para geração de novos valores nas entradas.

- Os <u>circuitos síncronos</u> utilizam, na grande maioria dos casos, flip-flops (sensíveis ao flanco).

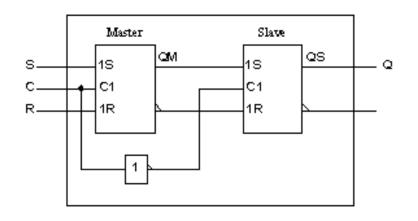

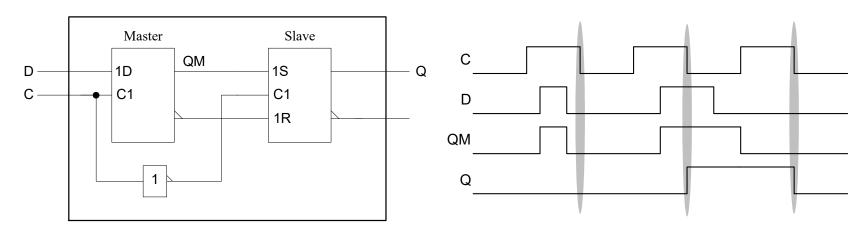

#### Flip-Flop Master-Slave

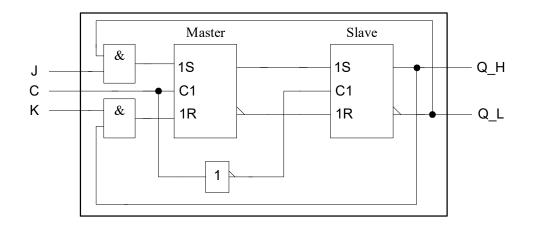

- ▶ O flip-flop Master-Slave consiste na ligação em cascata de 2 latches sincronizados, com sinais de controlo complementares.

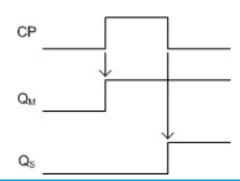

- ► Funcionamento: o mestre "aceita" ordens de Set ou Reset enquanto C = 1, mas só "passa" a ordem ao escravo quando C = 0;

- ▶ Do ponto de vista das saídas externas o estado apenas muda após a transição de 1 → 0 do relógio.

#### Exemplo: S=1 R=0

#### Caso Particular: Flip-Flop JK Master-Slave

▶ O flip-flop JK permite eliminar o estado indefinido, mantendo 2 entradas e, portanto, 4 funcionalidades distintas.

| J | K | Q <sub>n+1</sub> |        |

|---|---|------------------|--------|

| 0 | 0 | $Q_n$            | HOLD   |

| 0 | 1 | 0                | RESET  |

| 1 | 0 | 1                | SET    |

| 1 | 1 | $\overline{Q_n}$ | TOGGLE |

**Nota:** continua a só existir mudança de estado (variação nas saídas) após a transição de relógio de  $1 \rightarrow 0$ .

#### Flip-Flops Master-Slave

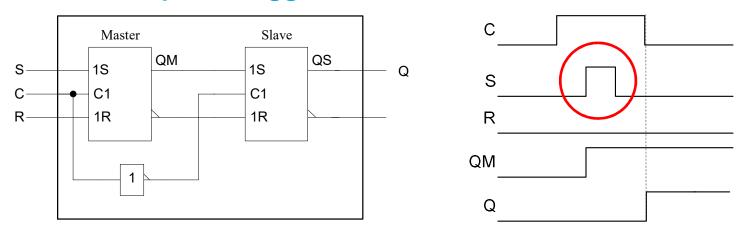

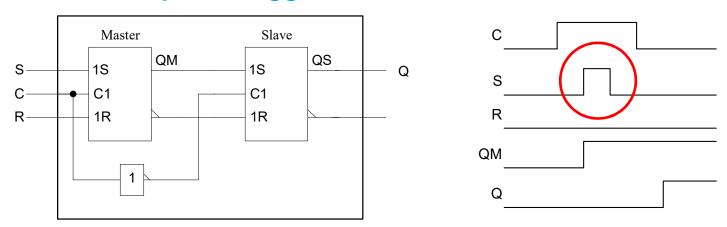

➤ Os flip-flops master-slave respondem aos valores na entrada que existam durante o semi-período em que C = 1. Por isso, são também chamados de pulse-triggered.

▶ No entanto, para o seu funcionamento correcto, não devem ser permitidas variações nas entradas durante o pulso de relógio.

#### Flip-Flops Master-Slave

▶ Os flip-flops master-slave respondem aos valores na entrada que existam durante o semi-período em que C = 1. Por isso, são também chamados de pulse-triggered.

Problema: se durante o pulso de relógio R = 0 e S = 0 → 1 → 0, esperar-se-ia que o flip-flop mantivesse o estado, pois a última ordem é de HOLD. No entanto, o Mestre respondeu à ordem de SET e é essa ordem que é passada ao Escravo.

#### Flip-Flops Edge-Triggered

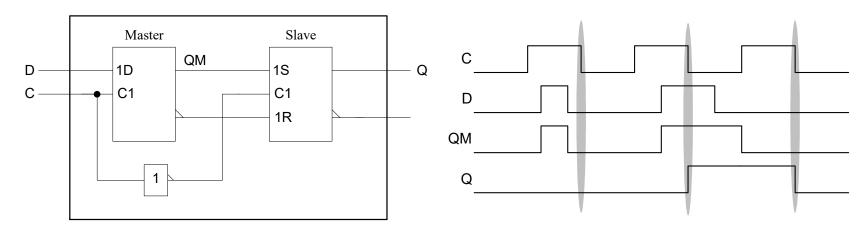

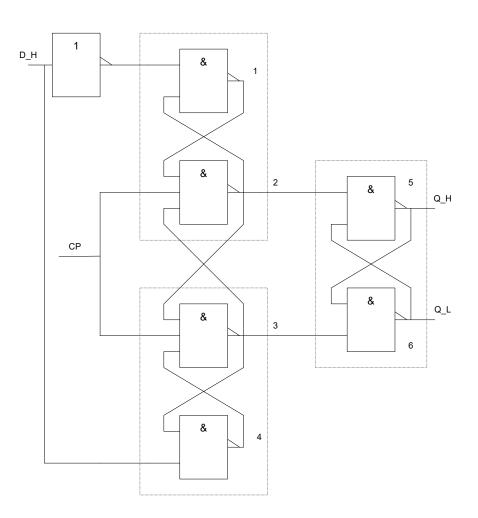

- ➤ Os flip-flops edge-triggered ignoram o pulso enquanto este se mantém num valor constante, e apenas reagem à transição de relógio.

- ▶ Uma estrutura tipo master-slave em que o Mestre é um flip-flop D funciona como edge-triggered (e não como pulse-triggered): o estado que é passado do Mestre para o Escravo é sempre o estado definido pelas entradas na transição de relógio.

#### Flip-Flops Edge-Triggered

- ➤ Os flip-flops dizem-se positive-edge-triggered se reagem à transição de relógio 0 → 1.

- ➤ Os flip-flops dizem-se negative-edge-triggered se reagem à transição de relógio 1 → 0.

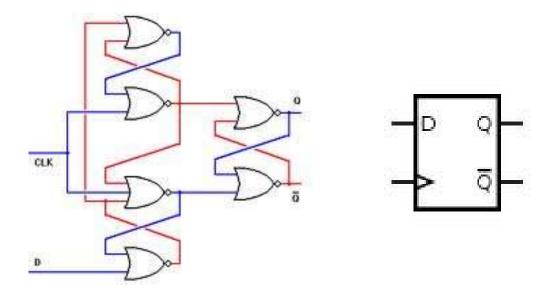

### Flip-Flop D Edge-Triggered

Os flip-flops D positive-edgetriggered são habitualmente realizados com o circuito ao lado.

| CP | D_H      | $Q_{n+1}$ |

|----|----------|-----------|

|    | L        | L         |

|    | Н        | Н         |

|    | -        | Qn        |

| L  | <b>-</b> | Qn        |

| Н  | _        | Qn        |

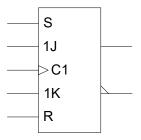

#### Entradas Assíncronas

- ► Alguns flip-flops incluem entradas adicionais que permitem fazer o SET ou o RESET <u>assíncronamente</u>, i.e., independentemente do relógio.

- ▶ A entrada de **set assíncrono** é também às vezes designada por "direct set" ou "preset", e a entrada de **reset assíncrono** é também às vezes designada por "direct reset" ou "clear".

#### Exemplo:

Flip-flop JK com R e S assíncronos

| S | R | С          | J | K | Q <sub>n+1</sub> |            |

|---|---|------------|---|---|------------------|------------|

| 0 | 0 | $\uparrow$ | 0 | 0 | Q <sub>n</sub>   | HOLD       |

| 0 | 0 | $\uparrow$ | 0 | 1 | 0                | RESET      |

| 0 | 0 | $\uparrow$ | 1 | 0 | 1                | SET        |

| 0 | 0 | $\uparrow$ | 1 | 1 | $\overline{Q}_n$ | TOGGLE     |

| 1 | 0 | X          | Χ | Χ | 1                | SET        |

| 0 | 1 | X          | Χ | Χ | 0                | RESET      |

| 1 | 1 | X          | Χ | Χ | U                | Indefinido |

|   |   |            |   |   |                  |            |

# Latches e Flip-Flops

#### Simbologia

### **Próxima Aula**

#### Tema da Próxima Aula:

- ▶ Caracterização temporal

- ► Metodologia de sincronização temporal

### **Agradecimentos**

Algumas páginas desta apresentação resultam da compilação de várias contribuições produzidas por:

- Nuno Roma

- Guilherme Arroz

- Horácio Neto

- Nuno Horta

- Pedro Tomás