### **Synthesis of Network Switch Programs**

### Francisco Chan Carvalho Machado

Thesis to obtain the Master of Science Degree in

### **Telecommunications and Informatics**

Supervisors: Prof. Fernando Manuel Valente Ramos Prof. Luís David Figueiredo Mascarenhas Moreira Pedrosa

### **Examination Committee**

Chairperson: Prof. Ricardo Jorge Fernandes Chaves Supervisor: Prof. Fernando Manuel Valente Ramos Member of the Committee: Prof. Maria Inês Camarate de Campos Lynce de Faria

June 2022

# **Acknowledgments**

First and foremost, I want to thank my parents and brothers for their never ending encouragement and support. I'd like to express my gratitude to my girlfriend Barbara for always believing in me. To all of my family and friends, I couldn't do it without you, thank you from the bottom of my heart. I'd also like to thank Prof. Luís Pedrosa and Prof. Fernando Ramos for their guidance and supervision, as well as my colleagues João Tiago and Francisco Pereira for all of their help and advice.

# Abstract

The emergence of programmable network hardware devices allowed engineers to deploy Network Functions that perform orders of magnitude faster than previous programmed software NFs. The improved performance of these devices comes at the expense of increasing programming complexity, which requires a thorough understanding of the underlying pipeline and hardware details. Some recent domainspecific languages, such as P4, have tried to optimize network packet forwarding by providing additional constructs and externs. However, the task of programming hardware devices still remains associated with steep learning curves and their integration in networks is limited to specialized engineers.

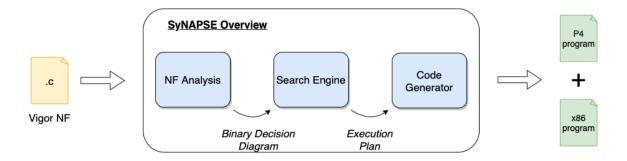

The state-of-the-art solutions address this challenge by means of rule-based approaches, often used in compiler design, to automatically generate code for these network devices. In this thesis we follow a different approach. We developed SyNAPSE, a program synthesis-based technique that leverages static analysis tools to generate NF implementations in P4 that are semantically equivalent to the original NF code. Our prototype reduces the effort required to program network devices by generating NF implementations for a P4 software switch and a standard x86 controller from NFs that were written in the well-known programming language C.

## **Keywords**

Network Functions; Program Synthesis; Network Function Synthesis; Data Plane Programmability; P4;

# Resumo

Na última década, foram introduzidos dois paradigmas que tiveram um grande impacto na indústria de redes: as Redes Definidas por Software (SDN) e a virtualização de Funções de Rede (NFV). Estes novos paradigmas introduziram um certo grau de programabilidade, aumentaram a flexibilidade e agilizaram a operação das redes. No plano de dados, em particular, o paradigma NFV permite correr funções de rede em software. As vantagens ao nível da flexibilidade trazem consigo o desafio do desempenho. Entretanto, a evolução nas arquiteturas de *chips* de redes resultaram em dispositivos de hardware programáveis com velocidades de processamento ordens de grandeza superiores às funções de rede virtualizadas. Em contrapartida, estes dispositivos estão associados a linguagens de programação de baixo-nível, e a sua introdução na infrastrutura exige por isso engenheiros de redes altamente especializados.

Como solução para este desafio, investigação recente propôs mecanismos de tradução baseados em regras, semelhantes aos usadas em compiladores, para este contexto. Neste tese propomos uma abordagem diferente: a utilização de técnicas de síntese de programas para sintetizar código para estes dispositivos de redes programáveis, com o intuito de reduzir a sua acentuada curva de aprendizagem. Com base nestas ideias, desenvolvemos o SyNAPSE, um protótipo que gera implementações de NFs para um switch P4 em software e para um controlador x86, a partir de NFs programadas em C. O protótipo aplica técnicas de síntese a partir de representações obtidas através de execução simbólica.

# **Palavras Chave**

Funções de Rede; Síntese de Funções de Rede; Programação do plano de dados; P4;

# Contents

| 1 Introduction |      |                                  |    |   |

|----------------|------|----------------------------------|----|---|

|                | 1.1  | Motivation                       |    | , |

|                | 1.2  | Contributions                    |    | i |

|                | 1.3  | Organization                     |    |   |

| 2              | Rela | ated work                        | 5  | j |

|                | 2.1  | Software-Defined Networking      |    | , |

|                |      | 2.1.1 Data Plane Programmability |    | i |

|                |      | 2.1.2 P4 Language                |    | I |

|                | 2.2  | Network Function Virtualization  |    | I |

|                |      | 2.2.1 Architectures              |    | , |

|                | 2.3  | Vigor as an Analysis Framework   |    | i |

|                | 2.4  | Program Synthesis                |    |   |

|                |      | 2.4.1 Programming by Example     |    | ) |

|                |      | 2.4.2 Sketch                     |    | i |

|                | 2.5  | Network Synthesis                | 17 | , |

|                |      | 2.5.1 Configuration Synthesis    |    | , |

|                |      | 2.5.2 SDN Synthesis              |    | 1 |

|                |      | 2.5.3 Network Function Synthesis |    |   |

|                |      | 2.5.4 Network Program Synthesis  |    | ; |

|                | 2.6  | Summary                          |    | j |

| 3              | Arch | chitecture                       | 29 | ) |

|                | 3.1  | Overview                         |    | ) |

|                | 3.2  | SyNAPSE in Detail                |    |   |

|                |      | 3.2.1 Vigor Data Structures      |    |   |

|                |      | 3.2.2 Running Example            |    | , |

|                | 3.3  | Network Function Analysis        |    | ; |

|                |      | 3.3.1 Call Paths                 |    | 5 |

|     | 3.3.2 Binary Decision Diagrams                                                                                                                   | 35                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

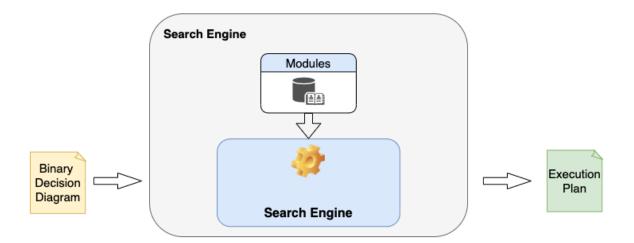

| 3.4 | Search Engine                                                                                                                                    | 37                                   |

|     | 3.4.1 Search Space Algorithm                                                                                                                     | 38                                   |

|     | 3.4.2 Implementation Details                                                                                                                     | 39                                   |

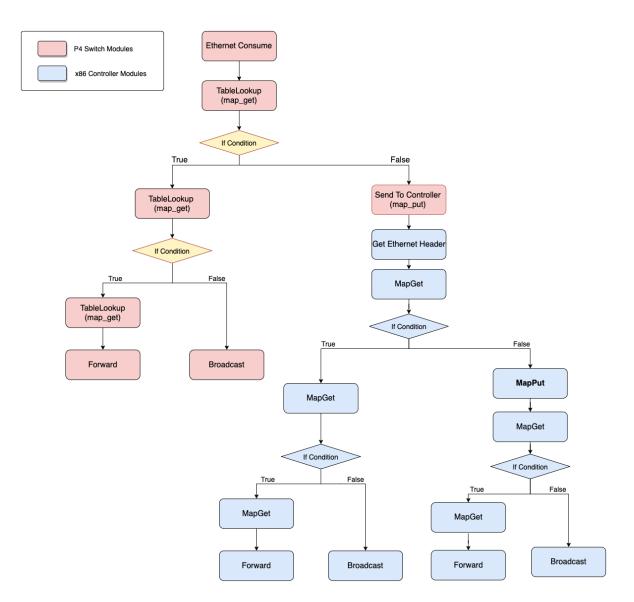

|     | 3.4.3 Running Example                                                                                                                            | 40                                   |

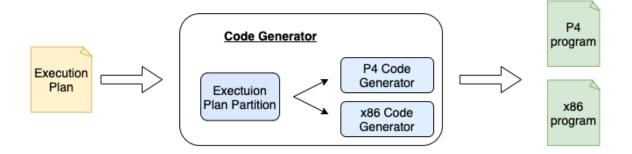

| 3.5 | Code Generator                                                                                                                                   | 43                                   |

|     | 3.5.1 Implementation Details                                                                                                                     | 43                                   |

| 3.6 | Summary                                                                                                                                          | 45                                   |

|     | 3.6.1 Contribution                                                                                                                               | 46                                   |

| Eva | Jation                                                                                                                                           | 47                                   |

| 4.1 | NF Description                                                                                                                                   | 48                                   |

| 4.2 | Benchmarking methodology                                                                                                                         | 49                                   |

| 4.3 | Performance Benchmarking                                                                                                                         | 50                                   |

| 4.4 | Discussion                                                                                                                                       | 53                                   |

| Con | clusion                                                                                                                                          | 63                                   |

| 5.1 | Conclusions                                                                                                                                      | 64                                   |

|     |                                                                                                                                                  |                                      |

|     | <ul> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>Evalu</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Conce</li> <li>5.1</li> </ul> | <ul> <li>3.4 Search Engine</li></ul> |

# **List of Figures**

| 2.1 | Simplified view of an SDN architecture.                                                     | 8  |

|-----|---------------------------------------------------------------------------------------------|----|

| 2.2 | Programmable blocks of the Portable Switch Architecture                                     | 9  |

| 2.3 | Illustrative example of Configuration Synthesis tools.                                      | 18 |

| 2.4 | Illustrative example of SDN Synthesis tools.                                                | 20 |

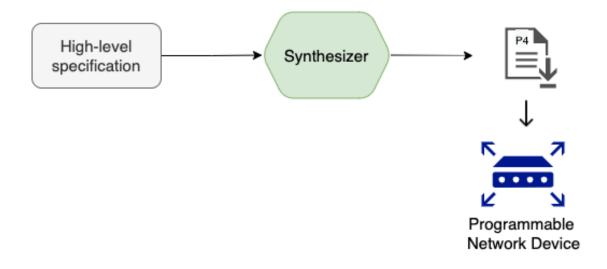

| 2.5 | Illustrative example of Network Program Synthesis tools                                     | 26 |

| 3.1 | SyNAPSE architecture.                                                                       | 30 |

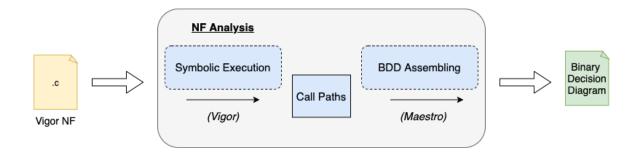

| 3.2 | NF Analysis Module architecture                                                             | 33 |

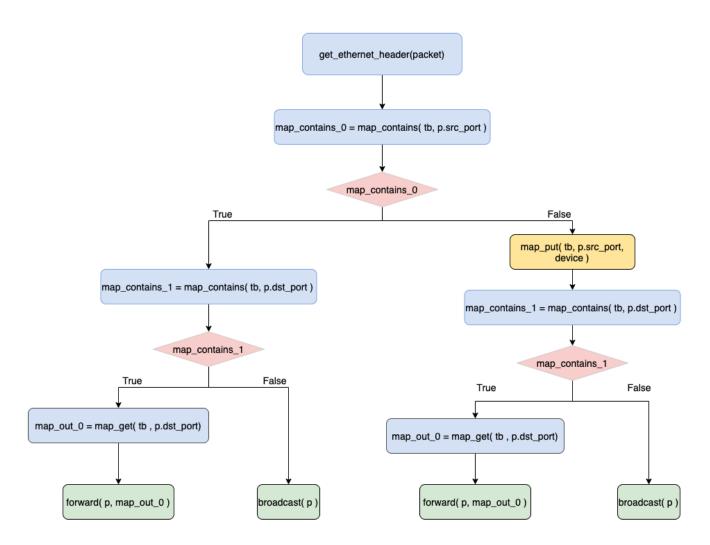

| 3.3 | Generated binary decision tree for the call paths in listing 3.2                            | 36 |

| 3.4 | Search Engine Module architecture.                                                          | 37 |

| 3.5 | Resulting Execution Plan for the Running Example                                            | 42 |

| 3.6 | Code Generator Module architecture.                                                         | 42 |

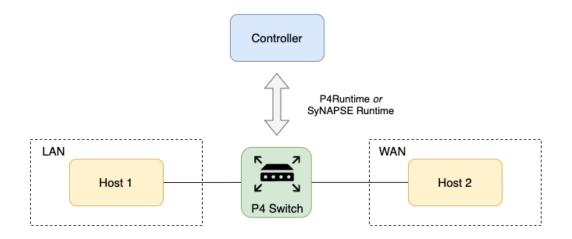

| 4.1 | Simplified view of the network topology.                                                    | 51 |

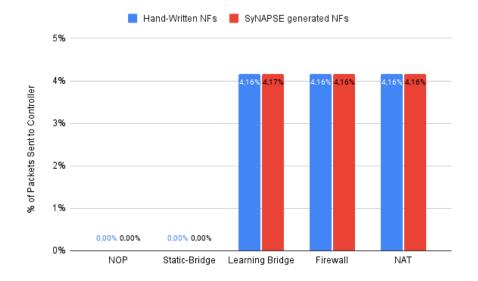

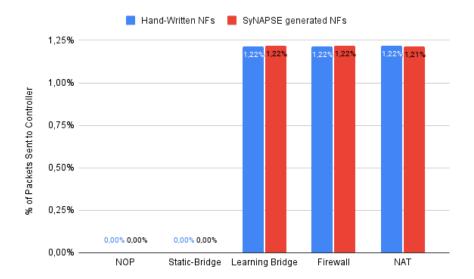

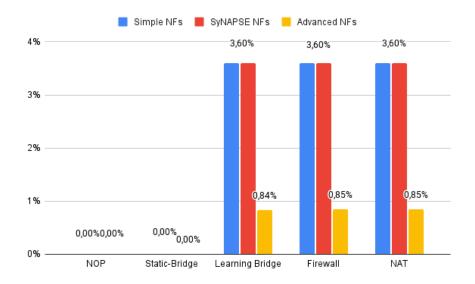

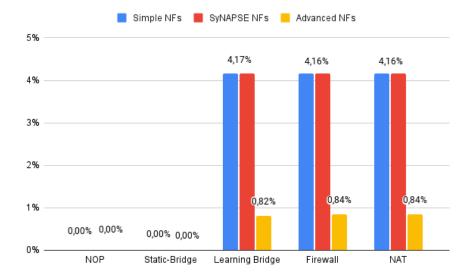

| 4.2 | Comparison of the percentage of packets sent to the controller for all NFs, with a 15       |    |

|     | second expiration time and 1 million packet with Uniform distribution                       | 54 |

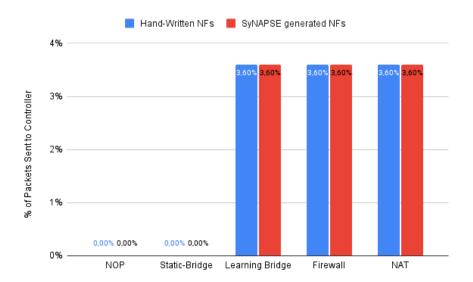

| 4.3 | Comparison of the percentage of packets sent to the controller for all NFs, with a 45       |    |

|     | second expiration time and 1 million packet with Uniform distribution                       | 54 |

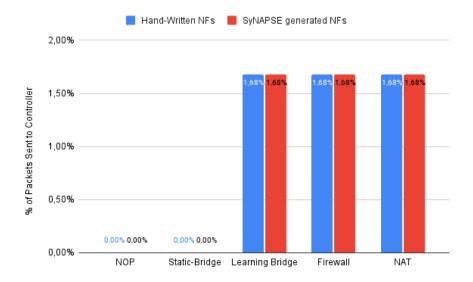

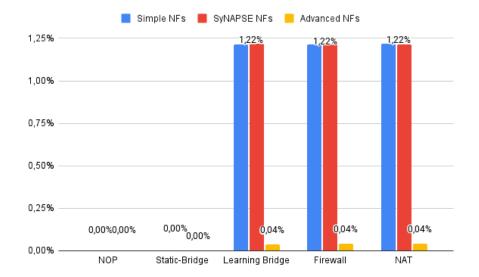

| 4.4 | Comparison of the percentage of packets sent to the controller for all NFs, with a 15       |    |

|     | second expiration time and 1 million packet with Zipfian distribution.                      | 55 |

| 4.5 | Comparison of the percentage of packets sent to the controller for all NFs, with a 45       |    |

|     | second expiration time and 1 million packet with Zipfian distribution.                      | 55 |

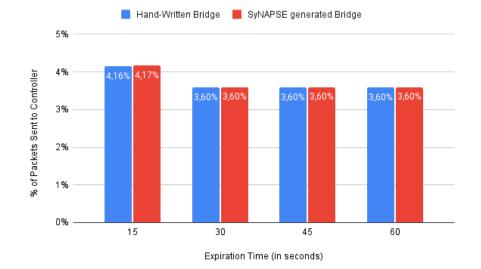

| 4.6 | Percentage of packets sent to the controller for different expiration times in the Learning |    |

|     | Bridge NF (1 Million packets with a Uniform Distribution).                                  | 56 |

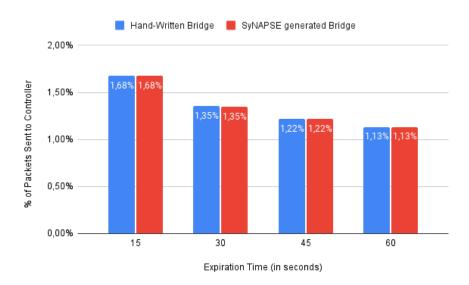

| 4.7 | Percentage of packets sent to the controller for different expiration times in the Learning |    |

|     | Bridge NF (1 Million packets with a Zipfian Distribution).                                  | 56 |

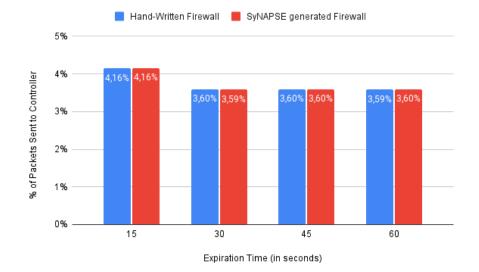

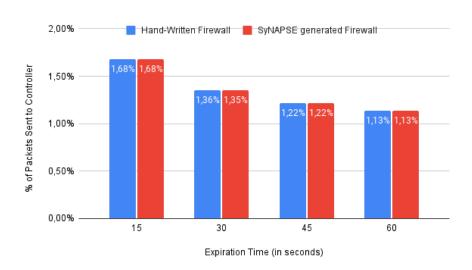

| 4.8  | Percentage of packets sent to the controller for different expiration times in the Firewall  |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | NF (1 Million packets with a Uniform Distribution)                                           | 57 |

| 4.9  | Percentage of packets sent to the controller for different expiration times in the Firewall  |    |

|      | NF (1 Million packets with a Zipfian Distribution).                                          | 57 |

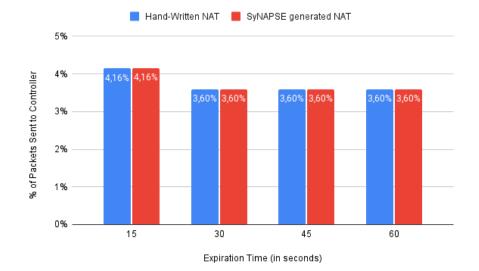

| 4.10 | Percentage of packets sent to the controller for different expiration times in the NAT NF (1 |    |

|      | Million packets with a Uniform Distribution).                                                | 58 |

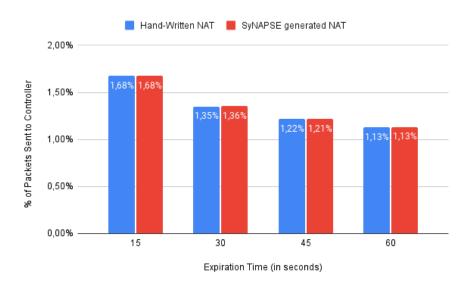

| 4.11 | Percentage of packets sent to the controller for different expiration times in the NAT NF (1 |    |

|      | Million packets with a Zipfian Distribution)                                                 | 58 |

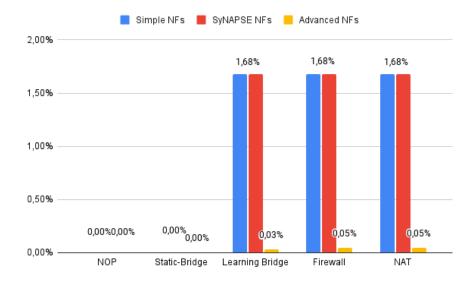

| 4.12 | 45 second expiration time and Uniform distribution                                           | 60 |

| 4.13 | 15 second expiration time and Uniform distribution                                           | 61 |

| 4.14 | 45 second expiration time and Zipfian distribution.                                          | 61 |

| 4.15 | 15 second expiration time and Zipfian distribution.                                          | 62 |

# **List of Tables**

| 2.1 | Comparative Table for all Related Tools.                                         | 28 |

|-----|----------------------------------------------------------------------------------|----|

| 4.1 | Comparing throughput estimation for SyNAPSE NFs and the Maestro NFs              | 53 |

| 4.2 | Comparing throughput estimation for simple and advanced SyNAPSE NFs and the Mae- |    |

|     | stro NFs                                                                         | 60 |

# Listings

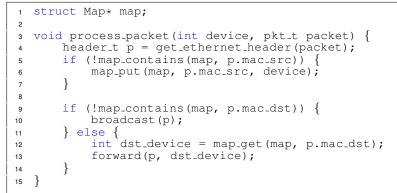

| 3.1 | Pseudo-code of vigbridge                                                  | 33 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | Call paths generated for the example NF by the symbolic execution engine. | 34 |

# Acronyms

| ASICs | Application-Specific Integrated Circuit            |

|-------|----------------------------------------------------|

| CEGIS | Counterexample Guided Inductive Synthesis          |

| CPU   | Central Processing Unit                            |

| DPDK  | Data Plane Development Kit                         |

| FPGAs | Field-programmable Gate Array                      |

| LAN   | Local Area Network                                 |

| ML    | Machine Learning                                   |

| NAT   | Network Address Translator                         |

| NF    | Network Function                                   |

| NFV   | Network Function Virtualization                    |

| NIC   | Network Interface Card                             |

| NIDS  | Network Intrusion Detection System                 |

| NPUs  | Network Processing Units                           |

| NUMA  | Non-Uniform Memory Access                          |

| P4    | Programming Protocol-Independent Packet Processors |

| PISA  | Protocol Independent Switch Architecture           |

| PSA   | Protocol Switch Architecture                       |

| SDN   | Software Defined Networks                          |

| ТСР   | Transmission Control Protocol                      |

- VM Virtual Machine

- **VPN** Virtual Private Network

- WAN Wide Area Network

# Introduction

### Contents

| 1.1 | Motivation    | 2 |

|-----|---------------|---|

| 1.2 | Contributions | 3 |

| 1.3 | Organization  | 4 |

The latest advances in the networking industry have contributed to an era of unseen innovation and development. Similarly to the computing industry, the networking sector has traditionally been dependent on vendors to supply network products, or middleboxes, specifically designed to address specific problems other than traffic forwarding, such as security and performance. The substantial demand for these products paired with their inflexible deployment has resulted in massive costs to network operators. These constraints led to difficulties scaling networks as adding new middleboxes to already extremely complex network infrastructure required a lot of effort: complying with the established network policies, optimizations and quality-of-service requirements. These difficulties, which were more evident as networks grew in size, motivated paradigms that tried to tackle issues that were stifling innovation.

Software-Defined Networking (SDN) [1] was developed to address management issues by decoupling traffic forwarding (the data plane) from routing logic and network management (control plane). SDN also introduced network programmability by allowing the network control plane to be logically centralized on a software controller. SDN motivated the development of Network Function Virtualisation (NFV) [2]. NFV enabled developers to provide middlebox functionality previously performed by specialised network devices by using general-purpose commodity servers to run software Network Functions (NFs).

With the adoption of these new network paradigms, by decoupling the NFs from the hardware and the control plane from the data plane, the installation of fixed-function hardware middleboxes across the network was considerably reduced. This translated in a decrease of the overall network complexity and largely contributed to a more efficient and flexible deployment of NFs granting some degree of abstraction to program network devices.

SDN introduced a new approach to determine the forwarding behavior of packets processed by the hardware. Flow rules allowed for programmers to decide which packet-processing actions would be applied to packets that would match the designated match fields. In the early stages of SDN, the rigid switch designs only accepted matching a fixed set header fields. However, the available packet-processing actions and the header fields have progressively increased to more general hardware designs. Nowadays, data plane packet processing can be programmable in hardware, and still guarantee line rate processing. This data plane programmability has emerged as another alternative to the inflexible middleboxes, allowing NFs to be programmed and compiled to programmable networking hardware capable of running at Terabit speeds.

### 1.1 Motivation

Unfortunately, programming network devices and their multi-stage forwarding pipelines can involve a lot of effort and time. Programs have to consider all the available resources and the forwarding pipeline limitations in order to run at line-rate [3]. These devices are usually associated with low-level chip-specific languages, with inconvenient learning curves. For example, optimizing linear-rate programs requires a deep knowledge of the underlying hardware constraints to take full advantage of all their capabilities. Some domain-specific language (DSL) languages, such as the P4 language [4], offers a way to program these switches, allowing to specify how packets are processed in the data plane. P4 programs are designed to be target-independent as they can be compiled against a wide range of forwarding elements, including hardware or software switches, network interface cards, and programmable network appliances. Despite enabling data plane programmability, P4 does not make it easy the task of programming the device. Programming in this language requires specialized knowledge of the target architecture, in order to guarantee line rate processing of packets.

When expanding and scaling networks, developers are therefore faced with the decision of whether to use software NFs, which provide greater flexibility and familiarity, or programmable hardware, which offers improved packet-processing speeds but is more difficult to program and optimize according to network constraints. If a network developer chose the latter, building a network function would take far more time and effort than implementing the NF in software using a more familiar programming language. Additionally, developers must consider the effort that programmable network hardware will require to optimize whenever network alterations are required.

In recent years, some tools have shown success in generating network-wide *configurations* utilizing program synthesis techniques (i.e., to program the *control* plane). Following on from these ideas, in this thesis we suggest to address the complexity of programming these intricate hardware devices by also following a program synthesis approach, but for the network *data plane*. Contrary to the state-of-the-art approach [5] that uses rule-based techniques, a program-synthesis solution can consider a larger search space of solution, potentially enabling the generation of packet-processing code that is faster and better optimized to the considered architecture. However, using program synthesis techniques instead of traditional compiler techniques has one main disadvantage: finding programs that fit the specified hardware constraints without sacrificing performance can lead to increased compile time, as this process is a complex combinations problem and the search space can grow exponentially with the program size. The challenge is therefore to develop domain-specific heuristics that prune and optimize the search space.

### 1.2 Contributions

This thesis adds to the state-of-the-art by proposing SyNAPSE. SyNAPSE is a tool that is able to generate new implementations of NFs that were originally written in C (using the Vigor [6] libraries), into semantically equivalent NFs that offload packet-processing to a P4-programmable software switch and to a x86 SDN controller. The prototype incorporates two previously existing tools, Vigor and Maestro, which perform static analysis of software NFs. It receives as input a network function programmed in C language in the context of Vigor – a software-verification framework. The Vigor framework explores the use of symbolic analysis to check NF behavior against a specifications for correctness. These static analysis methods are then used by Maestro to build a sound and complete representation of the NF behaviour. Maestro is used to automatically parallelize sequential implementations of NFs, by distributing traffic across CPU cores while preserving the semantics of the sequential implementation. We adopt the model of the NF behaviour of Maestro to obtain an intermediate representation of the NF, from which we are able to generate code for both the P4 switch and the SDN controller, resulting in a semantically equivalent NF to the original NF.

Our prototype allows network developers to write NFs in a language they are more familiarized with, thus reducing the time and effort required to deploy NFs directly in P4.

### 1.3 Organization

The remainder of this dissertation is divided into four chapters.

In the following chapter, we analyze the state-of-the-art in Software-Defined Networks, Network Function Virtualization, and Data Plane Programmability. We will investigate the motivation for program synthesis and some existing frameworks and tools. Additionally, we present the two tools on which this prototype builds on, namely Vigor and Maestro. Then, Chapter 3 explains the design and implementation of the SyNAPSE prototype, and how it generates new implementations of NFs. This prototype can be described as a sequential set of three modules that continuously modify the initial input until the generated code is obtained. In Chapter 4, we evaluate the prototype, and in chapter 5 we conclude and discuss future work.

# 2

# **Related work**

### Contents

| 2.1 | Software-Defined Networking 7   |

|-----|---------------------------------|

| 2.2 | Network Function Virtualization |

| 2.3 | Vigor as an Analysis Framework  |

| 2.4 | Program Synthesis               |

| 2.5 | Network Synthesis               |

| 2.6 | Summary                         |

In this chapter, we start by presenting some backgorund information on Network Function Virtualization and Software Defined Networks. We then introduce program synthesis and verification, and present state-of-the-art solutions that apply these techniques in the context of computer networks.

### 2.1 Software-Defined Networking

Computer networks are complex systems of interconnected nodes that can be arranged in a variety of topologies and subjected to many requirements. In the past years, cloud datacenters and service providers have seen increasing complexity in their network infrastructures and policies. The number of network elements in infrastructure ramped up with the emergence of dedicated hardware to implement specific network functions, such as firewalls, network address translators (NAT) and intrusion detection systems (IDS). To comply with these standards, datacenter objectives include optimizing performance while coping with continuous network link failures, all while maintaining security and quality-of-service requirements [7]. As a result, network implementation and subsequent maintenance have become more difficult, requiring highly qualified and specialized engineers, resulting in high operational expenses.

SDN emerged as a solution to this overwhelming problem, enabling efficient network configuration and providing network programmability by allowing the network control plane to be logically centralized on a software controller. By decoupling traffic forwarding (the data plane) from routing logic and network management, SDN technology seeks to simplify network design, implementation, and management (control plane). The data plane is responsible for processing all incoming packets according to basic rules. A controller establishes these rules depending on network architecture and global network policy goals. These rules are encoded in forwarding tables populated by the control plane and usually processed at very high requirements [8].

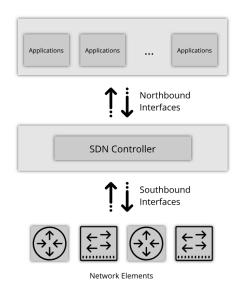

In SDN, control logic is moved to an external entity called the SDN controller, a logically centralized system to manage and control all resources available represented by one or multiple controller instances. Three main elements can be distinguished (Figure 2.1): the controller, and its southbound and northbound APIs. Controllers serve as an intermediate component between the network control applications and the data plane. Applications can program the network by defining a set of functions and services through a northbound API, which subsequently interacts with underlying network services using the southbound API. The controller also collects network information, such as state of the resources or changes in topology, to continuously adapt network configurations according to desired policies.

In SDN, forwarding decisions are flow-based instead of destination-based [1]. Flows are an abstraction that group traffic by matching a set of packet fields to a set of actions, unifying behaviour of multiple network devices, like switches, routers, and other middleboxes. This abstraction increases flexibility for network programmers. This concept was introduced by OpenFlow [9] with *flow rules* that defined forwarding behaviours and an interface for controlling the data plane. A flow rule comprises match fields,

Figure 2.1: Simplified view of an SDN architecture.

counters and set of instructions. Packets are compared against specific patterns and if a match occurs packets will follow through with the configured action. These actions can include for example, dropping, forwarding to one or multiple ports, changing the packet headers and sending the packet to the controller for further processing. In the latter case, the controller can subsequently generate new flow rules and send them to the switch. Each network element in the network maintains a Flow Table with all the controller defined rules. In OpenFlow 1.1, the Flow table abstraction was refined with the adoption of chaining multiple flow tables, where flow entries point to another tables flow entry.

Another defining feature was the OpenFlow protocol which allowed the secure transmission of flow rules from the controller to the switch. The first implementations of SDNs didn't get much attention from the network community, however, the introduction of OpenFlow in 2008 gained significant traction and resulted in the creation of the Open Networking Foundation (ONF) in 2011, to promote SDN and OpenFlow. Since then SDN has seen wide adoption and multiple APIs and Controllers have been developed.

### 2.1.1 Data Plane Programmability

OpenFlow introduced new abstractions and the possibility of programming the network control plane but the technology was limited to match previously determined header fields and to chip-specific capabilities. In the following years, new switching chip architectures contributed to the increased flexibility while maintaining processing speeds required for deployment in networks. For example, the Reconfigurable Match Table [3] (RMT) model allowed the forwarding plane to be changed in the field without modifying the hardware, and the Protocol Independent Switch Architecture (PISA), an architecture that allows

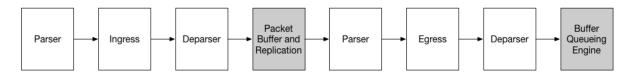

Figure 2.2: Programmable blocks of the Portable Switch Architecture.

forwarding pipelines to be programmed by high-level languages, such as P4 [4]. The possibility of programming functionality onto data plane resulted in a turning point for how ASICs (Application-Specific Integrated Circuit), and network devices overall, were developed.

The general approach to implement new functionalities onto fixed-function ASICs, followed a topdown design: New functionality had to be first standardized according to clients needs. Then the new design would have to be implemented in ASICs by chip designers. The complete process was slow hurting flexibility and hindering innovation [8]. The emergence of programmable network data planes allowed network engineers to dictate exactly how each packet should be processed. Directly programming the forwarding pipeline to implement new functionalities became a task operators could perform without depending on vendors, leading to rapid design cycles and quick innovation.

### 2.1.2 P4 Language

The P4 programming language was presented in 2014 [4] as a proposal for how OpenFlow "should evolve in the future". A revision to the P4 language was released in 2016, resulting in the P4<sub>16</sub> language specification [10]. P4 is a domain-specific language (DSL) to program forwarding planes. This DSL is protocol-independent, as it allows developers to specify the structures of the packet headers and how they are extracted and processed, and target independent as it supports multiple hardware architectures. P4 uses a compiler to map target hardware resources to the target-independent description, generating the necessary configurations [4].

P4 programs specify the behaviour of the programmable blocks of a given architecture. For example, the Portable Switch Architecture (PSA) Model [11] is composed of two pipelines: ingress pipeline (composed of a parser, ingress, deparser and a Packet buffer and Replication Engine (PRE)) and an egress pipeline (composed of a parser, egress, and Buffer Queuing Engine (BQE)). Packets traverse the pipeline in the order specified in 2.2. The P4 programmable parser enables user defined packet headers according to implementation needs. The main logic of the P4 program is defined in the ingress/egress blocks. In these blocks, the programmer can implement custom actions and define match-action tables with different combinations of matching entries, matching types and associated actions. Finally, the user can use these actions and/or tables freely, for example, depending on the parsed packet header elements. Besides defining packet processing throughout the pipeline, the architecture also defines a set

of P4 externs that extend P4 functionality, for example, counters, meters and registers which allow to maintain state between packets.

Similar to OpenFlow 1.1, pipelines are composed of multiple match+action stages, except in P4 they can be processed in parallel. To address dependencies between headers Table Dependency Graphs (TDGs) are used. This process is performed by the P4 compiler to identify possible conflicts before mapping match+action tables to their location in the pipeline. After being validated in the parser, packet headers are passed to an ingress match-action pipeline determining operations to be applied to each packet. The ingress deparser identifies which packet contents and metadata are sent to the buffer. Buffers are not part of the P4 architecture and are used to place packets waiting for their respective actions, reducing congestion. Metadata fields can carry information that are not contained in packet headers but are relevant to execution, for example, timestamps used for some traffic shaping policy. Both metadata and packet headers can be used as match fields in match+action tables and are processed in equal manner. Packets can be forwarded to one or to multiple egress ports (multicast), dropped or placed in queues where traffic shaping policies are applied. In the multicast case, the packet is replicated the necessary number of times before being sent to the PRE, where they are placed in a buffer and processed when possible. The PSA also allows for packets to be recirculated or resubmitted. In this case, they are sent to the beginning of the pipeline. PSA also defines a library of commonly used constructs, called externs. Externs allow P4 code to be extended with new constructs not supported by the language but made available by the target platform.

To summarize, SDN enhanced flexibility enabling a logically centralized control plane to manage network devices from different vendors and with diverse characteristics. Data plane programmability enabled new functionality to be implemented faster and more efficient usage of hardware resources. This trade-off between programmability and hardware performance made SDN a trending technology since it first appeared. SDN has seen wide adoption across data centers, Wide Area Networks (WANs) and access networks and has complemented, together with P4, the development of technologies such as Intent-Based Networking and In-Band Network Telemetry.

### 2.2 Network Function Virtualization

As mentioned before, the number of network elements in cloud datacenters and service provider networks have increased in order to accommodate more users and services. Users have specific constraints and requirements for their traffic related to security, isolation and quality-of-service, which result in complex policies. This functionality is commonly implemented as Network Functions (NFs) and is often supported by dedicated intermediary hardware, also known as "middleboxes," which increase forwarding efficiency by decoupling specific network functions from the forwarding plane. To comprehend the impact of the network architecture covered in this section, it's important to understand the market background of networking industry prior to it. Network functions were mostly implemented by proprietary equipment - vertically integrated solutions sold by large companies that developed all underlying technology, from hardware to middlebox operating systems. Thus, a network could demand the deployment of multiple middleboxes in order to offer a given service.

As networks grew in size and complexity, more functionalities were necessary to comply with user requirements and the increasing data line rates. Implementing a new functionality and updating equipment required network administrators to continuously purchase and store new integrated solutions directly to vendors. Scalability was also an issue for large networks, which would require as many middleboxes as forwarding elements [12], and the exponential difficulties in integrating solutions from different vendors in the same network. Combined with the slow-paced approach of producing new equipment mentioned in Section 2.1.1, this model of developing networks where implementing new functions depended on available solutions hindered innovation. All these constraints lead to high Operating Expenses (OPEX) and Capital Expenses (CAPEX) [2]. Telecommunications Service Providers (TSPs) started noticing these increasing costs and were forced to find more dynamic approaches to building and maintaining networks.

Network Function Virtualization (NFV) has been proposed to address the above mentioned challenges offering a new design to deploy services and improving resource management. NFV aims to decouple network functions from the underlying equipment offering more agility to deploy services and better resource management. This technique eliminates the network dependency on specialized hardware to perform network functions. Instead, network functions can be treated as plain software and decomposed in sets of Virtual Network Functions (VNFs) that can be deployed in standard physical servers. Such convenience makes scalability of networks possible and the deployment of services much faster, a task which once required network operators to purchase new equipment and develop appropriate skills to manage and integrate it. With NFV, capital expenses were also reduced as network functions could be deployed in commodity servers.

The concept of NFV was first suggested in October 2012 in a white paper [9]. The paper was the result from collaborative work from leading telecommunications companies calling for industrial and research action. The premise of this work was to decouple functions of proprietary hardware and move them to virtual servers, deployed in a wide range of hardware appliances. High-performance computing could be offloaded to virtual servers, for example, to COTS (Commercial off The Shelf) clusters, benefiting from affordable prices due to economies of scale. Some of the telecommunications companies that worked in the white paper selected ETSI (European Telecommunication Standards Institute) as the responsible entity for the NFV Industry Specification Group (ESTI ISG NFV)

The ETSI NFV framework consists of three main components: Virtualized Network Function (VNF),

VNF Infrastructure (VNFI) and VNF Management and Orchestration (VNF-MANO) [2].

- NFVI corresponds to the environment in which VNFs are deployed. It includes every network element that provides either processing, storage, or connectivity to VNFs, thus including both hardware and software resources. Virtual resources are abstractions from the underlying physical resources, obtained using a virtualization layer.

- VNF is the implementation of network functions deployed on virtual resources. VNFs can be deployed over multiple VMs depending on their internal components.

- 3. NFV MANO is responsible for managing all underlying resources and corresponding virtualised instances, performing operations such as configuring VNFs and any underlying infrastructure.

Although the Network Function Virtualization (NFV) architecture borrows concepts initially proposed in SDN to address challenges imposed by static architectures, no dependency exists between them. While both pretend to implement automation and virtualization, their goal is distinct. NFV main focus is on decoupling NF from specialized hardware whereas SDN separates the network control from packet handling. Nevertheless, leveraging both the network virtualization and logically centralized intelligence - *SDN-based NFV* - can lead to great value as VNFI benefits from having a central orchestration point.

Software-defined NFV can be applied to service-chaining and service deployment replacing timeconsuming complex tasks of installing, connecting hardware to implement new functions or validating and testing network infrastructures. This approach allows maximizing the usage of network resources and reducing the overall costs of providing/adding services.

### 2.2.1 Architectures

The virtualization of NFs and the advances in data plane programmability (Section 2.1.1) have resulted in a wide-range of devices used for general forwarding and performing network functions [8], from general-purpose hardware to hardware designs like ASICs and FPGAs (Field-programmable Gate Array).

**Network Processing Units (NPUs)** are specialized accelerators employed in switches and NICs (Network Interface Cards). They target network packet processing being capable of performing network-specific operations such as load-balancing and encryption. NPUs are optimized to perform parallel computation to process packets from individual network flows and have powerful dedicated memories such as SRAMs (Static Random Memory Access), DRAMs and TCAMs. These memories are organized in a specific manner to aid packet-processing by hosting frequently accessed data and forwarding tables used to determine packet forwarding.

**FPGAs** are integrated circuits based around a matrix of configurable logic blocks and can be reconfigured in the field as per client needs. FPGAs are typically programmed with hardware description languages, like Verilog, but can also, in some cases, be programmed in C or P4.

Additionally, these devices offer high performance, being primarily used to offload packet processing from servers.

**ASICs**, contrary to FPGAs, have more rigid designs, implementing fixed pipelines or processing steps. As a result, they can process packets significantly faster than any alternative, but their programmability is limited. As seen in Section 2.1.1 reconfigurable ASIC architectures have been proposed, for example, RMT [3] and PSA [11] enabling programmability to implement custom network functions and forwarding, with the same performance of their fixed-function counterparts.

**General-purpose Servers** have been deployed at massive scales in datacenters to implement network processing. Traditional NIC interfaces are not optimized for high-performance packet processing, as they are designed to be used in simpler contexts.

In server-based solutions, processing packets requires copying packet's data from NIC buffers to the CPU, where modifications are performed before copying data back to another buffer. This simple series of actions is difficult to implement in general-purpose hardware.

To accelerate network processing in commodity hardware some frameworks have been developed to increase processing rates, including DPDK [13] and Netmap [14]. For example, *zero-copy* [15] uses buffers visible both to applications and the NIC, avoiding costly memory copy operations. *Kernel bypass* gives direct NIC control to userspace processes to avoid system calls and context switching. These techniques avoid copying from kernel buffers and system calls, saving CPU cycles and memory bandwidth. When a packet is transmitted over a network, a sequence of operations must be followed, including the acquisition of locks for the respective queue. Processing packets in batches (groups) reduces the number of necessary lock acquisitions and minimizes system call overhead by reducing the number of PCI-E bus registers.

The integration of SDN and NFV in real networks contributed for increased flexibility allowing companies to easily deploy new services over a broader range of hardware appliances. This translated into an increasing ability to scale the network according to its needs. The minimal dependency of middleboxes impacts greatly their cost. Besides these benefits, running software-based implementations of network functions in commodity hardware lead to the lack of reliability in these software NFs. Frameworks that perform software verification to NFs, such as Vigor, have been developed with the goal of mitigating possible security vulnerabilities and other potential bugs.

### 2.3 Vigor as an Analysis Framework

Vigor [6] is a software stack and toolchain for building and running software network middleboxes with the ability to automatically verify their correctness, while preserving competitive performance and developer productivity. Vigor allows NF developers to write NF code in C on top of the DPDK I/O framework. It uses

libVig, a library of formally verified data structures, to store persistent states across packets. Symbolic execution is performed by the KLEE engine. This technique is used for live code path extraction which is then used to generate Call Paths. Instead of real values, symbolic execution analyses the program simulating the execution with symbolic values. These values are shaped in order to reflect operations and for any given branches presented in the program, the symbolic execution continues the simulation on both paths independently.

Besides verifying NF code correctness, the Vigor verification process includes verification of the entire NF stack to guarantee correctness in its entirety — libraries, packet-processing frameworks, operating system and device drivers. Verifying all these components would be inefficient and lead to path explosion given the complete stack dimensions. As a solution, its authors built a small, custom operating system (NFOS) that can be symbolically executed in an exhaustive manner, and modified both DPDK (in order to make it verifiable) and KLEE - to discard unnecessary paths and to speedup the process [16].

The authors guarantee that NFs are semantically correct, crash-free and memory safe [6] in four steps:

- 1. Obtain all live paths through the code call paths using exhaustive symbolic execution.

- 2. Convert symbolic execution traces to programs, where each one of them represents a path through the stateless code.

- 3. Annotate each trace with lemmas corresponding to the NF specification

- 4. Validate each annotated trace, using the pre- and post-conditions from the libVig API contracts.

Vigor uses symbolic execution to analyse the NF code and generates call paths. Each call path represents a possible execution path and collectively, the call paths generated by Vigor represent the complete behaviour of an NF and show all possible paths through the code triggered by a packet's arrival.

In this thesis, we propose the use of the call paths utilized for NF verification as the initial input to the SyNAPSE prototype. To these complete and sound representation of the NFs behaviour we will later be apply synthesis-based techniques to generate NF implementations.

### 2.4 Program Synthesis

Program synthesis is the task of automatically finding programs that satisfy given high-level formal specifications [17]. The process of finding correct programs constitutes a complex search problem that can be optimized by using different techniques, like complementing the specification with a general structure of the solution (Section 2.4.2) or examples of the program input and respective outputs (Section 2.4.1). The search for correct programs is a hard combinatorial problem because the *search space* of candidate programs grows exponentially with program size, which translates into increased compile time - the main drawback of a program synthesis approach. Synthesizers are characterized by three key dimensions: the kind of constraints that represent user intent, the search space of candidate programs, and the search technique it employs. User intent can appear in forms of logical specification, examples (Section 2.4.1), traces or partial programs (Section 2.4.2). Logical specifications are difficult to express as they declare logical relations for a program's inputs and outputs. A trace is a detailed step-by-step description of programs behaviour according to its inputs, showing how they are transformed.

Because the *search space* should capture a high number of candidate programs whilst maintaining search efficiency, some optimization approaches are capable of pruning it efficiently. We decided to highlight the following approaches:

- Divide-and-conquer, a Deductive search strategy that recursively reduces the search problem into sub-problems. Analyzing smaller parts of the program individually can improve synthesis performance.

- Constraint solving, strategy that usually involves two main steps: constraint generation, where the

applications are able to translate synthesis problems into constraints; and constraint resolution,

where the constraints generated on the previous phase are solved.

### 2.4.1 Programming by Example

Many Program Synthesis implementations explore programming by example (PBE) techniques to infer correct program implementations. In PBE, the specifications given as input to the synthesizer consist in input-output examples. More generally, examples demonstrate behaviours/actions the system should have for different input states. Using examples specifications makes PBE more tractable than other program synthesis approach and are much easier for users to specify [18]. There are three main components in a PBE engine.

- The Search algorithm that efficiently finds programs that mimic behaviours specified in examples. The *search space* is pruned using divide-and-conquer techniques.

- · Ranking Techniques that rank correct programs among the options that satisfy examples.

- The User Interaction Model, to guide synthesis and avoid selecting wrong programs.

The authors in [18] make an interesting comparison between Machine Learning (ML) and PBE as motivation to suggest that ML techniques are able to enhance the performance of PBE engines. Both involve prediction on new data after example-based training, yet the way they get to these predictions is very distinct. While ML requires huge quantities of training to generate sophisticated models with almost perfect precision for new inputs, PBE is expected to learn using few examples and generate solutions that provide perfect precision on new inputs. In any component, PBE engines use heuristic techniques, meaning that they can't guarantee that the search method or approach to the problem is optimal. ML can be used to learn and improve such heuristics, for example by analysing the structure of input-output

examples and capturing critical features.

Ranking techniques can also benefit from machine learning. Ranking schemes are used to differentiate programs that only perform as expected for given examples, from correct programs by giving them higher rankings. The subtle differences between both programs can be identified with the intent of building efficient learning rankers. User interaction models can accelerate synthesis process, for example, the user can rank multiple synthesized programs based on preference. In this module, PBE engine comes across multiple heuristic decisions including which programs to present to the user and in what order. The correctness of these decisions can be improved with ML.

### 2.4.2 Sketch

Sketching [19] allows programmers to design algorithms using *sketches* and high-level insights, leaving implementation of low-level details to be synthesized automatically. In Sketching, the programmer will provide a sketch and define the expected behaviour of the program, either in a set of tests the generated code must pass or in the form of reference implementation. A sketch is a partial program describing a general solution where difficult statements are unspecified — *holes*. The correct value for all *holes* are derived from this high-level strategy, using inductive synthesis, leaving the implementation of low-level details to be solved automatically by synthesis procedures.

Sketch relies on the *Counterexample Guided Inductive Synthesis (CEGIS)* algorithm to determine correct values for *holes*. CEGIS combines a SAT-based inductive synthesizer and an automated validation procedure, that checks if a candidate implementation is correct and produces new counterexamples. CEGIS alternates between two phases: (1) the *synthesis phase*, where an inductive synthesizer generates candidate programs that assign values to all holes in an attempt to satisfy the input implementation; and (2) the *verification phase*, where an automated validation checks if generated candidate program is indeed correct. In the cases the validation isn't accepted, the validation procedure produces counterexamples that demonstrate the failure, which can are then passed back to the synthesizer to inform its next iteration. The idea behind CEGIS is to utilise a checking tool capable of generating counterexamples to avoid testing the implementation on inputs that will fail in identical ways. By exposing problems associated to each candidate program, the synthesizer will gradually produce solutions closer to the desired solution and effectively guide the synthesis process.

Sketching often requires that developers are knowledgeable of the various low-level languages which is not suitable for practical programming.

*Holes* are marked with generators defining a set of expressions that can be selected by the synthesizer for their completion. The generator used to define unknown values is represented by '??'.

The repeat statement can be used in cases where the programmer has doubts about the number of times assignments should be in a loop. The construct repeat(n) produces *n* copies of the statement and

solves each copy independently. Sketch synthesis can be applied to multiple complex problems [19]. It successfully implemented an AES cipher by synthesizing fragments of code, for instance, the reference implementation used was transcribed from the NIST standard. The performance of the generated code by the sketch was found to be 10% less efficient when compared to hand written optimized code. Given the complexity of the problem, the quality of the optimized code was considered a good result. Many implementations of program synthesis combine techniques to generate low-level code for networking devices, developing new synthesis procedures for the different platforms. We explore these next.

### 2.5 Network Synthesis

Configuring data plane devices requires hardware expertise in the existing programmable network substrates. The ability to abstract the underlying hardware is one of the obstacles we face in this thesis: how to program a P4 programmable data plane from a generic network function specification, considering the underlying pipeline architecture and constraints.

Programmable devices and their respective programming languages have benefited from remarkable evolution in recent years, but are still at an early age and face challenges related to lack of abstractions for hardware features and capabilities, inhibiting their deployment in large scale networks. In this section, we will study how current synthesizers use program synthesis to generate different types of implementations. Systems will be separated in three different types according to their synthesis objective:

- 1. Configurations Synthesis, where systems are able to generate configuration that implement network wide policies (e.g, Cisco and Juniper) in conventional networks.

- 2. SDN Synthesis: systems able to generate policies to be executed on top of a SDN controller.

- 3. NF Synthesis: systems able to generate programs that implement network functions.

- 4. Synthesis of network programs: where systems are able to generate low-level configurations for network switching devices.

### 2.5.1 Configuration Synthesis

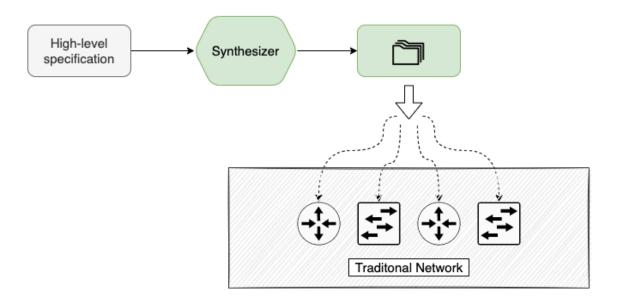

Network re-structuring can be highly disruptive to live traffic as the process of modifying and adjusting configurations for individual nodes is demanding and error-prone. In this section we analyse tools that aim to solve this issue by synthesizing optimized router configurations that implement network-wide policies in conventional networks, avoiding operator misconfigurations and any subsequent network outages. In fig. 2.3 we demonstrate a general example for these kind of synthesis tools.

Inspired by recent work on program synthesis, Beckket *et al.* [20] developed **Propane/AT**, a system capable of generating BGP configurations from high-level specifications for network topology, routing policies and fault-tolerance requirements. This framework was designed to be a improved version of

Figure 2.3: Illustrative example of Configuration Synthesis tools.

**Propane** [21], which introduced program analysis and compilation algorithms to translate regular policies into graph-based intermediate representations from which BGP configurations could be derived. These tools used regular expression to represent the various network specifications.

Additionally, Propane/AT takes as input the policy for the abstract topology. The policy consists of routing policy and a fault-tolerance policy. The synthesis process is divided into three phases. First, the routing policy and abstract topology are combined into a product graph (PG) containing the routing information for the topology in a policy-compliant manner. The algorithms used to manipulate Graphs are adapted from Propane. Second, Propane/AT checks compliance with the fault-tolerance policy. If met, a template for each node is generated in a third step. Transforming the template into BGP configurations — *concretization* — is done using a vendor-independent BGP configuration language. Results show that this framework is effective in real-world topologies and policies and configuration synthesis is considerably faster than systems that operate over concrete topologies.

At the time, the current existing tools supported a limited number of protocols, for example, Propane/AT was limited to BGP configurations and Genesis was limited to generating static router configurations. Addressing this limitation, El-Hassany *et al.* proposed a system capable of extending its supported routing protocols. **SyNET** [22] was able to synthesize correct network configurations for multiple and interacting routing protocols (OSPF and BGP) and static routes from requirements specified by an operator. Differently from the previous tools, SyNET does not uses regular expressions to describe network policies but Stratified Datalog, an expressive and complex declarative programming language suitable for describing routing protocols and capturing behaviour of the network in a clear and declarative manner, and a allowing operators to model routing protocols, the interactions between them, the topology of the network, and requirements such as reachability, path requirements, and traffic isolation. To synthesize configurations, SyNET applies an iterative algorithm to generate configurations by reducing input synthesis problem to SMT constraints. SyNET scales to real-world networks, synthesizing configurations for networks with 32 or less routers within an hour. For larger networks, with more than 64 routers, SyNET can take more than 24 hours to synthesize configurations, leaving some space for optimization. Another relevant topic discussed in SyNET is the idea that it is possible to take advantage of networks that are organized hier-archically around some regions and whose configurations can be synthesized independently. Although SyNAPSE does not consider network topologies, this idea could be applied to the binary decision diagram our Search Engine takes as input. SyNET approaches synthesis in a distinct manner from the above mentioned synthesis-based compilers by using a declarative logic language to describe routing protocols. The authors compared SyNET to tools of the likes of Propane/AT and Genesis and affirmed that SyNET is a more general system, as it allows for routing protocols to be added in stratified Datalog to synthesize configurations.

El-Hassany et al. presented a tool with the same goal of assisting network operators in modifying existing network-wide configurations to comply with new routing policies, using Sketch (section 2.4.2). Similarly to SyNET, NetComplete [23] supports static routes, OSPF, BGP and additionally, other routing requirements such as load balancing and traffic isolation are supported. The synthesizer scales much better for large networks, performing orders of magnitude faster than NetComplete. The synthesizer takes three inputs: the network topology, routing requirements and configuration sketches. NetComplete follows three steps to synthesize configurations for network-wide configurations. Firstly, the static routes defined in the routing requirements are synthesized. After that, BGP router-level configurations are synthesized from BGP requirements and policy sketches, computing a propagation graph with the order of BGP announcements. This process can also produce a set of constraints that need to be enforced in the OSPF synthesizer. Finally, the OSPF synthesizer uses CEGIS to comply with all requirements. This is known to be a complex search problem mainly for larger networks. CEGIS significantly improves OSPF synthesis compared to naive synthesis, where all requirements are simply introduced in a constraint solver to discover a model that computes link costs. With this search method, NetComplete evaluation results showed that the system is at least 600 times faster than SyNET and, as mentioned before, it is capable of synthesizing configurations for large topologies for which SyNET times out.

#### 2.5.2 SDN Synthesis

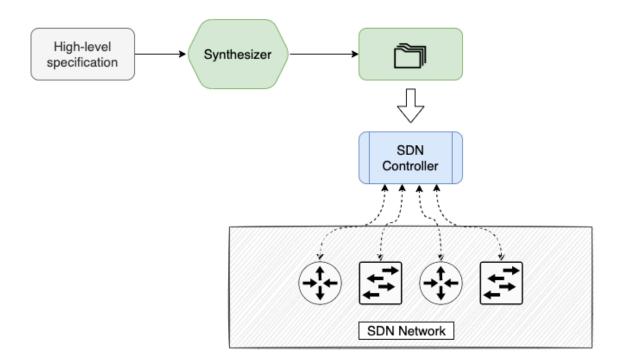

With the emergence of Software Defined Networks, network controllers allow operators to implement a wide range of policies controlling switches in a network through SDN protocols. In this section we mention tools that generate configurations that are executed on top of a SDN from high-level specifications

Figure 2.4: Illustrative example of SDN Synthesis tools.

of network policies and changes in the network state, as illustrated in fig. 2.4. The high-level domainspecific languages developed in the past years have greatly reduced the complexity of programming controller interfaces, however, programming SDN networks is still limited to a very reduced number of specialized network developers.

Towards the mitigation of this condition, Saha *et al.* [24] developed **NetGen**, a tool that automates the process of synthesizing configurations for the changes in the data-plane, and a specification language to express desired changes in an existing network. NetGen updates configurations by finding the minimal amount of changes to the network to satisfy a high-level specification.

NetGen presents a high-level language, based on regular expressions, to express desired changes in an existing network. The synthesis algorithm is capable of finding new network changes based on abstractions and constraint-solvers that generate new data plane states, different from the current implemented configurations in the network. The algorithm uses a state-machine to find the most reasonable number of changes to obtain the new data plane state. A distinct aspect of NetGen is that paths can be synthesized independently without affecting existing synthesized paths. NetGen was tested for larger networks with success with the authors proving its scalability by using NetGen in real-world networks of large dimensions. In comparison with previously developed synthesis-based compilers (2015), Net-Gen was more flexible and more widely applicable. It also approached configuration synthesis from a different perspective, as existing synthesis-based compilers like FatTire, Alloy and Merlin attempted to synthesize configurations for specific requirements, whereas NetGen uniquely synthesized new configurations by performing changes to existing ones. The use of regular expressions by tools allowed developers to define desired traffic patterns, however, Subramanian et al. [7] verified that the use of regular expressions can lead to increased number of constraints introduced in the SMT solver, thus slowing down the search process. Subramanian et al. presented Genesis, a network management system for multi-tenant datacenter networks and the use of tactics, a restricted form of regular expressions, that blacklists paths in a network based on patterns that are not desired. In Genesis, rich policies can be specified in a declarative manner allowing SMT constraint solvers to be used to program the underlying data plane, more specifically, to synthesize switch forwarding tables, that are subsequently introduced in network devices by a controller. By allowing developers to use isolating policies, a feature which was not implemented in similar previous tools, Genesis sped up significantly the synthesis procedure. Genesis is also capable of handling failures using a mechanism called *minimal repair* that calculates the minimal number of switches whose rule tables are modified before transitioning from a disrupted data plane to a new, and once again, policy-compliant state. To synthesize policies authors use a divide-and-conquer strategy to partition synthesis problems into smaller ones. These tools were significant advances in the area of program synthesis for network-wide configurations, however they were somewhat limited as Genesis only supported static routes and Propane/AT only supported BGP configurations.

Yuan *et al.* followed a different approach to generate SDN programs, presenting a scenario-based programming tool named **NetEgg** [25]. NetEgg allows network operators to program policies by describing representative example behaviours, from which it synthesizes automatically policy implementations to be executed on top of a centralized controller. The scenarios NetEgg receives as input are composed of examples of packet traces and their corresponding actions to each packet. The tool is capable of synthesizing automatically controller programs that are consistent with the example behaviours while the interpreter executes the policies according to incoming network events on the controller and infers rules that can be pushed onto switches [25].

NetEgg provides a configuration language to express network behaviour in representative scenarios, where packet variables and fields are typed. A packet-type consists of a list of names of fields of the packet along with their types. NetEgg also provides a library with standard packet fields and actions, such as flood, send(port), and modify(f,v) (modifying the value of a given field). Before the synthesizer tries to generate a policy according to these scenarios, it checks for any existing conflicts between them. If any exist, they are displayed to the network operator to be resolved.NetEgg can generate policy implementations within seconds with less overhead, when compared to other POX [26] implementations (the platform used for SDN control applications). The interpreter was tested for its Rule installation process, and results show that rules are installed correctly from the first incoming packet-in event.

NetEgg pioneered the approach of using examples to write network programs, however it only con-

sidered networks where the control plane was centralized in a single controller. In an SDN network, the control plane can be physically centralized or distributed, with controller processes running on multiple network nodes. **McClurg** *et al.* [27] addresses the problem of programming distributed controllers by taking a buggy decentralized program and inserting the necessary synchronization to make it correct. The authors highlight two concurrency challenges specific to networks with multiple controllers. They are *controller races* and *packet races* and both capable of introducing serious problems such as packet loss. The packet race happens when one of the controllers removes a forwarding rule, to introduce a new one. In between the two events the controller races adds rules that forward incoming packets in an incorrect manner. Its authors use a program synthesis approach to simplify writing distributed controller programs, so that programmers don't need to focus on keeping track of possible interleavings of controller processes to ensure the specification is always in compliance.

*McClurg* uses a CEGIS algorithm to find synchronization constructs to correctly synchronize the event net. CEGIS uses an *event net repair engine* to synthesize candidate event nets from the input event nets and a finite set of known counterexample traces and uses an *event net verifier* to check whether the candidate satisfies the LTL property, producing a counterexample trace if not. The developed prototype is deployed efficiently in several network topologies.

#### 2.5.3 Network Function Synthesis

**Yanjun Wang** *et al.* [28] suggests an approach to learn the objectives of a network design through iterative interactions with the network architect. Frameworks mentioned earlier are capable of generating a solution assuming well-defined objectives, but in practice it can be challenging for an architect to precisely state the desired objectives. Its authors argue that besides the challenge of solving well-defined problems, the task of obtaining a formal specification that reflects the architects goals is also a complex problem. The challenge in network design relates to the determination of objective functions that reconciles multiple criteria, such as resource allocation and traffic engineering goals (latency, throughput, fairness). This approach is motivated by PBE systems (section 2.4.1), however, PBE techniques don't suit *comparative synthesis* as it requires the architect to specify and provide feedback on exact objectives. In this context if the architect could provide such feedback, he would have written the precise objective function. To explain the synthesis process we will consider the example mentioned by the authors, where the goal is to synthesize an objective function on both throughput and latency of a network design. The synthesis process starts with one or more sketches (section 2.4.2) or templates of typical objective functions, that reconcile throughput and latency. Initially, random weights are assigned to each unknown variable and the system queries the user about the ranking of a given set of concrete scenarios. User's preferences are then recorded in a Direct Acyclic Graphs (DAG) used to discard incorrect solutions and provided better scenarios, *i.e.* with better SMT-generated candidates, from which the user will continue to choose. As the user provides feedback in each iteration, the DAG grows in size, the SMT solver produces better candidates, and scenarios start to converge to the preferred user scenario. Eventually, if the preference graph is rich enough the SMT will return unsatisfiable, meaning only one possible solution is viable. Because the initial inputs are randomly assigned the experiments are non-deterministic. The authors conclude that (1) the developed prototype is capable of synthesizing correct object functions from multiple interactions with the user, and (2) the most optimal solution is for the user to rank 3 scenarios at time, which only reduced the amount of interaction moderately but decreased the total time of synthesis significantly. Similarly to this implementation, our tool should be able to discard solutions and make decisions to achieve a desired metric by manipulating DAGs, for example, "reconcile throughput and latency".

#### 2.5.4 Network Program Synthesis

In this section we will examine compilers that use program synthesis to program configurations onto programmable network devices. Although these devices allow to deploy NFs onto networks and support packet processing at high speeds, programming them its a task that requires knowledge of the pipeline and other hardware details. Even with the recent development of DSLs targeting these devices, there is still a significantly learning curve for the average operator. Program synthesis can address this issue and has been used automatically generate packet-processing code that can result in faster processing/forwarding. In fig. 2.5 we demonstrate a general description for network program synthesis tools.

Haoxian *et al.* developed **Facon** [29], a tool that addressed the proliferation of DSLs for programmable networks enabling automatic generation of *control plane* programs using arbitrary DSLs, based on input/output examples. Instead of generating device configurations, like NetEgg does, Facon generates the program whose function is to generate data plane configurations. The synthesizer takes two kinds of inputs, either the mentioned examples or Network DataLog (NDLog) relation schemas, and produces an NDLog program that satisfies all input-output examples.

The developed prototype was only used to evaluate feasibility and performance of Facon, thus only 4 simple programs were synthesized: a learning switch, a recursive reachability program, a stateful firewall, and a program for application-based forwarding. All were synthesized within a reasonable time budget, even for programs with a larger input size (a stateful firewall and application-based forwarding), as Facon is able to reduce the number of iterations to search within huge search spaces. Additionally, because Facon generates a program instead of configurations, the programs can be moved between networks with different underlying architectures. Generating the programs from input/output examples also allows Facon to transform from one DSL to others. Facon proposes search algorithms and heuris-

tics, to guide the search direction, that can serve as inspiration to improvements to our first prototype. However, they target control plane programs, while we target data plane programs. Our challenge is therefore different as the data plane programs are more low-level, closer to the hardware architecture.

One of the challenging characteristics of programming hardware devices relates to their *all-or-nothing* nature, where if a program can fit within pipeline resources, it will run at line rate; otherwise, it will not run at all. Usually this task is handed over to a compiler, but standard rule-based compilers often are unable to rewrite programs so that they fit within the switch limited resources. Motivated by these drawbacks and by the achievements of program synthesis in related areas, Gao *et al.* proposed synthesizing code for hardware devices, presenting **Chipmunk** [30, 31] as a compiler that uses the SKETCH synthesizer to transform high-level programs (P4 or Domino) to switch machine code that fits within resource limits.

The synthesizer takes two inputs, a specification and a *sketch*, and generates a pipeline implementation. The sketch (section 2.4.2) is a partial problem with holes that represent unknown values in a finite range of integers that describe low-level machine code. To speed up synthesis, its authors developed a technique called *slicing* where each slice corresponds to a simpler synthesis problem. After synthesized, each slice is merged by stacking the resulting pipeline on top of each other composing the final hardware implementation. Other optimizations where introduced in the Chipmunk compiler, such as scaling up synthesis to larger inputs, constant synthesis and canonicalization. Chipmunk was designed with the intention to be *retargetable*, i.e to apply the same underlying program synthesis to multiple backend targets, generating machine code for different pipeline architectures by analysing declarative specification of given targets. In order to accomplish retargetability, the authors developed a DSL — the pipeline description language — to specify hardware pipeline capabilities. A switch hardware simulator was used to compare Chipmunk to Domino, in order to evaluate its performance against rule-based compilers. Domino [32] is a high-level language to program data-plane algorithms. Domino programs are compiled into low-level code that can run in programmable line-rate switching chips. Some noticeable findings included:

- Chipmunk is able to compile programs that are rejected by Domino, yet Domino's compile times are faster than Chipmunk.

- · Chipmunk generates code with fewer pipeline stages a highly constrained switch resource

- The slicing technique speeds up synthesis process by 51 times, on average.

The approach used here to build a retargetable compiler, as well as the optimization techniques used, are also highly relevant to this thesis and have informed our design choices. However, they generate a compiler from P4 to machine code, while our goal is to generate a P4 program from a high-level language program.

Other approach with a similar goal to Chipmunk – and therefore different to ours – is **Lyra** [33], a highlevel language and compiler that enables programmers to efficiently program the data plane through a *"one-big-pipeline"* abstraction that allows programmers to use simple statements to express their intents without worrying about the underlying hardware details. Lyra also supports simultaneous deployment of multiple programs and programs that need to be executed in distributed ways, challenges mentioned in 2.5. The motivation example presented in Lyra's paper is a *load-balancer* that requires that NF to be deployed in different nodes according to their functionality in the network.

Data plane programs are written in chip-specific languages (P4 and NPL) that are tightly coupled to chip-specific architectures. Nevertheless, Lyra is capable of synthesizing code pieces for different chip-specific architectures while meeting functional correctness specified by the input Lyra program. Its key methodology consists in encoding all logic and constraints into an SMT problem and use an SMT solver to find an optimal implementation and deployment strategy for a target network.

The single pipeline abstraction is composed of chained modules that can be divided into Front-End and Back-End, taking as input high-level Lyra program, an algorithm scope describing each algorithm's placement, and a network topology and its configurations.