## **LLVM Backend Support for Data Streaming Extensions**

### **Tiago Cardoso Pires**

Thesis to obtain the Master of Science Degree in

## **Electrical and Computer Engineering**

Supervisors: Prof. Nuno Filipe Simões Santos Moraes da Silva Neves Prof. Pedro Filipe Zeferino Aidos Tomás

#### **Examination Committee**

Chairperson: Prof. Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Prof. Nuno Filipe Simões Santos Moraes da Silva Neves Member of the Committee: Prof. João Carlos Viegas Martins Bispo

November 2021

## **Declaration**

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

## **Acknowledgments**

I would like to thank my family for always supporting me through this journey, who was always by my side every time I needed. A special thanks also to Cátia for her tireless support and encouragement.

Also a special thanks to Prof. Nuno Roma, Prof. Pedro Tomás and Prof. Nuno Neves who were always available and helpful to give the expertise and transmit the knowledge necessary to complete this work.

Last but not least, I would also like to thank all my friends and colleagues with who I had the pleasure to share this adventure with.

Thank you all.

This work was partially supported by national funds through Fundacão para a Ciência e a Tecnologia (FCT) under projects UIDB/50021/2020 and PTDC/EEI-HAC/30485/2017.

## Abstract

Unlimited Vector Extension (UVE) is a novel ISA extension that incorporates data streaming and scalable vectorization. To do so, it implements a data streaming engine that allows detaching the main memory access from computation, releasing some pressure from the main pipeline of the processor. This is done by statically encoding the memory access pattern of streamable loops through a set of special description instructions, to offload the corresponding address sequence generation to the streaming engine. This not only allows the computational code to be simplified by removing memory addressing instructions, but also simplifies the vectorization of the loop, in turn increasing the throughput of the processing cores. However a new extension that implements target specific instructions, it still lacks compiler support to produce target code. Accordingly, in this thesis aims at taking the first steps in the development of a compiler for UVE by instantiating a new subtarget from RISC-V's LLVM backend and creating and encoding the extension's instructions. To provide an initial integration with LLVM IR, a set of intrinsics is also proposed that match the instructions. Due to the intrinsic incompatibility between the streaming paradigm from UVE and LLVM IR SSA form, a new approach to overcome this issue is introduced based on pseudo-instructions . The new backend and LLVM IR intrinsics were evaluated with a set of benchmarks that highlight the main introduced features.

## **Keywords**

Scalable Vector Processing; Stream Computing; LLVM IR; Compiler Backend

## Resumo

Unlimited Vector Extension é uma extensão nova que incorpora fluxos de dados e vetorização escalável. Para tal, implementa uma unidade de fluxo de dados que permite desconectar acessos à memória princial da computação, aliviando alguma pressão da linha principal do processador. Isto é feito através da codificação estática de padrões de acesso à memória em ciclos que permitem fluxos de dados através de um grupo especial de instruções descriptivas, para transferir a correspondente geração de sequência de endereços para a unidade de fluxo de dados. Isto não só permite o código computacional de ser simplificado através da remoção de intruções de endereçamento à memória, mas também simplifica a vetorização do ciclo, aumentando a taxa de transferência dos núcleos de processamento. No entanto por ser uma nova extensão que implementa instruções específicas, ainda não possui suporte de compiladores para produzir o código específico. Nesse sentido, esta tese visa dar os primeiros passos no desenvolvimento de um compilador para UVE instanciando um novo sub-alvo do backend LLVM do RISC-V e criando e codificando as instruções da extensão. Para fornecer uma integração inicial com o LLVM IR, um conjunto de intrínsecas é também proposto que combina com as intruções. Devido à incompatibilidade intrínseca entre o paradigma de fluxo de dados do UVE e a forma SSA do LLVM IR, é introduzida uma nova abordagem baseada em pseudo-intruções para superar este problema. O novo backend e as intrínsecas de LLVM IR foram avaliadas com um conjunto de padrões de desempenho que destacam as principais características introduzidas.

## Palavras Chave

Processamento Vectorial Escalável; Computação em Fluxo de Dados; Representação Intermédia do LLVM; Backend do Compilador

# Contents

| 1 | Intro | oductio | n          |                                  | 1    |

|---|-------|---------|------------|----------------------------------|------|

|   | 1.1   | Motiva  | ition      |                                  | . 3  |

|   | 1.2   | Object  | tives      |                                  | . 4  |

|   | 1.3   | Contri  | butions .  |                                  | . 4  |

|   | 1.4   | Outline | ə          |                                  | . 4  |

| 2 | Bac   | kgroun  | d          |                                  | 7    |

|   | 2.1   | Comp    | ilers      |                                  | . 9  |

|   |       | 2.1.1   | History of | of the Compiler                  | . 9  |

|   |       | 2.1.2   | Structur   | e of a Compiler                  | . 9  |

|   |       |         | 2.1.2.A    | Lexical Analyser                 | . 10 |

|   |       |         | 2.1.2.B    | Syntax Analyser                  | . 10 |

|   |       |         | 2.1.2.C    | Semantic Analyser                | . 11 |

|   |       |         | 2.1.2.D    | Intermediate Code Generation     | . 12 |

|   |       |         | 2.1.2.E    | Intermediate Code Optimization   | . 12 |

|   |       |         | 2.1.2.F    | Target Code Generation           | . 13 |

|   |       |         | 2.1.2.G    | Target Code Optimization         | . 14 |

|   |       | 2.1.3   | LLVM In    | frastructure                     | . 14 |

|   |       |         | 2.1.3.A    | Frontend                         | . 14 |

|   |       |         | 2.1.3.B    | LLVM IR                          | . 15 |

|   |       |         | 2.1.3.C    | Backend                          | . 16 |

|   | 2.2   | Vector  | Extensio   | ons                              | . 21 |

|   |       | 2.2.1   | SIMD ar    | nd Scalable Vectorial Extensions | . 21 |

|   |       |         | 2.2.1.A    | SIMD                             | . 22 |

|   |       |         | 2.2.1.B    | Scalable Vectorial Extensions    | . 23 |

|   | 2.3   | Unlimi  | ted Vecto  | or Extension                     | . 24 |

|   |       | 2.3.1   | Memory     | Access Description               | . 24 |

|   |       | 2.3.2   | UVE Str    | eams                             | . 27 |

|    |       | 2.3.3 UVE Instruction Set Architecture |                                                  |    |

|----|-------|----------------------------------------|--------------------------------------------------|----|

|    |       |                                        | 2.3.3.A Register File                            | 28 |

|    |       |                                        | 2.3.3.B Instructions overview                    | 29 |

|    | 2.4   | Relate                                 | ed Work                                          | 33 |

|    | 2.5   | Summ                                   | nary                                             | 34 |

| 3  | Imp   | lement                                 | ing UVE on LLVM                                  | 35 |

|    | 3.1   | LLVM                                   | Supporting Extension Requirements                | 37 |

|    | 3.2   | LLVM                                   | Support Implementation                           | 38 |

|    |       | 3.2.1                                  | Setup                                            | 38 |

|    |       | 3.2.2                                  | Register Definition                              | 39 |

|    |       | 3.2.3                                  | UVE Instructions Definition                      | 40 |

|    |       |                                        | 3.2.3.A Implementing UVE Arithmetic Instructions | 40 |

|    |       |                                        | 3.2.3.B Implementing UVE Logic Instructions      | 43 |

|    |       |                                        | 3.2.3.C Implementing UVE Branch Instructions     | 44 |

|    |       | 3.2.4                                  | Creating support for UVE instructions in LLVM IR | 45 |

|    |       |                                        | 3.2.4.A Defining LLVM Instrinsics                | 46 |

|    |       |                                        | 3.2.4.B Creating Patterns                        | 47 |

|    |       |                                        | 3.2.4.C Overcoming LLVM IR SSA Form              | 49 |

|    |       | 3.2.5                                  | Register Coalescing                              | 52 |

|    | 3.3   | Summ                                   |                                                  | 54 |

| 4  | Res   | ults an                                | nd Discussion                                    | 57 |

|    | 4.1   | Evalua                                 | ation Method                                     | 59 |

|    | 4.2   | Bench                                  | nmarks Evaluation                                | 59 |

|    |       | 4.2.1                                  | SAXPY                                            | 59 |

|    |       | 4.2.2                                  | Trisolv                                          | 61 |

|    |       | 4.2.3                                  | SPMV                                             | 62 |

|    | 4.3   | Summ                                   | nary                                             | 66 |

| 5  | Con   | clusio                                 | ns and Future Work                               | 67 |

|    | 5.1   | Concl                                  | usions                                           | 69 |

|    | 5.2   | Future                                 | e Work                                           | 69 |

| Bi | bliog | raphy                                  |                                                  | 71 |

# **List of Figures**

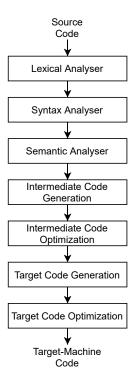

| 2.1  | Compiler Structure                                                            | 10 |

|------|-------------------------------------------------------------------------------|----|

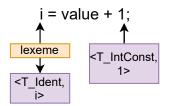

| 2.2  | Example of Lexical Analysis.                                                  | 11 |

| 2.3  | Example of Syntax Analysis.                                                   | 11 |

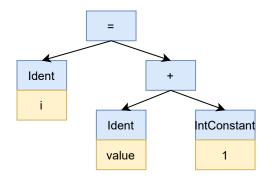

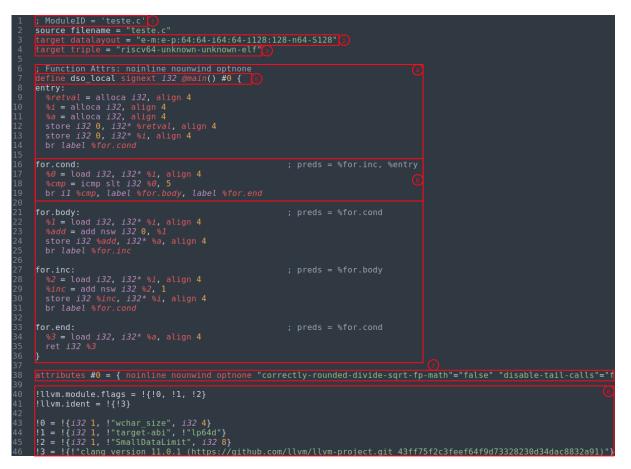

| 2.4  | Example of LLVM IR                                                            | 15 |

| 2.5  | Example of selection DAG after being built.                                   | 17 |

| 2.6  | Example of initial DAG after being optimized.                                 | 18 |

| 2.7  | Example of DAG legalization.                                                  | 19 |

| 2.8  | Example of final DAG after legalization.                                      | 20 |

| 2.9  | Example of the instruction selection process.                                 | 20 |

| 2.10 | Example of final DAG after instruction selection.                             | 21 |

| 2.11 | Example of instruction scheduling.                                            | 21 |

| 2.12 | Example of emitting machine instruction                                       | 22 |

| 2.13 | Example of register allocation using the greedy method                        | 22 |

| 2.14 | Descriptor specification proposed by Neves et al. [1]                         | 25 |

| 2.15 | Access Descriptor encoding a triangular matrix access by Neves et al. [1]     | 26 |

| 2.16 | Access Descriptor encoding an indirect memory indexation by Neves et al. [1]  | 27 |

| 2.17 | Descriptors summary by Domingos et al. [2].                                   | 28 |

| 2.18 | Description of the structure of UVE vectorial register by Domingos et al. [2] | 29 |

| 2.19 | Description of UVE Add instruction by Domingos et al. [2]                     | 30 |

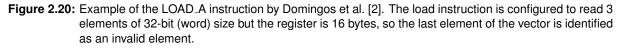

| 2.20 | Example of the LOAD_A instruction by Domingos et al. [2]                      | 31 |

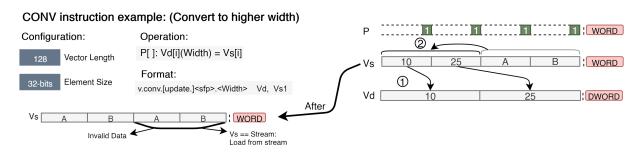

| 2.21 | Conversion between vectors by Domingos et al. [2].                            | 32 |

| 3.1  | Example instruction before and after the two address instruction pass.        | 50 |

| 3.2  | Example Machine Instructions and corresponding input and output variables     | 53 |

| 3.3  | Example register mapping of the variables defined in Figure 3.2.              | 54 |

# **List of Tables**

| 3.1 | RISC V R-type and B-type formats, respectively from top to bottom [3] | 41 |

|-----|-----------------------------------------------------------------------|----|

| 3.2 | UVE Arithmetic-type format.                                           | 41 |

| 3.3 | UVE Logic-type format.                                                | 43 |

| 3.4 | UVE Branch-type format.                                               | 44 |

# Listings

| 3.1  | Implementation of <i>SubtargetFeature</i> and <i>Predicate</i> classes                      | 38 |

|------|---------------------------------------------------------------------------------------------|----|

| 3.2  | Adding previously defined features to <i>RISCVSubtarget</i> class                           | 38 |

| 3.3  | Defining UVE registers.                                                                     | 39 |

| 3.4  | Definition of <i>RVInst</i> class                                                           | 40 |

| 3.5  | Definition of $UVE\_ARITH\_V\_VVP\_f$ derived class                                         | 41 |

| 3.6  | Definition of class and multiclass to define arithmetic instructions                        | 42 |

| 3.7  | Definition of arithmetic instructions                                                       | 42 |

| 3.8  | Definition of $UVE\_LOGIC\_V\_VSP\_f$ derived class                                         | 43 |

| 3.9  | Definition of class to define logic instructions.                                           | 43 |

| 3.10 | Definition of logic instructions.                                                           | 44 |

| 3.11 | Definition of UVE_BRANCH_f derived class.                                                   | 44 |

| 3.12 | Fixup value adjustment.                                                                     | 45 |

| 3.13 | Definition of Intrinsic class.                                                              | 46 |

| 3.14 | Definition of arithmetic derived classes and arithmetic intrinsics                          | 47 |

| 3.15 | Definition of branch derived classes and branch intrinsics                                  | 48 |

| 3.16 | Patterns between logic intrinsics and logic instructions                                    | 48 |

| 3.17 | Patterns between branch intrinsics and branch instructions                                  | 49 |

| 3.18 | Definition of arithmetic derived classes and arithmetic intrinsics with pseudo-instructions |    |

|      | in mind                                                                                     | 51 |

| 3.19 | Definition of pseudo arithmetic derived classes and arithmetic pseudo-instructions          | 51 |

| 3.20 | Expanding pseudo-instruction that matches with UVE_ABS _FP instruction                      | 52 |

| 4.1  | SAXPY kernel described in C language                                                        | 60 |

| 4.2  | SAXPY kernel described in LLVM IR                                                           | 60 |

| 4.3  | SAXPY kernel assembly format after compilation                                              | 61 |

| 4.4  | Trisolv kernel described in C language                                                      | 61 |

| 4.5  | Trisolv kernel described in LLVM IR                                                         | 62 |

| 4.6  | Trisolv kernel assembly format after compilation.                                           | 63 |

| 4.7  | SPMV kernel described in C language                                       | 63 |

|------|---------------------------------------------------------------------------|----|

| 4.8  | SPMV kernel described in LLVM IR                                          | 64 |

| 4.9  | SPMV kernel assembly format after compilation.                            | 65 |

| 4.10 | SPMV kernel assembly format without freezing intrinsics after compilation | 66 |

# Acronyms

| AST   | Abstract Syntax Tree                      |

|-------|-------------------------------------------|

| CFG   | Context Free Grammar                      |

| CISC  | Complex Instruction Set Computer          |

| CPU   | Central Processing Unit                   |

| CSR   | Control Status Registers                  |

| DAG   | Directed Acyclic Graph                    |

| DCE   | Dead Code Elimination                     |

| DeSC  | Decoupled Supply-Compute                  |

| DFA   | Determinitic Finite Automata              |

| DLP   | Data Level Parallelism                    |

| ELF   | Executable and Linkable Format            |

| HPC   | High Performance Computing                |

| IDE   | Integrated Development Environment        |

| IR    | Intermediate Representation               |

| ISA   | Instruction Set Architecture              |

| JIT   | Just-In-Time                              |

| ML    | Machine Learning                          |

| MVT   | Machine Value Types                       |

| NFA   | Nondeterminitic Finite Automata           |

| PBQP  | Partitioned Boolean Quadratic Programming |

| RISC  | Reduced Instruction Set Computer          |

| SAXPY | Single-Precision A· X Plus Y              |

|       |                                           |

| SIMD | Single Instruction Multiple Data |

|------|----------------------------------|

| SLL  | Shift Logical Left               |

| SPMV | Sparse Matrix-Vector Multiply    |

| SSA  | Static Single-Assignment         |

| SSE  | Streaming SIMD Extensions        |

| SVE  | Scalable Vector Extension        |

| TAC  | Three-Address Code               |

| UVE  | Unlimited Vector Extension       |

| VL   | Vector-Lenght                    |

# Introduction

#### Contents

| 1.1 | Motivation    | 3 |

|-----|---------------|---|

| 1.2 | Objectives    | 4 |

| 1.3 | Contributions | 4 |

| 1.4 | Outline       | 4 |

#### 1.1 Motivation

Throughout the years multiple innovations have come up in the computing area to improve the performance of the processor, by using different architectures and paradigms. Some of these apply in a general way, by changing the structure completely while others are targeted for some specific purpose. One of these specific paradigms is Single Instruction Multiple Data (SIMD) [4–6], that tries to take advantage from vector-like patterns displayed by the memory accesses of some applications, such as digital signal processing and graphics processing.

SIMD units allow to fix an element size for the vector, depending on the extension, and process multiple elements while only issuing a single instruction to do it. This has clear advantages in the sense that it saves time by increasing the throughput of the processing unit.

While the use of SIMD increases the performance for some applications, it has issues. Depending on the extension, the Vector-Lenght (VL) is limited to a fixed number of bits, constraining the overall improvement that can be seen in the performance of the processor. To solve this problem the obvious solution is to eliminate the fixed limit on the VL, and that is what ARM did when they introduced Arm Scalable Vector Extension (SVE) [7], a SIMD extension to the Arm AArch64 architecture. This extension allows flexible VL implementations, that can vary from a minimum of 128 bits up to a maximum of 2048 bits, with 128-bit increments. As such, the design doesn't force the processor to implement the maximum VL and it's still able to run the same application in different implementations of SVE, without recompiling the code.

As it is a vector extension, SVE presents the largest application improvements when very large amounts of data need to processed. However it does not present a solution for memory access, where it can cause a bottleneck on the application if the data is not available for processing as it is necessary. Prefetchers partially solve this problem by speculating on what data it might be necessary on the future and fetching it ahead of time, but it is not as effective on irregular memory accesses and short memory accesses. It also never achieves a perfect prediction accuracy of the data that needs to be prefetched.

This is where the Unlimited Vector Extension (UVE) [2] presents an improvement. By combining SIMD instructions with data streaming it tries to solve both problems at once. To achieve a perfect data prefetching accuracy it describes the memory access patterns in software, allowing for that data to be streamed into a dedicated engine and used by the main processing pipeline as it is necessary.

To ease the development of new software for a new architecture it is usual to develop compiler support for that target, so that it is not necessary to write low level code. This is usually provided by the companies that also develop the architecture.

The aim of this work is to provide a LLVM backend to RISC-V's architecture extension that supports the UVE extension to be used during software development, by taking advantage of the LLVM modular structure. LLVM allows for the addition of specific UVE features while making minimal impact on the overall structure of the compiler. The new compiler extension should be able to represent UVE instructions or other form of representation, such as intrinsics, in LLVM Intermediate Representation (IR), that will latter go through the compiler pipeline and transformed into UVE target code. If possible it should also reuse some parts of other implementations that share similarities, such as Arm SVE, while also creating new solutions dedicated to the new extension.

#### 1.2 Objectives

Given that the UVE Instruction Set Architecture (ISA) is already fully defined, a supporting compiler extension can be developed in LLVM, targeting the RISC-V architecture. This extension should give support on the backend for the new instructions as well as some way to represent such instructions in LLVM IR.

As such, the main objectives of this work are to create a fully functional UVE backend on LLVM that allows for the compilation of IR into the target assembly code, a representation that enables the use of UVE instructions inside LLVM IR and an evaluation of the implemented solution using representative benchmarks, that make use of most developed features.

#### 1.3 Contributions

Contributions that will come out of this work are the following:

- A functional backend that can compile from IR into UVE's assembly code, using the custom instructions.

- A representation to embed UVE instructions with the rest of the LLVM IR, so that it can represent data streams and its nuances.

- One method to overcome the Single Static Assignment enforced by the LLVM IR representation and another to avoid streaming registers from being written over during register allocation.

- The successful compilation using the implemented compiler extension of a set of three benchmarks that represent the custom features.

#### 1.4 Outline

This document is divided into four chapters. On chapter 2, a backgroud is done to explain some necessary concepts that will be used in chapters ahead related to the structure and functioning of compilers and the implementation of various vectorial extensions, culminating with UVE. Following chapter 2 is the development of compiler support, on chapter 3. During this chapter it is described the processes and methods used by LLVM to support new architectures and a solution is presented that allows to compile from an IR into assembly code. On chapter 4 an evaluation of the proposed solution is done, by compiling a set of three benchmarks that highlight the main features of the implementation. On the 5th and final chapter a conclusion is presented about the work developed and some future directions for the continuation and improvements of this work.

# 2

# Background

#### Contents

| 2.1 | Compilers                  |

|-----|----------------------------|

| 2.2 | Vector Extensions          |

| 2.3 | Unlimited Vector Extension |

| 2.4 | Related Work               |

| 2.5 | Summary                    |

#### 2.1 Compilers

The compiler is a computer program that transforms source code, usually written in a programming language, into a certain target machine language.

To start with, it is presented a brief description of the history of the compiler and how it came to be. After that, a generic structure of a compiler is described, and the multiple stages it encompass. Lastly, the description of the LLVM Infrastructure and all the stages and methods it uses to implement a compiler, that is used within the scope of this work.

#### 2.1.1 History of the Compiler

During the 1950's and before, programming was done on a much lower level, such as assembly language or even machine code. The main reasons for that were the constraints on memory available at the time, slow clock rates that made every single instruction precious and the amount of work needed to develop a compiler. There was no need to compile a program that was small in size, as it could be written directly in assembly, and the lack of memory available sometimes prohibited the hosting of a compiler on the machine. Also at that time programs written by hand were more optimized then the compiled versions.

In 1951 Grace Hopper first introduced the term "compiler" and in 1957 John W. Backus and his FORTRAN team developed the first commercially available compiler [8,9].

The increase in memory availability, program complexity and processing power, as well as the cost for developing big projects during the following years led to a more widely use of compilers, to be able to program in higher-level languages. During the 1970's only critical parts of a program were written by hand, usually in assembly language as it would still lead to more optimized code [10]. For the following years, the main focus was on the performance of the resulting program and the speed it takes to compile it.

#### 2.1.2 Structure of a Compiler

For most compilers, the structure follows the principles presented in Figure 2.1 [11]. This structure can be divided in two categories: the frontend and the backend. The frontend consists on the analysis of the source file and following decomposition into an intermediary representation that is supported by the compiler. The lexical, syntax and semantic analyzers are part of it. The remaining parts belong to the backend, where multiple processes are executed such as machine dependent and independent optimizations, resource allocation, instruction scheduling and target code generation.

Figure 2.1: Compiler Structure.

#### 2.1.2.A Lexical Analyser

This stage is responsible for breaking down the characters received as input from the source file into meaningful sequences called *lexemes*. This *lexemes* are then used to create *tokens* that are associated with them. Each *token* represents a logical piece of the source material, such as variable names and keywords and can contain attributes to transmit necessary extra information for the other stages of the compiler.

Lexical analysers can be implemented as finite automatas, with two main distinct types: Determinitic Finite Automata (DFA) or Nondeterminitic Finite Automata (NFA) [12]. DFAs have each possible transition to a state determined. If a DFA starts in the initial position and is given always the same input, it will always end in the same state. NFAs allow that one input might result in different outcomes, so if it starts in the same initial position and is always given as the same input it can end in different states.

As an example, in Figure 2.2 there can be identified 5 lexemes and consequently 5 tokens, 2 of them identified by the string "i" and "1".

#### 2.1.2.B Syntax Analyser

The *syntax analyser*, also known as *parser*, takes as input the tokens resulting from the previous stage and builds a tree-like object in order to give grammatical structure to the token streams. The goal is to

Figure 2.2: Example of Lexical Analysis.

recover the structure that was previously represented by the tokens. This trees are often represented as having the parent nodes being the operations and leaf nodes the operators and represent the productions that are used, not the order by which they occur.

Programming languages are often specified by Context Free Grammar (CFG). A CFG is a formalism for defining languages and is defined by four components: a set of non-terminals (strings that help define the language generated by the grammar), a set of terminal symbols and a set of productions (the way terminal and non-terminal symbols can be combined). These are used because various *parsers* are able to process this grammars in an efficient way. Some of the well known parsers are the LL, LALR and the Earley parser.

The LL parser uses a top-down approach to parsing: it begins with the start symbol and from there it tries to guess the productions in order to get to the input program. LALR uses the opposite approach, bottom-up. It starts with the input program and tries to reach to the start symbol. The Early parser is more complex, and can be described as a chart parser. It uses the dynamic programming approach and can parse all context-free languages, unlike the previous two.

Using the example of the tokens from Figure 2.2 it is possible to derive the tree presented in fig. 2.3.

#### 2.1.2.C Semantic Analyser

*Semantic analyses* ensures that a program has a well defined meaning. It makes use of the syntax tree to make sure that the source program is consistent with the defined language semantics.

Figure 2.3: Example of Syntax Analysis.

In this step various properties of the program are verified such as the use of variables before declaration, classes not inheriting from existing classes, scope checking and type checking. After this step it is guaranteed that the user's input program is legal. Symbol tables are often used in this step to aid in scope checking.

#### 2.1.2.D Intermediate Code Generation

After the generation of a syntactic and semantically correct tree the next step is to transform it into one or more intermediate representations that are between high-level languages and assembly or some kind of data structure. This representation usually tends to be independent from the frontend as from the backend, so if a compiler is needed for frontend **X** and backends **Y** and **Z** it is only necessary to implement the single frontend and both the backends instead of implementing a compiler for **XY** and another for **XZ**. This strategy is scales very well with an increase in the number of implementations.

Intermediate representations also allow for optimizations that are machine independent and is suitable for instruction selection and register allocation.

Some common intermediate representations include:

- Directed Acyclic Graph (DAG) : As the name suggests, it is a directed graph with no directed cycles. DAG's can be used as a secondary intermediate representation as it is very helpfull in the specific tasks of resources allocation and instruction selection. It is also an efficient method to identify common sub-expressions.

- Three-Address Code (TAC) : Code that uses this representation is characterized by it's expressions having only one or two operators, with one operation in between when there are two. This representation is most suitable for optimization and code generation.

- Static Single-Assignment (SSA) : This representation is similar to TAC but with two distinct features. First, it only allows for a variable with the same name to have a value assigned a single time. Second, because a variable may only have a value assigned once, to solve control flow issues where a variable would have to assume different values depending where the control comes from a φ-function is used to represent that.

#### 2.1.2.E Intermediate Code Optimization

This is one of the most important stages of a compiler and a subject for a lot of studies. The previous stage is focused on translating into an intermediate stage and not on the most optimal way to do it. As a result, a lot of redundancies and overhead are introduced.

The main goals of optimization are to reduce the memory usage of a program, shorten the runtime and use as less power as possible. Optimizations can be categorized into two categories: *local optimizations* and *global optimizations*. Local optimizations aim to make a piece of code as efficient as possible inside a single *basic block*. A basic block is a piece of code that runs from the beginning to the end without any branches, except for the entrance and the exit to the block. Some local optimizations include:

- Common Subexpression Elimination : Eliminates expressions that recalculate unchanged values already obtained before.

- Copy Propagation : Replaces the uses of variable *a*, assigned with variable *b*, by variable *b*.

- **Dead Code Elimination** : Remove assignments that are no longer used throughout the block and are considered dead. A dead variable can originate from the two previous methods.

- Strength Reduction : Replacing operations by simpler ones. One example might be the replacement of a multiplication by 2 for a left shift.

- **Constant Folding** : Evaluation of expressions at compile-time, removing unnecessary computations.

Global Optimizations act on whole functions instead of a single basic block. This type of optimization is more powerful as it has a bigger picture of the whole code. Some global optimizations include:

- Global Dead Code Elimination : Similar to the local one, but can track variables through multiple blocks.

- Global Constant Propagation : Replaces each variable that is known to be a constant by the constant itself.

- **Partial Redundancy Elimination** : Eliminates expressions that are redundant on some paths but not all parts of a program.

#### 2.1.2.F Target Code Generation

Generation of the target machine code. Allocation of resources such as registers and the cache. Because different processors have different characteristics, a good compiler needs to be able to take advantage of peculiar features in order to generate the best performing machine code. Machine specific optimizations are often done during this stage, although some are also done after at the next step. Instruction parallelism, the parallel or simultaneous execution of instructions, is also an opportunity of optimization for compilers when generating the machine code.

#### 2.1.2.G Target Code Optimization

Finally, with the machine code ready, the last optimizations are done.

Currently most processors use some kind of pipeline as part of the architecture. As a result, the order in which the instructions are executed can cause hazards and impact the performance. This problem presents an opportunity of optimization by rescheduling instructions to minimize the time the processor is idle waiting for some operation to complete. To take advantage of multicore processors, compilers can also exploit loop parallelization.

Many caches also share a feature that tries to take advantage of code that exhibit temporal and spacial locality. Temporal locality refers to the fact that memory read recently tends to be read again. Spacial locality refers to the fact that recently read memory will likely have adjacent memory also read. An example for both cases are loops. Compilers can take advantage of this by reordering loops and doing structure peeling, that consists on dividing structures into several ones to increase the number of hits on the cache.

#### 2.1.3 LLVM Infrastructure

The LLVM Infrastructure provides multiple tools and libraries for the implementation of a new compiler or simply create a new extension for an existing one. One feature that sets the LLVM Infrastructure apart from the other compilers is it's structure [13]. Instead of being a monolithic implementation, LLVM separates every stage into different modules and libraries. This way, if it is necessary to create a new frontend, a user only needs to be worried about translating the source file into LLVM IR, assuming that the target they want to compile to is already implemented on the backend.

#### 2.1.3.A Frontend

As a frontend for the C language family, the LLVM Infrastructure offers Clang. Clang was designed as a replacement for the GCC frontend. The goal was to make a frontend that was easier to integrate into an Integrated Development Environment (IDE), with a better performance and that preserved more information about the source code.

The lexical analysis done by Clang splits the source characters into tokens and creates an identifier hash table, to hold the information on the tokens. For the parser, it uses a recursive descent parser. Recursive descent parsers are a kind of top-down parsers that, as the name suggests, starts parsing from the top and reads the input from left to right. Each entity uses procedures to recursively parse the input. It is only during the syntax analysis that an Abstract Syntax Tree (AST) is built and type checking is done. At the end, the AST is converted into another intermediate representation, LLVM IR.

#### 2.1.3.B LLVM IR

LLVM IR is an intermediate representation that separates the frontend from the backend on the Clang/L-LVM compiler. This representations is it's own language and presents resemblances to the assembly language. By using a representation that is both machine and programming language independent, it enables optimizations and transformations without having to change them every time the frontend or backend changes. LLVM IR is a strongly typed SSA based representation that uses an infinite set of temporary registers and is designed to be used in three ways: as a representation in memory for the compiler in the form of C++ classes, as a binary bitcode representation that is saved on disk and can be used by Just-In-Time (JIT) compilers or in a human readable form, that resembles assembly.

LLVM IR files in the human readable form use the ".II" extension and in each individual file it can be identified the following components, present in Figure 2.4:

Figure 2.4: Example of LLVM IR.

• **Module** : *Modules* are the top level structure that hold all other LLVM IR objects of the input file. It contains functions, global variables, additional compilation information and metadata, among others. In Figure 2.4, identified by the number 1, it is the module ID.

- Target Data Layout : A module can specify how data is supposed to be laid out in memory, identified by the number 2 in Figure 2.4. In the example, each specification is separated by the character "-" and the information about the specification is given after the character": ". So the string in the example represents: little-endian form (given by "e"); LLVM names are mangled in the output with the option Executable and Linkable Format (ELF) mangling (given by "m:e"); the size of the pointers, in bits (given by "p:64:64"); the size of the types, in bits (given by "i64:64" and "i128:128"); set of native integer widths for the target Central Processing Unit (CPU), in bits (given by "n64"); the natural alignment of the stack, in bits (given by "S128").

- Target Triple : A string that describes the target host, identified by the number 3 in Figure 2.4. The structure of this string follows the template "ARCHITECTURE-VENDOR-OPERATING\_SYSTEM-ENVIRONMENT", each field separated by the delimiter "-".

- **Functions** : A *function* is a collection of basic blocks that executes some task, like a C language function. Each basic block can have a *label* as it's entry point (stored in a symbol table), has some instructions and finishes with a terminator instruction (branch and return), that shifts the control of the program into another basic block or just ends. Some exterior functions need to be declared with the "declare" keyword and all functions need to be defined with the "define" keyword. In Figure 2.4, the function is identified by the number 4, the definition of the function by number 5 and a basic block inside the function identified by number 6.

- Variables : A module can contain *global* and *local variables*, similarly to the C language. A global variable is available on the whole module and is defined by the "@" character while a local variable is only available inside the function and is defined by the "%" character. In Figure 2.4, identified by the number 5, is the global variable *main*, that is also a function.

- Attribute Groups : As the name suggests, they are a group of attributes that can be associated with various components, such as functions. They are identified by the number 7 in Figure 2.4.

- **Metadata** : *Metadata* allows to convey extra information to the compiler optimizer, code generator and debugging information. Identified by the number 8 in Figure 2.4.

After the generation of the LLVM IR, it begins the process of generating the code for the target machine.

#### 2.1.3.C Backend

The backend is implemented by many LLVM libraries and takes as input the LLVM IR from the previous stage after some machine independent optimizations. The goal is to generate code for a specific target

machine using a target-independent code generator. To do so it uses another intermediate representation in the form of a selection DAG by going through the following processes:

#### · Generating an initial DAG

First the input code is transformed into a selection DAG. Instructions are mapped into DAG nodes, represented by the class *SDNode* that encapsulates the operands represented by the *SDValue* class. After the whole graph is constructed, all the nodes are linked according to the flow of the program and data dependencies. An example of the selection DAG built for the basic block identified by the number 6 in Figure 2.4 can be seen on Figure 2.5.

#### · Optimization of the initial DAG

After the DAG is built, some simple optimizations are performed to simplify it. This includes recognising some instructions and combining them into others. After this optimization the example DAG from Figure 2.5 looks like Figure 2.6.

#### Legalization of selection DAG

Until now, all the steps taken are applicable for any target machine. This is the first stage where the DAG nodes are checked to see if the type and instructions used are supported by the target machine. If a type or instruction is not supported by the target machine, that node is considered illegal.

To legalize a node, the illegal type must be lowered or expanded into other that is supported, or use a custom lowering action, allowing more options on what to do with the illegal type. Operations must be converted into others or a collection of other operations that do the same function and are supported. After the types of the operands and the instructions are legal, the node is considered legal and good to advance to the next step.

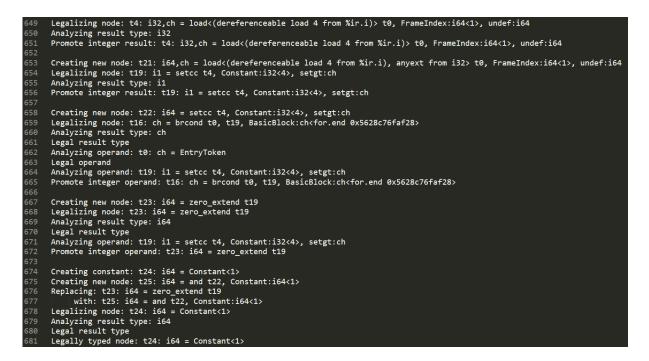

```

Creating constant: t2: i64 = Constant<0>

Creating new node: t3: i64 = undef

Creating new node: t4: i32,ch = load<(dereferenceable load 4 from %ir.i)> t0, FrameIndex:i64<1>, undef:i64

Creating constant: t5: i32 = Constant<5>

547

Creating new node: t7: i1 = setcc t4, Constant:i32<5>, setlt:ch

548

Creating constant: t8: i1 = Constant<-1>

Creating new node: t9: i1 = xor t7, Constant:i1<-1>

Creating new node: t11: ch = brcond t0, t9, BasicBlock:ch<for.end 0x5628c76faf28>

Creating new node: t13: ch = br t11, BasicBlock:ch<for.body 0x5628c76fad78>

Initial selection DAG: %bb.1 'main:for.cond'

SelectionDAG has 14 nodes:

t0: ch = EntryToken

t2: i64 = Constant<0>

t4: i32,ch = load<(dereferenceable load 4 from %ir.i)> t0, FrameIndex:i64<1>, undef:i64

t7: i1 = setcc t4, Constant:i32<5>, setlt:ch

t9: i1 = xor t7, Constant:i1<-1>

t11: ch = brcond t0, t9, BasicBlock:ch<for.end 0x5628c76faf28>

t13: ch = br t11, BasicBlock:ch<for.body 0x5628c76fad78>

```

```

Figure 2.5: Example of selection DAG after being built.

```

```

600 Optimized lowered selection DAG: %bb.1 'main:for.cond'

601 SelectionDAG has 11 nodes:

602 t0: ch = EntryToken

603 t4: i32,ch = load<(dereferenceable load 4 from %ir.i)> t0, FrameIndex:i64<1>, undef:i64

604 t19: i1 = setcc t4, Constant:i32<4>, setgt:ch

605 t16: ch = brcond t0, t19, BasicBlock:ch<for.end 0x5628c76faf28>

606 t13: ch = br t16, BasicBlock:ch<for.body 0x5628c76fad78>

```

Figure 2.6: Example of initial DAG after being optimized.

The legalization of the DAG is done in multiple steps, with optimization steps done in between and after it is complete.

An example of the legalization step for the operands and operations, following the example of Figure 2.6, is present in Figure 2.7. The final result of the legalization step is presented in Figure 2.8.

#### Instruction Selection

Here the generic target independent instructions used within LLVM IR are replaced by target specific instructions. The input is a legal DAG from the previous stage.

On the backend, each target defines what instructions it supports and what patterns should be matched to each instruction. At this stage, the compiler takes this patterns and matches every single generic instruction or intrinsic function into an instruction supported by the target, by creating a new DAG with the native instructions. A pattern doesn't need to be just a simple one to one replacement. It can take a sequence of instructions and replace them all by another one that serves the same function. As an example, if the target supports fused multiplication and addition, it can take both instructions together and replace them by the target single instruction.

Following the example of Figure 2.8, the instruction selection process is represented in Figure 2.9 and the resulting DAG after the selection in Figure 2.10.

#### · Scheduling and emitting machine instruction

At this stage the compiler takes the DAG with the target machine instructions and gives them an order that depends on the target machine constraints. After all instructions are scheduled, the selection DAG is discarded and is converted into a list of machine instructions.

Following the example of Figure 2.10, a schedule can be found in Figure 2.11 and the emitted machine instructions in Figure 2.12.

#### Register Allocation

```

Legalizing node: t18: ch = setgt

Analyzing result type: ch

Legal result type

612

Legally typed node: t18: ch = setgt

Legalizing node: t17: i32 = Constant<4>

Analyzing result type: i32

Promote integer result: t17: i32 = Constant<4>

Creating constant: t20: i64 = Constant<4>

Legalizing node: t20: i64 = Constant<4>

Analyzing result type: i64

Legal result type

Legally typed node: t20: i64 = Constant<4>

Legalizing node: t12: ch = BasicBlock<for.body 0x5628c76fad78>

625

Analyzing result type: ch

Legal result type

Legally typed node: t12: ch = BasicBlock<for.body 0x5628c76fad78>

Legalizing node: t10: ch = BasicBlock<for.end 0x5628c76faf28>

Analyzing result type: ch

Legal result type

Legally typed node: t10: ch = BasicBlock<for.end 0x5628c76faf28>

```

(a) Operators Legalization.

(b) Operation Legalization.

Figure 2.7: Example of DAG legalization.

| 915 | Optimized legalized selection DAG: %bb.1 'main:for.cond'                                                |

|-----|---------------------------------------------------------------------------------------------------------|

| 916 | SelectionDAG has 11 nodes:                                                                              |

| 917 | t0: ch = EntryToken                                                                                     |

| 918 | t29: i64,ch = load<(dereferenceable load 4 from %ir.i), sext from i32> t0, FrameIndex:i64<1>, undef:i64 |

| 919 | t22: i64 = setcc t29, Constant:i64<4>, setgt:ch                                                         |

| 920 | t16: ch = brcond t0, t22, BasicBlock:ch <for.end 0x5628c76faf28=""></for.end>                           |

| 921 | t13: ch = br t16, BasicBlock:ch <for.body 0x5628c76fad78=""></for.body>                                 |

Figure 2.8: Example of final DAG after legalization.

| 924 | ===== Instruction selection begins: %bb.1 'for.cond'                                                                 |  |  |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 925 |                                                                                                                      |  |  |  |  |  |  |  |  |

| 926 | ISEL: Starting selection on root node: t13: ch = br t16, BasicBlock:ch <for.body 0x5628c76fad78=""></for.body>       |  |  |  |  |  |  |  |  |

| 927 | ISEL: Starting pattern match                                                                                         |  |  |  |  |  |  |  |  |

| 928 | Initial Opcode index to 78437                                                                                        |  |  |  |  |  |  |  |  |

| 929 | Morphed node: t13: ch = PseudoBR BasicBlock:ch <for.body 0x5628c76fad78="">, t16</for.body>                          |  |  |  |  |  |  |  |  |

| 930 | ISEL: Match complete!                                                                                                |  |  |  |  |  |  |  |  |

| 931 |                                                                                                                      |  |  |  |  |  |  |  |  |

| 932 | ISEL: Starting selection on root node: t16: ch = brcond t0, t22, BasicBlock:ch <for.end 0x5628c76faf28=""></for.end> |  |  |  |  |  |  |  |  |

| 933 | ISEL: Starting pattern match                                                                                         |  |  |  |  |  |  |  |  |

| 934 | Initial Opcode index to 32704                                                                                        |  |  |  |  |  |  |  |  |

| 935 | OpcodeSwitch from 32709 to 32745                                                                                     |  |  |  |  |  |  |  |  |

| 936 | TypeSwitch[i64] from 32746 to 33098                                                                                  |  |  |  |  |  |  |  |  |

| 937 | Skipped scope entry (due to false predicate) at index 33103, continuing at 33123                                     |  |  |  |  |  |  |  |  |

| 938 | Skipped scope entry (due to false predicate) at index 33124, continuing at 33144                                     |  |  |  |  |  |  |  |  |

| 939 | Skipped scope entry (due to false predicate) at index 33145, continuing at 33165                                     |  |  |  |  |  |  |  |  |

| 940 | Skipped scope entry (due to false predicate) at index 33166, continuing at 33186                                     |  |  |  |  |  |  |  |  |

| 941 | Skipped scope entry (due to false predicate) at index 33187, continuing at 33207                                     |  |  |  |  |  |  |  |  |

| 942 | Skipped scope entry (due to false predicate) at index 33208, continuing at 33228                                     |  |  |  |  |  |  |  |  |

| 943 | Morphed node: t16: ch = BLT Constant:i64<4>, t29, BasicBlock:ch <for.end 0x5628c76faf28="">, t0</for.end>            |  |  |  |  |  |  |  |  |

| 944 | ISEL: Match complete!                                                                                                |  |  |  |  |  |  |  |  |

Figure 2.9: Example of the instruction selection process.

Up until now it was assumed that there could be as many virtual registers as necessary. However, real machine only have a limited number of physical registers. During this stage, the compiler assigns physical registers to the virtual register. If there are not enough physical registers to assign, the compiler moves the value of one of the registers to the main memory, in a process called *spilling*.

LLVM allocates registers in two different ways: *direct mapping* and *indirect mapping*. In the first case, the classes associated with the physical registers and machine operands are responsible for the allocation. On the second case, the class associated with the virtual registers are responsible for the allocation. LLVM also makes available four register allocation techniques: *Fast*, where it allocates register on a basic block level and tries to keep the values on the registers to reuse them; *Basic*, an incremental approach to register allocation, that makes use of live range analysis (where a variable has a live value during the execution of the program) and spill weight for prioritization of virtual registers; *Greedy*, an optimized version of the *Basic* method and incorporates a global live range splitting; *PBQP*, a Partitioned Boolean Quadratic Programming (PBQP) based register allocator, that represents the allocation of registers as a PBQP problem and solves it using a PBQP solver.

Following the example of Figure 2.12, the allocation of registers using the greedy method is

| 978   | ===== Instruction selection ends:                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 979   | Selected selection DAG: %bb.1 'main:for.cond'                                                                                                                |

| 980 🔻 | SelectionDAG has 11 nodes:                                                                                                                                   |

| 981 🔻 | t0: ch = EntryToken                                                                                                                                          |

| 982   | t34: i64 = ADDI Register:i64 \$x0, TargetConstant:i64<4>                                                                                                     |

| 983   | t29: i64,ch = LW <mem:(dereferenceable %ir.i)="" 4="" from="" load=""> TargetFrameIndex:i64&lt;1&gt;, TargetConstant:i64&lt;0&gt;, t0</mem:(dereferenceable> |

| 984   | t16: ch = BLT t34, t29, BasicBlock:ch <for.end 0x5628c76faf28="">, t0</for.end>                                                                              |

| 985   | <pre>t13: ch = PseudoBR BasicBlock:ch<for.body 0x5628c76fad78="">, t16</for.body></pre>                                                                      |

Figure 2.10: Example of final DAG after instruction selection.

\*\*\* Final schedule \*\*\*

SU(2): t29: i64,ch = LW<Mem:(dereferenceable load 4 from %ir.i)> TargetFrameIndex:i64<1>, TargetConstant:i64<0>, t0

1064

SU(3): t34: i64 = ADDI Register:i64 \$x0, TargetConstant:i64<4>

1066

1067

SU(1): t16: ch = BLT t34, t29, BasicBlock:ch<for.end 0x5628c76faf28>, t0

1068

1069

SU(0): t13: ch = PseudoBR BasicBlock:ch<for.body 0x5628c76fad78>, t16

Figure 2.11: Example of instruction scheduling.

represented in Figure 2.13.

# Code emission

The final step is to emit the machine code into a binary format or assembly. The compiler takes as input the *Machine Instructions* from the previous steps and lowers them into *Machine Code Instructions*, used by the *Machine Code* layer. One of the advantages LLVM has over traditional compilers is that, usually, traditional compilers output only the assembly code and then need an external assembler to produce the object file. However, LLVM uses its own assembler so it can print directly into binary form and with some wraps, to object file. This features allows to save time and guarantees that the output in textual format will be the same as the output in binary formats.

# 2.2 Vector Extensions

In this section it will be given an overview of the processing strategy SIMD and some popular vectorial extensions, such as the RISCV "V" vector extension and the Arm SVE. It will also be discussed the pros and cons of using such strategies and extensions. To present an alternative, it will be introduced the streaming paradigm and UVE, an experimental ISA extension that makes use of data streams.

# 2.2.1 SIMD and Scalable Vectorial Extensions

The use of SIMD based extensions and scalable vectorial extensions aim to take advantage of Data Level Parallelism (DLP) by processing multiple data while only emitting one single processing instruction. To do so, the data to be processed if aggregated into vectors, that then go through some processing unit, executing the same operations on all the data.

| 2162 | bb.1.for.cond:                                                   |

|------|------------------------------------------------------------------|

| 2163 | ; predecessors: %bb.0, %bb.3                                     |

| 2164 | successors: %bb.2, %bb.4                                         |

| 2165 |                                                                  |

| 2166 | %1:gpr = LW %stack.1.i, 0 :: (dereferenceable load 4 from %ir.i) |

| 2167 | %2:gpr = ADDI \$x0, 4                                            |

| 2168 | BLT killed %2:gpr, killed %1:gpr, %bb.4                          |

| 2169 | PseudoBR %bb.2                                                   |

Figure 2.12: Example of emitting machine instruction.

| 2666 | selectOrSplit GPR:%3 [320r,336r:0) 0@320r weight:INF w=INF                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2667 | AllocationOrder(GPR) = [ \$x10 \$x11 \$x12 \$x13 \$x14 \$x15 \$x16 \$x17 \$x5 \$x6 \$x7 \$x28 \$x29 \$x30 \$x31 \$x9 \$x18 \$x19 \$x20 \$x21 \$x22 \$x23 \$x24 \$x25 \$x26 |

|      | \$x27 \$x1 ]                                                                                                                                                               |

| 2668 | hints: \$x10                                                                                                                                                               |

| 2669 | assigning %3 to \$x10: X10 [320r,336r:0) 0@320r                                                                                                                            |

| 2670 |                                                                                                                                                                            |

| 2671 | selectOrSplit GPR:%1 [96r,128r:0) 0@96r weight:9.259259e-03 w=9.259259e-03                                                                                                 |

| 2672 | assigning %1 to \$x10: X10 [96r,128r:0) 0@96r                                                                                                                              |

| 2673 |                                                                                                                                                                            |

| 2674 | selectOrSplit GPR:%2 [112r,128r:0) 0@112r weight:INF w=INF                                                                                                                 |

| 2675 | assigning %2 to \$x11: X11 [112r,128r:0) 0@112r                                                                                                                            |

| 2676 |                                                                                                                                                                            |

| 2677 | selectOrSplit GPR:%4 [176r,192r:0) 0@176r weight:INF w=INF                                                                                                                 |

| 2678 | assigning %4 to \$x10: X10 [176r,192r:0) 0@176r                                                                                                                            |

| 2679 |                                                                                                                                                                            |

| 2680 | selectOrSplit GPR:%5 [240r,256r:0) 0@240r weight:INF w=INF                                                                                                                 |

| 2681 | assigning %5 to \$x10: X10 [240r,256r:0) 0@240r                                                                                                                            |

| 2682 |                                                                                                                                                                            |

| 2683 | selectOrSplit GPR:%6 [256r,272r:0) 0@256r weight:INF w=INF                                                                                                                 |

| 2684 | assigning %6 to \$x10: X10 [256r,272r:0) 0@256r                                                                                                                            |

Figure 2.13: Example of register allocation using the greedy method.

However, the way it is used to achieve such goals is different from strategy to strategy and from extension to extension. On the following chapters, it is given a description of the strategy used by SIMD and scalable vectorial extensions and some of the extensions designed using such strategies.

# 2.2.1.A SIMD

SIMD extensions make use of fixed length vectors to process multiple data with a single instruction, taking advantage of DLP. In order to do so, the processing units must be able to handle multiple data and are referred to as SIMD units. To take advantage of this units it is also important to combine multiple loads and stores accesses. This can be achieved with contiguous memory accesses and with arrays that are aligned in memory. This solutions are great for specific problems that can be vectorized and have a huge amount of data to be processed but for other applications that don't share these characteristics it can be detrimental. Because it uses larger registers it also consumes more energy.

Two extensions that make use of SIMD instruction are the x86 SSE/AVX extension by Intel [4, 5] and the NEON extension by Arm [6]. This two extensions are featured in two different instruction sets architectures, the first in a Complex Instruction Set Computer (CISC) based processor and the second in a Reduced Instruction Set Computer (RISC) based processor. Streaming SIMD Extensions (SSE) and AVX are both designed by Intel for the x86 instruction set architecture. The first SIMD based extension released by Intel that started it all was the MMX instruction set. This extension supported registers 64

bits wide but could not operate on floating point and SIMD data at the same time, because it reused the x87 floating point registers. To improve on this extension, in 1999, Intel released their next extension, SSE. This extension had a new 128 width bit independent register file that could already support floating point operations. The next iteration on this extension came in the form of SSE2, SSE3 and SSE4, with the addition of double-precision floating point operations and a lot of supporting instructions. In 2011, Intel released AVX, that widened the data path from 128 bit registers to 256 and three-operand SIMD instructions. Following that it came AVX2 and, the latest extension, AVX-512, that again extended the registers from 256 bits to 512 bits.

The NEON extension is designed by Arm and is intended to accelerate multimedia applications, signal and video processing, among others. It is composed of 32 64-bit separate registers capable of storing 64 bits (doubleword) and 128 bits (quadword) and NEON instructions support 8-bit, 16-bit, 32-bit and 64-bit signed and unsigned integers as also 32-bit single-precision floating point elements. These instructions perform memory accesses, data copying between NEON and general purpose registers, data type conversion and data processing.

By comparing both approaches, Intel gets the wider registers with the AVX-512 extension, capable of storing 512 bits, in comparison to Arm's NEON extension of only 128 bits, leading to being able to operate on more data at the same time, and thus reducing the number of clock cycles necessary and execution time. However that comes at a cost, by consuming more energy and occupying more space. SIMD extensions provides a benefit by operating on large amounts of data at the same time but it still has some problems. The one that stands out immediately is the size of the register being a fixed number. This forces developers to design implementations for many different sized registers architectures, otherwise the application may not have the same performance by having vectors too wide or to narrow, leading to a waste of vector space or the emission of too many load and store instructions, respectively.

### 2.2.1.B Scalable Vectorial Extensions

Scalable vector extensions appear as an attempt to mitigate the disadvantages of the SIMD based extensions, by removing the fixed limit on the size of the vectors. This strategy removes the necessity of designing different implementations depending on the target's vector size and also removes the necessity to worry about some edge cases, with only having to scale the vector in order to solve them. The main extensions that share this ideology are RISC-V "V" extension [14] and Arm's SVE [7].

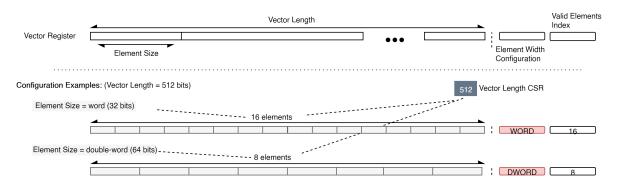

The RISC-V "V" vector extension defines that the size of a vector element, ELEN, must be higher or equal to 8 bits and a power of 2, and the size of a vector register, VLEN, must be higher or equal to the size ELEN and should also be a power of 2. This extension adds 32 vector registers and 7 Control Status Registers (CSR), that allow to control the vector starting position, length, data type register and vector register length in run-time. This extension also supports vector masking, that allows finer control over which elements inside the vectors are processed.

Arm's SVE extension was designed with High Performance Computing (HPC) and Machine Learning (ML) applications in mind. This extension includes 32 new scalable vector registers with their length being implementation dependent, from 128 to 2048 bits, in increments of 128 bits. The data elements can range from 8 bits to 16, 32 and 64 bits. It also features 16 scalable predicate registers, that allow per lane predication and a more selective choice of what data elements are going to be processed, same as RISC-V "V" extension, although only 8 are used for general memory and arithmetic operations, as a way to mitigate the predicate register pressure observed in other predicate-centric architectures. It also features a special-purpose first-fault register. Following SVE, it came SVE2, that shares most of functionality with SVE but it extends the instruction set to cover more data-processing domains, such as computer vision, multimedia and web serving.

Both of these extension function in a similar way; they both need to define the vector and elements length, a predicate register, and then operate, with a single instruction, over this vectors. RISC-V's "V" extension is able to configure the scalable vectors in a more refined way comparing to Arm's SVE extension. The use of scalable vectors eases the problem that was the fixed limit of SIMD based extensions, and also presents better results when dealing with edge case scenarios. However, both these extension still need to rely on instructions to calculate memory accesses and to emit loop iteration control instructions, adding on to the pipeline. Both Arm's SVE and RISC-V "V" extension are already supported in LLVM [15–17].

# 2.3 Unlimited Vector Extension

UVE is an experimental ISA extension proposed by Domingos et al. [2] to overcome the disadvantages described in the previous scalable extensions. In order to do so, it implements a streaming engine to decouple the memory accesses from the main processing pipeline and makes use of data streams. To implement the data streams, UVE needs to be able to represent various memory accesses, from simple linear iterations to indirect memory accesses.

As implementing compiler support for this extension is the main focus of this work, UVE will be described with great detail on the next sections, to be able to comprehend some of the decisions done on the implementation.

# 2.3.1 Memory Access Description

In order for UVE to implement streams, it needs to be able to describe them. To describe a stream, UVE makes use of memory pattern description through descriptors. The base of the descriptor is given by

Neves et al. [1,18,19] works, where it is specified that by using a combination of descriptors any regular memory access pattern can be represented. The address sequence can be represented as an affine function, given by:

$$y(X) = y_{base} + \sum_{k=0}^{\dim_y} x_k \times stride_k, \text{ with } x_k \in [\alpha_k, \beta_k], \ X = \{x_0 \cdots x_{\dim_y}\}$$

(2.1)

where each stream access y(X) is described by the sum of the base address  $(y_{base})$  with  $dim_y$  pairs, described by their size  $(x_k)$  and stride  $(stride_k)$ . This representation is capable of describing any pattern but can introduce a huge amount of descriptors.

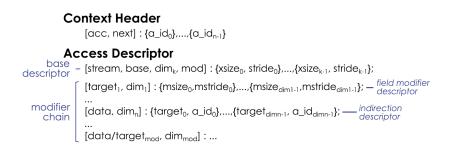

A form of describing memory accesses that circumvents this problem is proposed by Neves et al. in Figure 2.14.

This specification is composed of a context header, a base descriptor and a modifier chain. The base descriptor is composed of a stream identification (*stream*), memory base address (*base*), the number of dimensions it has ( $dim_y$ ), the number of modifiers (*mod*) and the description of each dimension, given by its size (*xsize*) and stride (*stride*). The encoded pairs configured more to the right (with higher index) represent higher or outermost dimensions. This base description allows for the representation of any N-dimension memory description but is would use too many dimensions to do so.

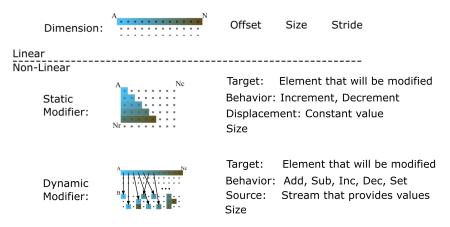

The modifier chain allows to represent non-linear memory patterns, and consequently decrease the number of descriptors necessary to represent such memory accesses. Modifiers are applied to the base descriptor every time after a complete iteration of the corresponding dimension pair it is associated with. Modifiers descriptors are divided into two categories: field modifier descriptors and indirect descriptors.

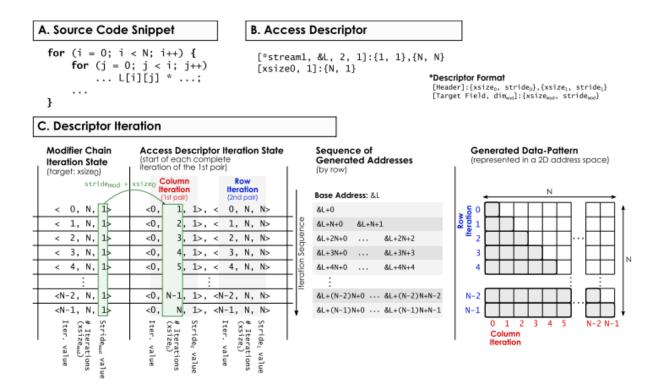

Field modifier descriptors are as described in Figure 2.14 and contain the target of the modifier  $(target_{mod})$ , the dimension of the modifier  $(dim_{mod})$  and then a pair that includes the size of the modifier (msize) and its stride (mstride). A use of this modifier is exemplified in Figure 2.15. In this example the source code pretends to make a triangular matrix memory access. To implement this pattern as a descriptor, a base descriptor is defined with two dimensions, the first by  $\{1, 1\}$  that iterates over the elements on a row and the second by  $\{N, N\}$  that jumps over the rows N times. After that, a field modifier

Figure 2.14: Descriptor specification proposed by Neves et al. [1].

descriptor is defined targeting *xsize*0 (the size of dimension 1 from the base descriptor) with dimension 1, characterized with size N and stride 1. This modifier will change the size of the first dimension on the base descriptor every full iteration, increasing it by 1 unit, leading to a triangular matrix access.

Figure 2.15: Access Descriptor encoding a triangular matrix access by Neves et al. [1].

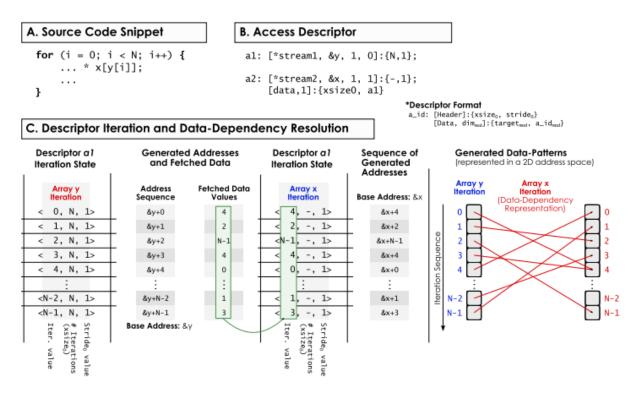

Indirect descriptors can be used to encode data dependencies between descriptors. To describe one, it is necessary to specify the *data* label, the dimension of the modifier  $(dim_{mod})$  and the pairs composed by the target (target) and stream descriptor  $(a_{-}id)$ . The stream descriptor in the pair emphasises the data dependency between the descriptors. An example of this modifier is given in Figure 2.16. In this example, on the source code snippet, the *y* variable is being iterated every loop and used as an index for the *x* variable, creating a data dependency between *y* and *x*. So, the *y* variable can be represented as a descriptor by simply defining its only dimension, of size N and stride 1. To describe the *x* variable it is necessary to first define a descriptor that has a dummy dimension pair, of undefined size and stride 1. This is because the size is going to be defined by the size of the descriptor used in the modifier. The modifier defines a pair, targeting the *xsize*0 field and the descriptor *a*1, referring to the variable *y*. With this definition, every time the descriptor *a*1 produces a value, that value will be used as an offset by descriptor *a*2 to create indirect memory accesses.

Figure 2.16: Access Descriptor encoding an indirect memory indexation by Neves et al. [1].

# 2.3.2 UVE Streams

In UVE, a stream is a continuous flow of data that makes use of descriptors to describe memory patterns for its configuration and manipulation. The descriptors used in UVE take inspiration from the ones described previously but are made simpler for an easier integration with for loops, the main target this extension.

The linear patterns used in UVE resemble the base descriptor in Figure 2.14, by using three parameters to describe a dimension: offset, equivalent to *base* from the base descriptor and size and stride, that formed a pair for defining dimensions on the base descriptor. It is also necessary to detail the data-type, to know when accessing from memory how many bits can be read. The conjunction of this parameters, as before, defines a descriptor, that is a representation of a stream. To add more dimensions to the previously defined descriptor, one only needs to add a new descriptor of top, by following the same procedure as for the first one.

In order to represent more complex memory access patterns, UVE also makes use of modifiers. The modifier must be associated to a single dimension. Each one is characterized by the target the modifier wants to change (a choice between offset, size and stride from the aforementioned linear pattern), the behaviour it wants to implement (increment and decrement), the amount it will increase or decrease the targeted parameter and the size of the modifier (the number of iterations it will perform this modification).

Lastly, to represent indirect accesses UVE uses the same approach as the previous modifiers, however, since indirect modifiers represent a data dependency between two variables, instead of selecting the amount it will modify the targeted dimension this data will come from a stream. As such, the definition of an indirect modifier is done by selecting the target it will modify, the behaviour of such modification (add, subtract, increment, decrement and set), the source stream for the implementation of such behaviours and the size of the modifier, with the same purpose as in the last one.

A summary of the descriptors and modifiers detailed previously is shown in Figure 2.17.

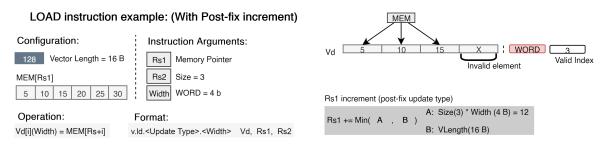

Lastly, to be able to use descriptors with multiple dimensions and modifiers associated with them UVE implements a list. Each node of this list can have, at most, one dimension and one modifier and the list is built from the inner most loop, as the head of the list, to the outer most loop. This list is connected and directed, to imply order between the nodes. A way to build such ordered list can be done by issuing every single dimension and modifier with one instruction, building upon the latter one.

# 2.3.3 UVE Instruction Set Architecture

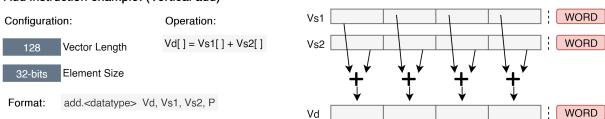

After defining the concept of descriptor, and how they are used to describe a stream, the UVE instructions make use of them to define their architecture and the instructions supported in the ISA.

UVE is implemented as an extension to RISC-V, leveraging the fact it is an open-source architecture. It makes use of a streaming engine as a way to decouple the memory accesses from the main processing pipeline. This way, it can save time by letting the streaming unit deal with some memory operations and removing some memory instructions from the main processing unit.