## Vector Multiply-Accumulate Unit for Transprecision Computing

## Luís Miguel Marques Crespo

Thesis to obtain the Master of Science Degree in

## **Electrical and Computer Engineering**

Supervisors: Prof. Nuno Filipe Valentim Roma Prof. Pedro Filipe Zeferino Aidos Tomás

### **Examination Committee**

Chairperson: Doutora Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Prof. Nuno Filipe Valentim Roma Member of the Committee: Prof. Horácio Cláudio de Campos Neto

November 2021

# **Declaration**

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

## **Acknowledgments**

Gostaria de começar por agradecer aos meus pais, por todo o apoio, carinho e educação que sempre me proporcionaram. Agradeço à minha namorada, Inês, por estar sempre presente e por todos os momentos de alegria e afeto. Ao meu irmão, agradeço todas as horas de companhia e amizade. Um obrigado aos amigos que conheci e me acompanharam ao longo deste árduo percurso e por todos os bons e maus momentos que partilhámos.

Agradeço aos meus orientadores Prof. Nuno Roma e Prof. Pedro Tomás, os quais me deram um apoio essencial na elaboração deste trabalho e me desafiaram a ir mais longe. Quero deixar um especial agradecimento ao Nuno Neves, por toda a paciência, disponibilidade e apoio no desenvolvimento desta tese. Sem ele, este trabalho não seria possível.

This work was partially supported by national funds through Fundação para a Ciência e a Tecnologia (FCT) under projects UIDB/CEC/50021/2020, PTDC/EEI-HAC/30485/2017 and PCIF/MPG/0051/2018.

# Abstract

Transprecision computing is currently viewed as a potential paradigm to increase performance and energy efficiency in modern computing systems, by allowing the floating-point precision to be tuned to the application requirements. However, most attempts at deploying transprecision architectures often rely on instantiations of multiple different modules to provide support for different precisions. To counteract this issue, recent solutions have started to explore variable-precision units with dynamic datapaths that can support different floating-point precisions with the same hardware resources. This approach not only provides for significant area reductions but also enables straightforward Single Instruction, Multiple Data (SIMD) capabilities. Despite their success, most architectures often have to rely on the IEEE-754 standard and lack support for low-precision arithmetic. To that end, the recent Posit number system presents a non-uniform encoding that is particularly well-suited for low-precision arithmetic. However, for higher precisions, it often incurs in prohibitive hardware requirements. In this Thesis, a new unified Posit/IEEE-754 Vector Multiply-Accumulate Unit is proposed, with variable-precision and SIMD computing capabilities. It implements a fully vectorized datapath with multiple-precision arithmetic capabilities and unique shared support for both the Posit and IEEE-754 formats. The proposed unit was fully described in RTL by considering Application Specific Integrated Circuit (ASIC) and Field Programmable Gate Array (FPGA) implementations. Results show that the proposed unit requires 50% less area and  $2.9 \times$  less power consumption when compared to a reference transprecision setup.

## **Keywords**

Floating-point Arithmetic, Posit Number System, IEEE-754, Variable-Precision, SIMD, Transprecision Computing

# Resumo

O paradigma de computação em transprecisão é atualmente visto, como uma potencial solução para aumentar o desempenho e a eficiência energética em sistemas de computação modernos, através do ajuste da precisão dos números de vírgula flutuante aos requisitos da aplicação. No entanto, a maior parte das implementações resultam da utilização de diversos módulos para suportar as diferentes precisões. Para contrariar esta tendência, arquiteturas mais recentes implementam unidades de precisão variável, com datapaths dinâmicos que suportam diferentes precisões com os mesmos recursos de hardware. Esta abordagem, permite reduções de área como também possibilita explorar esquemas de Single Instruction, Multiple Data (SIMD). No entanto, apesar do seu sucesso, estas arquiteturas tendem apenas a suportar o standard IEEE-754, que não contempla aritmética de baixa precisão. Neste sentido, o recente sistema numérico Posit apresenta uma codificação não uniforme que é particularmente adequada para a aritmética de baixa precisão. No entanto, para precisões mais elevadas, o Posit toma proporções de hardware demasiado elevadas. Assim, esta Tese propõe uma nova unidade Vetorial de Multiplicação-Acumulação unificada para os formatos Posit e IEEE-754, oferecendo precisão variável e recursos de computação SIMD. A unidade é totalmente vetorizada, com aritmética de precisão variável e suporte para os formatos Posit e IEEE-754. A unidade proposta, foi inteiramente descrita em RTL e implementada em Application Specific Integrated Circuit (ASIC) e em dispositivos Field Programmable Gate Array (FPGA). Os resultados mostram que a unidade proposta, quando comparada a uma referência de transprecisão, obtém uma área 50% inferior e requere consumo de potência 2.9× menor.

## **Palavras Chave**

Aritmética de Vírgula Flutuante, Formato Numérico Posit, IEEE-754, Precisão Variável, SIMD, Computação de Transprecisão

# Contents

| 1 | Intro | duction                              | 1 |

|---|-------|--------------------------------------|---|

|   | 1.1   | Motivation                           | 2 |

|   | 1.2   | Objectives                           | 3 |

|   | 1.3   | Contributions                        | 4 |

|   | 1.4   | Thesis Outline                       | 4 |

| 2 | Bac   | ground                               | 5 |

|   | 2.1   | Floating-point formats               | 6 |

|   |       | 2.1.1 IEEE-754 standard              | 7 |

|   |       | 2.1.2 Posit Format                   | 0 |

|   | 2.2   | Floating-point arithmetic structures | 4 |

|   |       | 2.2.1 IEEE-754 Format Decoding       | 5 |

|   |       | 2.2.2 Posit Decode                   | 5 |

|   |       | 2.2.3 Addition/subtraction           | 6 |

|   |       | 2.2.4 Multiplication and Division    | 7 |

|   |       | 2.2.5 Fused Multiply-Add             | 8 |

|   |       | 2.2.6 Multiply-Accumulate 1          | 9 |

|   |       | 2.2.7 IEEE-754 Format Encoding       | 0 |

|   |       | 2.2.8 Posit Format Encoding          | 0 |

|   | 2.3   | Floating-point Hardware Units        | 1 |

|   | 2.4   | Discussion                           | 4 |

|   | 2.5   | Summary 2                            | 5 |

| 3 | Prop  | osed Architecture 2                  | 7 |

|   | 3.1   | Proposed Architecture Overview       | 8 |

|   | 3.2   | Arithmetic Vectorization             | 0 |

|   |       | 3.2.1 Vector Data Formats            | 0 |

|   |       | 3.2.2 Vector Arithmetic Operators    | 3 |

|   | 3.3   | Proposed Vector MAC Unit             | 9 |

|    |       | 3.3.1 Control Signals                   | 0  |

|----|-------|-----------------------------------------|----|

|    |       | 3.3.2 Decode                            | 1  |

|    |       | 3.3.3 Multiply                          | 6  |

|    |       | 3.3.4 Quire Arithmetic                  | 8  |

|    |       | 3.3.5 Normalize                         | 5  |

|    |       | 3.3.6 Encode                            | 7  |

|    | 3.4   | Summary                                 | ;1 |

| 4  | Impl  | mentation Results 6                     | 63 |

|    | 4.1   | Evaluation Methodology                  | 64 |

|    | 4.2   | mplementation Results                   | 65 |

|    |       | 4.2.1 ASIC Implemenatation              | 5  |

|    |       | 4.2.2       FPGA Implementation       6 | 8  |

|    | 4.3   | Summary                                 | '1 |

| 5  | Con   | lusion 7                                | '3 |

|    | 5.1   | Future Work                             | '5 |

| Bi | bliog | aphy 7                                  | 7  |

| A  | Rad   | a-4 Booth Multiplier 8                  | 33 |

# **List of Figures**

| 2.1                                      | Binary IEEE-754 floating-point format [1].                                                                                                                                                                                                                                                                                          | 7                          |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.2                                      | Structure of: (a) FP32, (b) FP16 and (c) bfloat16 [2]                                                                                                                                                                                                                                                                               | 9                          |

| 2.3                                      | Posit format highlighting its components (sign, regime, exponent and fraction) [3]                                                                                                                                                                                                                                                  | 10                         |

| 2.4                                      | Accuracy comparison of FP16 and posit $<16,1>.$                                                                                                                                                                                                                                                                                     | 13                         |

| 2.5                                      | Binary quire format [4]                                                                                                                                                                                                                                                                                                             | 13                         |

| 2.6                                      | Floating-point unit structure.                                                                                                                                                                                                                                                                                                      | 14                         |

| 2.7                                      | Decision tree representation of the IEEE-754 special encodings.                                                                                                                                                                                                                                                                     | 15                         |

| 2.8                                      | Typical posit decoding module.                                                                                                                                                                                                                                                                                                      | 16                         |

| 2.9                                      | Floating-point addition/subtraction structure                                                                                                                                                                                                                                                                                       | 17                         |

| 2.10                                     | Floating-point multiplication/division structure.                                                                                                                                                                                                                                                                                   | 18                         |

| 2.11                                     | Floating-point FMA structure.                                                                                                                                                                                                                                                                                                       | 18                         |

| 2.12                                     | MAC structure with Long Adder and Long Shifter                                                                                                                                                                                                                                                                                      | 19                         |

| 2.13                                     | Typical posit encoding module.                                                                                                                                                                                                                                                                                                      | 21                         |

| 3.1                                      | (A) variable-precision vs proposed (B) vector datapath configuration scheme                                                                                                                                                                                                                                                         | 29                         |

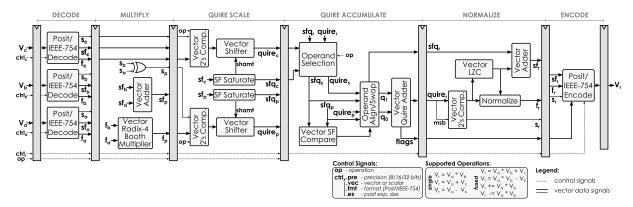

| 3.2                                      | Proposed Posit/IEEE-754 unit architecture diagram.                                                                                                                                                                                                                                                                                  | 30                         |

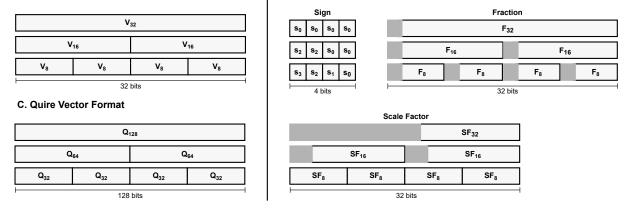

| 3.3                                      | Vector data formats.                                                                                                                                                                                                                                                                                                                | 31                         |

| 3.4                                      |                                                                                                                                                                                                                                                                                                                                     |                            |

|                                          | Adopted quire vector formats                                                                                                                                                                                                                                                                                                        | 32                         |

| 3.5                                      | Adopted quire vector formats                                                                                                                                                                                                                                                                                                        | 32<br>34                   |

| 3.5<br>3.6                               |                                                                                                                                                                                                                                                                                                                                     |                            |

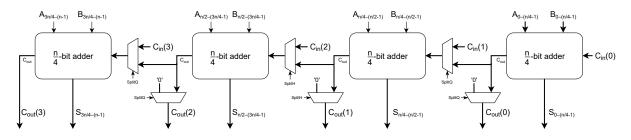

|                                          | Vectorized adder structure.                                                                                                                                                                                                                                                                                                         | 34                         |

| 3.6                                      | Vectorized adder structure.                                                                                                                                                                                                                                                                                                         | 34<br>34                   |

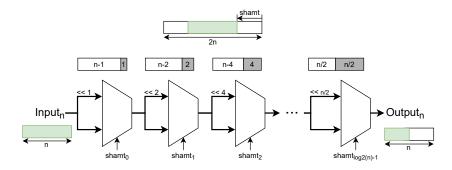

| 3.6<br>3.7                               | Vectorized adder structure.                                                                                                                                                                                                                                                                                                         | 34<br>34<br>35             |

| 3.6<br>3.7<br>3.8<br>3.9                 | Vectorized adder structure.                                                                                                                                                                                                                                                                                                         | 34<br>34<br>35<br>36       |

| 3.6<br>3.7<br>3.8<br>3.9<br>3.10         | Vectorized adder structure.                                                                                                                                                                                                                                                                                                         | 34<br>34<br>35<br>36<br>37 |

| 3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11 | Vectorized adder structure.<br>Left Barrel Shifter architecture based on multiplexers.<br>Input and shift amount generic vectors format.<br>Overview of the vectorized barrel shifter architecture.<br>Vectorized leading zero counter architecture .<br>Long (A) decimal and (B) binary multiplication example of $190 \times 170$ | 34<br>35<br>36<br>37<br>37 |

| 3.14 | Proposed posit decode module                                                                 | 43 |

|------|----------------------------------------------------------------------------------------------|----|

| 3.15 | Scale factor construction logic. Each rectangle corresponds to a bit. The grey bits are '0'. | 44 |

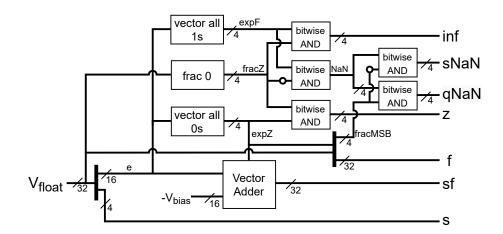

| 3.16 | Proposed IEEE-754 decode module                                                              | 45 |

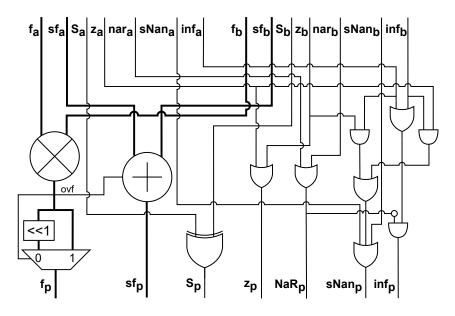

| 3.17 | Complete Multiply stage in a scalar perspective.                                             | 47 |

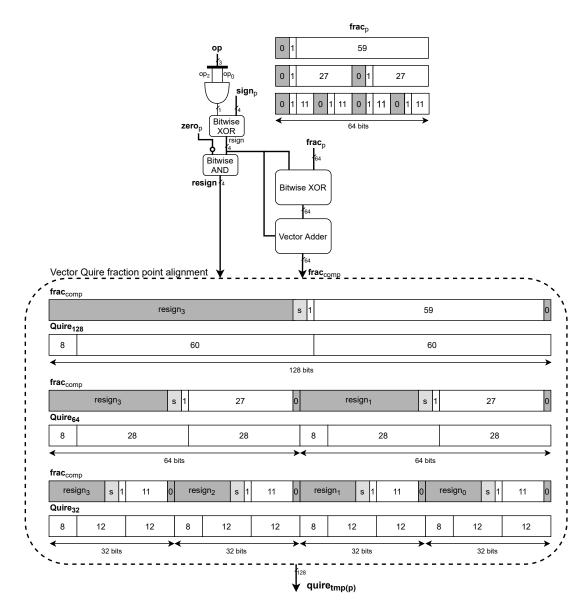

| 3.18 | Quire conversion of Quire Scale module for the multiplication result                         | 49 |

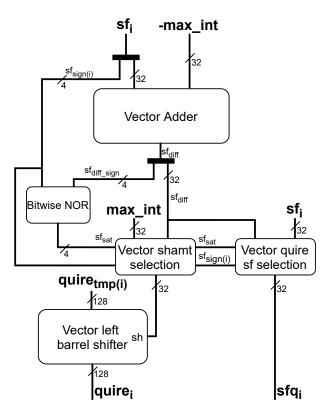

| 3.19 | Quire adjustment of the Quire Scale module for the <i>i</i> operand                          | 50 |

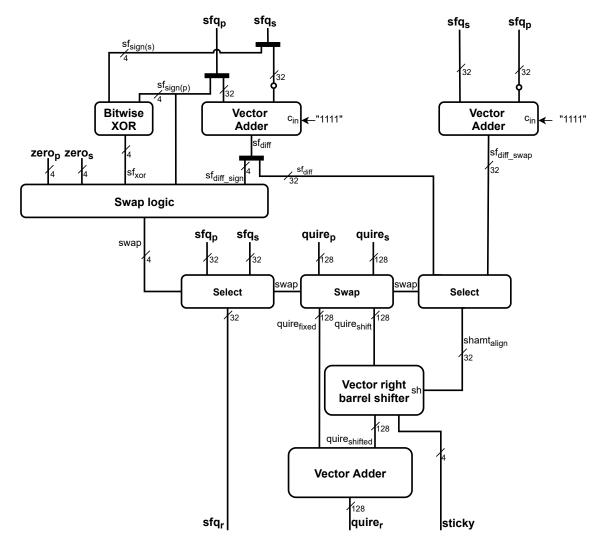

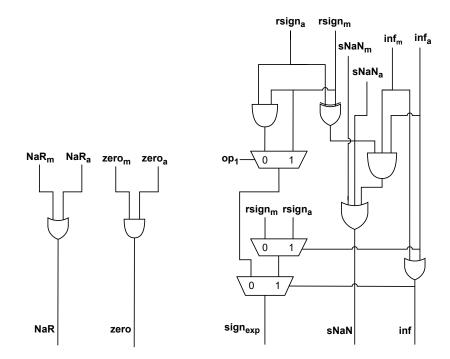

| 3.20 | Detailed Quire Accumulate arithmetic stage                                                   | 52 |

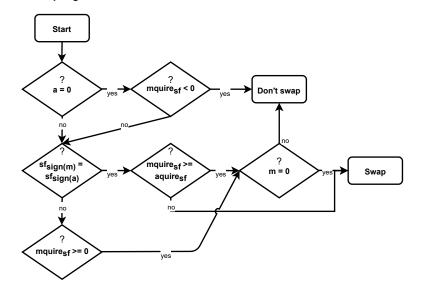

| 3.21 | (A) flowchart and (B) Boolean swap logic.                                                    | 53 |

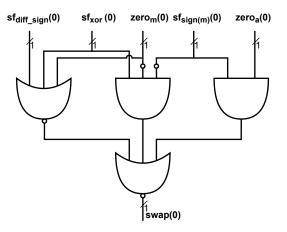

| 3.22 | Special encodings arithmetic.                                                                | 54 |

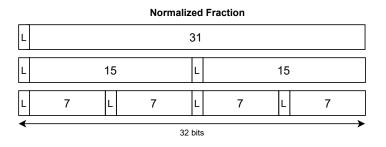

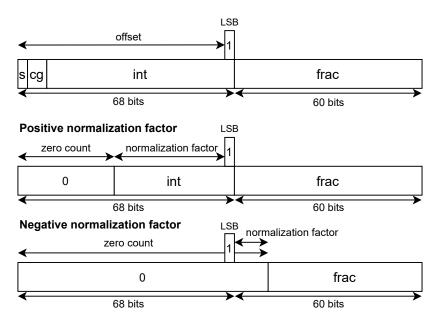

| 3.23 | Normalized fraction vector.                                                                  | 56 |

| 3.24 | Scale factor encoded in the quire                                                            | 56 |

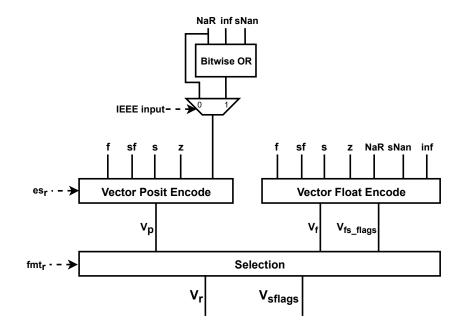

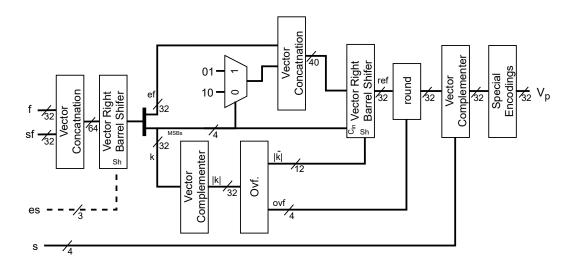

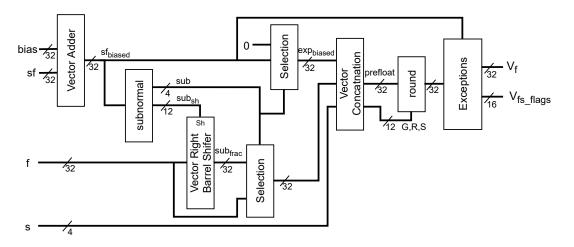

| 3.25 | Proposed Posit/IEEE-754 encode module                                                        | 57 |

| 3.26 | Proposed Posit encode module.                                                                | 58 |

| 3.27 | Proposed IEEE-754 encode module.                                                             | 59 |

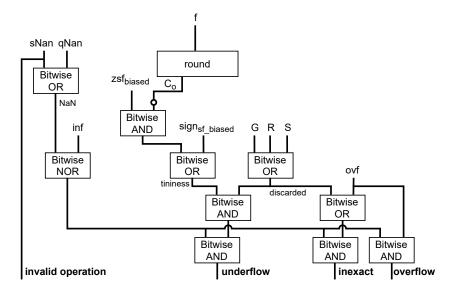

| 3.28 | IEEE-754 encode status flags logic.                                                          | 60 |

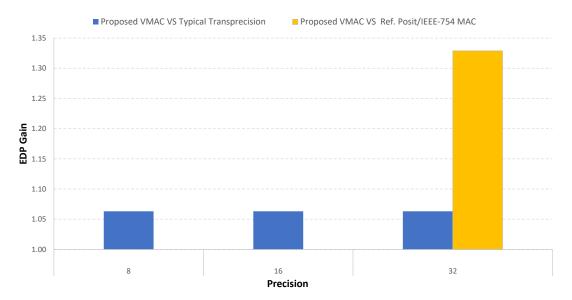

| 4.1  | ASIC implementation energy-delay product gain.                                               | 68 |

|      |                                                                                              |    |

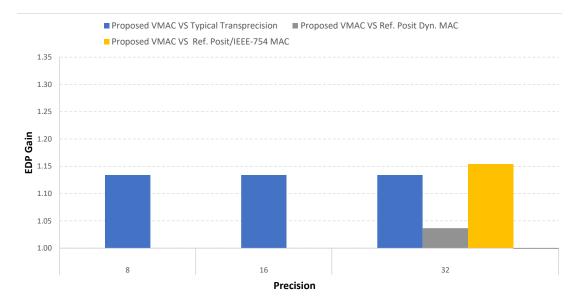

| 4.2  | FPGA implementation energy-delay product gain                                                | 71 |

| A.1  | 8 bit modified radix-4 Booth multiplier.                                                     | 84 |

# **List of Tables**

| 2.1 | Haf, single, double and quadruple precision floating-points encodings.                                              | 8  |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Encodings of the IEEE-754 standard.                                                                                 | 8  |

| 2.3 | Example of the run-length meaning $k$ of the regime field with 4 regime bits                                        | 11 |

| 2.4 | Parameters of standardized posit configurations.                                                                    | 14 |

| 2.5 | Arithmetic unit architectures for IEEE-754 and Posit.                                                               | 22 |

| 3.1 | Precision and operation signal encodings and respective function.                                                   | 41 |

| 3.2 | Specification of multiplication for IEEE-754 float special encodings.                                               | 47 |

| 3.3 | Specification of addition and subtraction for IEEE-754 float special encodings                                      | 54 |

| 4.1 | Comparison of the proposed VMAC.                                                                                    | 66 |

| 4.2 | Comparison of the proposed VMAC with state-of-the-art solutions for FPGA technology. $% \mathcal{A}_{\mathrm{S}}$ . | 69 |

| A.1 | Radix-4 Booth recoding.                                                                                             | 84 |

# Acronyms

| ASIC     | Application Specific Integrated Circuit     |

|----------|---------------------------------------------|

| DL       | Deep Learning                               |

| DNN      | Deep Neural Network                         |

| FMA      | Fused Multiply-Add                          |

| FPGA     | Field Programmable Gate Array               |

| FPU      | Floating-Point Unit                         |

| FP       | Floating-Point                              |

| IEEE-754 | IEEE Standard for Floating-Point Arithmetic |

| LSB      | least significant bit                       |

| LZC      | leading zero counter                        |

| MAC      | Multiply-Accumulate                         |

| maxpos   | maximum positive number                     |

| minpos   | minimum positive number                     |

| MSB      | most significant bit                        |

| NaN      | Not a Number                                |

| NaR      | Not a Real                                  |

| qNaN     | quiet NaN                                   |

| SIMD     | Single Instruction, Multiple Data           |

| sNaN     | signaling NaN                               |

| VMAC     | Vectorized Multiply-Accumulate              |

# Introduction

## Contents

| 1.1 | Motivation      |  |

|-----|-----------------|--|

| 1.2 | Objectives      |  |

| 1.3 | Contributions 4 |  |

| 1.4 | Thesis Outline  |  |

### 1.1 Motivation

The end of Moore's Law and waning of Dennard scaling mark the end of an era in which the computational capacity growth was mainly based on the down-scaling of silicon-based technology [5]. As a result, new research efforts have been shifting to the study of more efficient arithmetic circuits and improved computer technologies to meet the requirements of applications in several emergent domains [5].

Motivated by rapidly evolving algorithms advances in domains, such as Deep Learning (DL) and the ever-increasing amount of data availability, led to the exploration of different approaches to cope with increasing computational demands. In particular, significant advances have been made by lowering the arithmetic precision of Floating-Point (FP) operations [3,6–13], to obtain straightforward acceleration and efficiency. By lowering operand precision, it is possible to reduce memory storage per operand, obtain higher computing bandwidths, while reaching lower power and energy consumptions. In fact, it has been shown that it is possible to use different precisions in the different stages of an application [8, 14]. As an example, a recent study [8] verified that some stages of the training phase of DL applications are more sensitive to numerical errors than others, allowing the adjustment of the precision operations, such as 64-bits or even higher [15, 16]. Hence, it can be concluded that different applications have distinct precision requirements and adjusting the precision to the application can provide significant acceleration and efficiency gains.

Transprecision computing [14] is set on these principles and has received a gradually increasing attention as a viable paradigm to cope with the ever-increasing performance and energy efficiency demands in modern computing systems. Transprecision computing is a step beyond approximate computing [17], in which rather than tolerating errors implied by imprecise computations, systems are designed to deliver just the required precision. However, most transprecision hardware solutions [18] rely on instantiating multiple arithmetic modules to support different precisions, which leads to an increased chip area and power consumption. Moreover, even if the non-used modules are disabled, when a given precision is considered, it still results in a waste of resources [19].

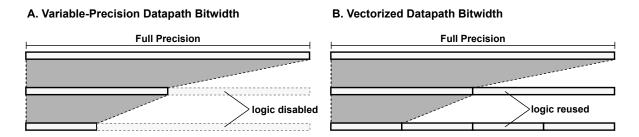

To tackle this issue, recent variable-precision arithmetic units [19–21] introduce dynamic datapaths that can operate in different precisions with the same hardware resources. To do so, they deploy a higher precision arithmetic logic (e.g., 32-bit) and allow parts of the circuit to be turned off to lower the operand precision by as much as it is required by the application (e.g., to 8-bit or lower [15]). While this approach provides for significant area reductions and enables straightforward Single Instruction, Multiple Data (SIMD) capabilities [19], existing solutions are often limited by their adoption of the IEEE-754 standard [20], whose lowest supported precision is only 16 bits. Some major computing market players such as Intel [22], Google [6] and Xilinx [23] have already realized that the adoption of alternative floating-point formats with reduced precision may provide straightforward computing acceleration. However,

despite their success, most solutions are tailored for the DL domain.

Alternatively, some recent solutions [19, 21] adopt the recently proposed Posit format [3], since it allows parameterizable precision and dynamic range (exponent size). This format is especially well suited for low-precision operations since it offers a trade-off between a wider dynamic range and an increased precision, which effectively allows a higher accuracy while lowering the operand precision (fewer bits). The Posit format is also particularly suited for fused operations since it adopts an exact accumulator structure (quire) with enough precision to avoid overflow and accuracy losses [4]. While Posit-based implementations traditionally define and fix its parameters at design-time [10–12, 24, 25], it has been shown that it is possible to support runtime-configurable exponent sizes with minimal hardware overheads [13]. This allows making use of the entire representable dynamic range for a given posit precision by specifying the exponent size of the input values. In turn, it also provides the possibility to encode a larger dynamic range, capable of supporting (within the same hardware) both values with high precisions and very large magnitude.

Nevertheless, while these features make posits well suited for low-precision arithmetic and transprecision computing, the hardware overhead associated with the quire becomes prohibitive when the precision and exponent size increase [24, 25]. Additionally, for a more general-purpose context, it is desirable to maintain compatibility with the standard IEEE-754 format, as it still is the most established FP format.

### 1.2 Objectives

The main objective of this thesis is to investigate and implement new variable-precision architectures for future Transprecision computing systems. Accordingly, the following research directions were considered for the herein presented work:

- · Research on new dynamic datapaths to enable variable-precision computing;

- Assess the viability of adopting the Posit format as an alternative to the IEEE-754 standard, for low-precision arithmetic;

- Investigate new mechanisms to mitigate the hardware overheads associated with the adoption of the Posit format for high-precision arithmetic.

The aimed work will also entail the description of all developed hardware modules in RTL and their evaluation in terms of performance and energy efficiency, by considering implementations in Application Specific Integrated Circuit (ASIC) technologies and Field Programmable Gate Array (FPGA) devices.

### 1.3 Contributions

According to the defined objectives, this thesis proposes a new Posit/IEEE-754 Vector Multiply-Accumulate (MAC) unit for transprecision computing. Besides combining variable-precision arithmetic and SIMD capabilities, it takes a step further from existing solutions by deploying a unified support for the IEEE-754 and Posit formats. It introduces the following contributions and features:

- an efficient variable-precision FP multiply-accumulate (MAC) 32-bit architecture, especially designed for transprecision computing;

- a unified FP arithmetic architecture compatible with both the IEEE-754 and the Posit formats with support for inter-format operation and conversion;

- a fully vectorized datapath to efficiently make use of the released hardware resources in lowprecision computing scenarios;

- SIMD decoding/encoding modules with shared support for FP vectors encoded with *i*) dynamic posit formats with configurable exponent size; *ii*) IEEE-754 standard and low-precision non-standard formats; and *iii*) multiple scalar and vector element precisions (including 32/16/8-bit scalars and 2x16/4x8-bit vectors).

Results show that, for an ASIC implementation, the proposed unit requires 50% less area and  $2.9 \times$  less power consumption when compared to a reference transprecision system setup. For a FPGA implementation, the proposed unit requires 2.1x less LUTs, 4x less registers, and 3.9x less power consumption when compared to a reference transprecision system setup.

### 1.4 Thesis Outline

The thesis is organized in the following chapters:

- Chapter 2 provides background on floating-point formats, by focusing on the IEEE-754 standard and the Posit number system. Then, the main arithmetic structures for each format are presented in detail, followed by a revision of the literature. The chapter is concluded by covering the main problems and solutions that can be found in the literature;

- **Chapter 3** describes the proposed variable-precision architecture, by introducing the adopted vector data formats and structures. Then, it is presented the proposed architecture and its main modules in detail;

- **Chapter 4** describes the main implementation results for ASIC and FPGA, together with a comparison with state-of-the-art solutions;

- **Chapter 5** presents the main conclusions of this work along with a discussion on possible future work directions.

# 2

# Background

### Contents

| 2.1 | Floating-point formats               |  |

|-----|--------------------------------------|--|

| 2.2 | Floating-point arithmetic structures |  |

| 2.3 | Floating-point Hardware Units        |  |

| 2.4 | Discussion                           |  |

| 2.5 | Summary                              |  |

Transprecision computing [14] is set on the principle that different application domains have different precision requirements. However, most transprecision hardware solutions [18] rely on the instantiation of multiple modules to support different precisions and only support the IEEE Standard for Floating-Point Arithmetic (IEEE-754). More recently, some floating-point architectures have been adopting the Posit format [3], which has been gaining attention as a possible complement to the IEEE-754 standard. The unified support of both formats can be the next step for transprecision computing.

This chapter presents some background on floating-point arithmetic with the IEEE-754 standard and Posit formats. The first section introduces relevant floating-point formats, starting with the definition of floating-point, the IEEE-754 standard for floating-point including some of his variants, and the recent Posit number system. The second section describes the main computing structures and operators for IEEE-754 floats and posit operations. The third section presents the most relevant IEEE-754 and Posit arithmetic unit architectures in the literature. Finally, a discussion is presented regarding IEEE-754 floats and posit as well as transprecision implementation approaches.

### 2.1 Floating-point formats

Since the early years of computing, several ways of approximating and representing real numbers have been introduced, each providing different compromises between the complexity of its manipulation and the involved approximation error. A relatively straightforward approach is to adopt a fixed-point representation, where the numbers are processed as integers with a fixed scale factor. They have three components: integer part, binary point (implied), and fractional part. They have simple associated hardware, however, they have a limited dynamic range, caused by the fixed radix point position.

Other proposed representations involve storing the logarithm of a number and doing multiplication by adding the logarithms or using a pair of integers (x,y) to represent the fraction x/y. However, floatingpoint arithmetic is by far the most widely used way of approximating real number arithmetic to perform numerical calculations on modern computers.

Floating-point was created as a means to have an approximation of real numbers while supporting both very small and very large real numbers (i.e. a larger dynamic range) with a limited number of bits. It is a "semi-logarithmic" representation with a fixed-point component (significand or mantissa) that is scaled by a factor (exponent). A floating-point number is represented as

$$sign \times significand \times base^{exponent}$$

. (2.1)

The most popular format for floating-point arithmetic is the IEEE-754 [1], a standard established in 1985 that has been expanded and improved by the Institute of Electrical and Electronics Engineers over the years. The standard defines encodings, operations, exception handling, and rounding rules. The

standard supports base 2 and 10, although the second is not relevant in this work.

### 2.1.1 IEEE-754 standard

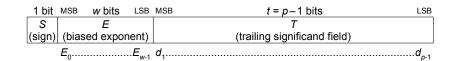

The IEEE Standard for Floating-Point Arithmetic was established in 1985 with the goal to improve the portability of floating-point computations and it was recently updated in 2019 [1]. The representation of binary floating-point data consists of three fields – sign, exponent, and trailing significand. In Figure 2.1 it is represented the structure of an n-bit float. The standard defines several formats of widths, 16, 32, 64, and 128 bits, and in general for any multiple of 32 bits of at least 128 bits. In Table 2.1 are represented the first four.

The sign bit is 0 for positive numbers and 1 for negative. The exponent is *w*-bit wide and it is represented as an unsigned integer with a bias: E = exp + bias. The significand field is represented as a fixed-point number with *t*-bits. Normalized numbers are represented as

$$(-1)^{sign} \times 2^{exp} \times 1.significand,$$

(2.2)

where the '1' denotes the hidden bit, which is implicitly encoded in the exponent. When the number is subnormal, the hidden bit is set to 0 and  $exp = exp_{min}$ . Apart from these encodings, the standard defines several expectations, such as Not a Number (NaN) and infinity, all represented in Table 2.2.

The IEEE-754 standard defines not only a number, but also several guidelines and rules in what concerns:

- Operations (e.g., Arithmetic operations, conversions and sign manipulation)

- Rounding

- Exceptions

Most arithmetic operations do not result in a number that can be exactly represented. In such cases, the result needs to be rounded. To that end, The IEEE-754 standard defines five rounding modes:

- roundTiesToEven rounds to the nearest value; if the two nearest are equally near, rounds to the

one with an even least significant digit; if that is not possible, rounds to the larger in magnitude.

- roundTiesToAway rounds to the nearest value; if the two nearest are equally near, rounds to the larger in magnitude.

Figure 2.1: Binary IEEE-754 floating-point format [1].

| Format                      | Bits (n) | Exponent Bits (w) | Bias  | Significand Bits (t) |

|-----------------------------|----------|-------------------|-------|----------------------|

| Half-precision (FP16)       | 16       | 5                 | 15    | 10                   |

| Single-precision (FP32)     | 32       | 8                 | 127   | 23                   |

| Double-precision (FP64)     | 64       | 11                | 1023  | 52                   |

| Quadruple-precision (FP128) | 128      | 15                | 16383 | 113                  |

Table 2.1: Haf, single, double and quadruple precision floating-points encodings.

| Encoding                      | Sign | Biased Exponent       | Fraction              |  |

|-------------------------------|------|-----------------------|-----------------------|--|

| Positive zero                 | 0    | 0 (all 0's)           | 0 (all 0's)           |  |

| Negative zero                 | 1    | 0 (all 0's)           | 0 (all 0's)           |  |

| Positive infinity             | 0    | (all 1's)             | 0 (all 0's)           |  |

| Negative infinity             | 1    | (all 1's)             | 0 (all 0's)           |  |

| qNaN                          | -    | (all 1's)             | any number (non-zero) |  |

| signaling NaN (sNaN)          | -    | (all 1's)             | any number (non-zero) |  |

| Positive nonzero (Subnormal)  | 0    | 0 (all 0's)           | 0.any number          |  |

| Negative nonzero (Subnormal)  | 1    | 0 (all 0's)           | 0.any number          |  |

| Positive nonzero (Normalized) | 0    | any number (non-zero) | 1.any number          |  |

| Negative nonzero (Normalized) | 1    | any number (non-zero) | 1.any number          |  |

Table 2.2: Encodings of the IEEE-754 standard.

- roundTowardPositive rounds to the closest value towards positive infinity.

- roundTowardNegative rounds to the closest value towards negative infinity.

- roundTowardZero truncation.

It is also stated in the standard that a binary format implementation shall provide the first rounding mode as default (*roundTiesToEven*) and the last three as user selectable. The mode *roundTiesToAway* is optional.

The standard specifies five kinds of exceptions that shall be signaled with the corresponding status flag and default result. The exceptions covered by the standard are:

- · Invalid operation

- · Division by zero

- Overflow

- Underflow

- Inexact

Some disadvantages (also argued in [3]) are: repeated patterns to represent NaN values,  $\pm\infty$  and  $\pm 0$  values, the possibility of overflow/underflow, the added complexity of using normalized/subnormal numbers, misused exponent size and the lack of reproducibility guarantees across systems. The latter occurs since, there are various optional mechanisms that are covered in the standard, including the subnormal support, the diagnostic information on invalid operation exception, which is provided in the quiet NaN (qNaN) output, etc.

### Variations

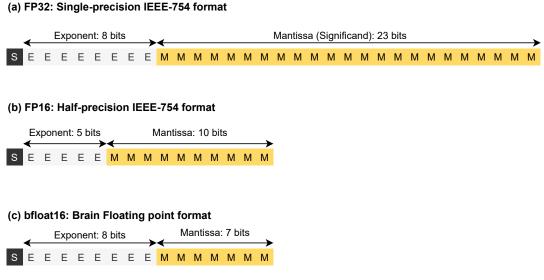

Several variations to the IEEE-754 standard have been recently proposed, mostly by the ever-increasing proliferation of deep learning applications. One of the most most popular is the "Brain Floating Point" (bfloat16) [2], which is a 16-bit truncated version of the F32. It aims to improve hardware efficiency while maintaining the ability to train accurate deep learning models, all with minimal switching costs from FP32. In Figure 2.2, is represented the structure of: (a) FP32, (b) FP16 and (c) bfloat16.

Since the FP16 format is prone to overflowing and Deep Learning (DL) is not a strongly precisionbound application, the bfloat16 format has an exponent of the same size as a FP32, at the cost of fraction accuracy. Furthermore, bfloat16 multipliers require nearly half the chip area size of an FP16 multiplier. However, this custom floating-point format is not suited for all domain applications, since it was designed specifically to DL.

There is also an 8-bit floating-point format [26], also known as microfloats. It has 1 sign bit, 4 exponent bits, and 3 significand bits. This 8-bit variation of IEEE 754 floating-point stresses some of its limitations. Specifically, it has 14 representations for NaN,  $\pm \infty$ , and  $\pm 0$  which make up to approximately 6.6% of useless values.

One of the most recent is the TensorFloat-32 (TF32) [27], introduced in the NVIDIA Ampere architecture. Despite the name, this format is 19-bit long and is a combination of FP16 and bfloat16. The mantissa is 10-bit long (similar to FP16), while the exponent is 8-bit long (similar to bloat16 and FP32). As a consequence, this format has the same dynamic range of FP32 and the same precision of FP16.

Most of these variations are tailored for the Deep Learning domain, contrarily to the Posit number system, which is gaining attention as a possible alternative (or complement) to the IEEE-754 Standard.

Figure 2.2: Structure of: (a) FP32, (b) FP16 and (c) bfloat16 [2].

### 2.1.2 Posit Format

The Posit format [3] is part of the latest revision of the unum (universal number) arithmetic framework. The original "Type I" unum was proposed in 2015 [28], and it is a superset of the IEEE-754 Standard. Following the Type I, the "Type II" unum [29] was proposed and corresponds to a completely new design based on the projective reals and abandons compatibility with the IEEE Standard. Motivated by the fact that Type II unums rely on table look-up for most operations and they are not adequate to fused operations, the "Type III" unum emerged in 2017 [3] – with the designation of posit. The Posit format is a "hardware friendly" version of Type II unums that keeps many of its merits while relaxing some mathematical properties. A draft of its standard [4] was made available in 2021.

A posit is defined by the pair  $\langle n, es \rangle$ , where *n* represents the word size and *es* the exponent size. In Figure 2.3 it is represented the structure of an *n*-bit posit, with *es* exponent bits.

The sign bit is 0 for positive numbers and 1 for negative. However, for negative numbers, it is necessary to take the 2's complement before decoding the following fields: regime, exponent, and fraction.

The Posit format presents a non-uniform encoding where the length of its parameters varies depending on the magnitude of the represented number. The regime is a sequence of identical bits, r, terminated by the opposite bit,  $\bar{r}$  (or by the end of the posit) and has numerical meaning, k, as demonstrated in Table 2.3. Let m be the number of identical bits in the regime. Then, k is given by:

$$k = \begin{cases} m-1 & \text{, if } r_0 = 1 \\ -m & \text{, otherwise.} \end{cases}$$

(2.3)

The encoded value indicates a scale factor (sf) of magnitude  $useed^k$  where  $useed = 2^{2^{es}}$  (or  $2^{k2^{es}}$ ).

The exponent can have up to es exponent bits (depending on how many bits remain to the right of the regime) and is represented as an unsigned integer, e. Contrarily to IEEE-754 floats, there is no bias. Hence the encoded value indicates a scale factor of  $2^e$ .

The fraction, f, is represented by the remaining bits that are not used by the regime and exponent fields. Similarly to the IEEE-754 significand field, there is a hidden bit. However, there are no subnormal numbers, that is, the hidden bit is always '1', and the encoded value is 1.f.

Similarly to the floating-point standard, the Posit format also defines exception values. However, it only provides a single representation for 0 (all '0' bits) and one  $\pm \infty$  = Not a Real (NaR) ('1' followed by

| sign | regime | exponent                                                | fraction            |  |

|------|--------|---------------------------------------------------------|---------------------|--|

| bit  | bits   | bits, if any                                            | bits, if any        |  |

| s r  | r r r  | $\overline{r}$ $\rho_1 \rho_2 \rho_2 \cdots \rho_m f_1$ | fo fo fo fo fo form |  |

|      |        | $\overline{r} e_1 e_2 e_3 \cdots e_{es} f_1$            |                     |  |

Figure 2.3: Posit format highlighting its components (sign, regime, exponent and fraction) [3].

| Binary               | 0000 | 0001 | <mark>001</mark> x | 01xx | 10xx | 110x | 1110 | 1111 |

|----------------------|------|------|--------------------|------|------|------|------|------|

| Numerical meaning, k | -4   | -3   | -2                 | -1   | 0    | 1    | 2    | 3    |

**Table 2.3:** Example of the run-length meaning *k* of the regime field with 4 regime bits.

all '0' bits). It does not have NaN representation, thus all remaining bit patterns are used to represent actual numbers. Furthermore, the sf can be heavily affected by the chosen value of es, which will, in turn, establish the maximum positive number (maxpos) and minimum positive number (minpos) representable as posits. Unlike IEEE-754 floats, posits do not overflow nor underflow, but saturate to  $\pm$ maxpos or  $\pm$ minpos, respectively. Therefore, a number (x) encoded as a posit has a decoded value p given by Equation 2.4.

$$p = \begin{cases} 0 & \text{if } x = 000 \dots 0, \\ \pm \infty = \mathsf{NaR} & \text{if } x = 100 \dots 0, \\ (-1)^{sign} \times useed^k \times 2^e \times 1.f & \text{all other } x. \end{cases}$$

(2.4)

Example 2.1.1 illustrates the decoding process for a posit, according to Equation 2.4. To understand the example it is important to define the posit sf, which is analogous to the exp from IEEE-754 floats. It is the combination of the regime and exponent factors and is obtained by rearranging Equation 2.4 as

$$p = (-1)^{sign} \times 2^{e+k2^{es}} \times 1.f,$$

(2.5)

therefore,  $sf = e + k2^{es}$ .

### Example 2.1.1 Posit decoding

Consider the following posit bit strings for the < 8, 2 > configuration:

1. 01100101;

- 2. 11001101;

- 3. 01111101.

Since the configuration is < 8, 2 >,  $useed = 2^{2^2} = 16$  for all examples.

The first two examples correspond to decoding a simple positive and negative number. The third example shows some of the peculiarities due to the variable-length parameters. An analysis of each bit string is presented below, with the parameters discriminated (where the variable length is well observed) according to the color scheme from Figure 2.3:

1. 0 110 01 01

The sign bit 0 means the value is positive. The regime bits 110 have a run-length of two

### Continued -

1s, which means k is 1, corresponding to a contribution by the regime of  $16^1$ . The exponent bits, 01, represent 1 (as an unsigned binary integer), and contribute another scale factor of  $2^1$ . Lastly, the fraction bits 01 represent 1 (as an unsigned binary integer), so the fraction is  $1 + \frac{1}{4}$ . This translates in:  $p = 1 \times 16^1 \times 2^1 \times 1.25 = 40$ .

### 2. 1 1001101 (01 10 011)

The sign bit 1 means the value is negative, consequently, it is necessary to take the 2's complement to decode the remaining fields: 01 10 011.

The regime bits 01 have a run of one 0, which means k is -1, corresponding to a contribution by the regime of  $16^{-1}$ . The exponent bits, 10, represent 2 (as an unsigned binary integer), and contribute another scale factor of  $2^2$ . Lastly, the fraction bit 011 represent 3 (as an unsigned binary integer), resulting in the fraction  $1 + \frac{3}{8}$ . This translates in:  $p = -1 \times 16^{-1} \times 2^2 \times 1.375 = -0.34375$ .

### 3. 0 111110 1

The sign bit 0 means the value is positive. The regime bits 111110 have a run of five 1s, which means k is 4, corresponding to a contribution by the regime of  $16^4$ . For the exponent, in this case, there is only one 1 bit left in the bit string. However, the exponent field is 2 bits wide, therefore, the represented exponent corresponds to 10, which represents 2 (as an unsigned binary integer), and contributes another scale factor of  $2^2$ . Since there are no bits left, the fraction is 1 + 0. This translates in:  $p = 1 \times 16^4 \times 2^2 \times 1.0 = 262144.0$ .

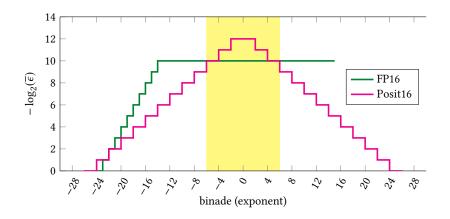

When comparing the structure of a posit against the IEEE-754, the main difference corresponds to the presence of the regime field and the variable length of the parameters. The variable length of the regime allows numbers near to 0 to have more accuracy than extremely large or extremely small numbers (tapered precision), which is the same distribution that Deep Neural Network (DNN) weight parameters usually follow (more grouped around 0). As a result, posit presents more accuracy in this "golden zone", as highlighted on Figure 2.4. However, out of this zone, posits become less accurate than IEEE-754 of the same precision.

Finally, the Posit format only defines one rounding method, where the value is rounded to the nearest binary value and if two posits are equally near, the one with binary encoding ending in 0 is selected.

Figure 2.4: Accuracy comparison of FP16 and posit < 16, 1 > with the posit "golden zone" highlighted [24].

### Quire

Besides its non-uniform encoding, the most important feature of the Posit format is the adoption of an exact accumulator for fused operations. This structure, named quire, is a 2's complement fixed-point accumulator based on the Kulisch accumulator [30]. It is capable of storing sums of products of posits without rounding, up to at least  $2^{n-1} - 1$  (dependent of the carry guard) number of such products. As a consequence, the quire format is particularly useful to implement the frequent dot products present in DNN computations, such as convolutions, matrix multiplications, etc. In Figure 2.5 it is represented the quire format.

The quire is composed of the following fields:

- length: qsize = 16n bits.

- fraction: nq = (8n 16) bits.

- integer: nq bits.

- carry guard: cg = 31 bits (allows at least  $2^{30} 1$  sums of products).

The value of the quire datum is given by the 2's complement signed integer represented by all bits, divided by  $2^{nq}$  and also includes the NaR exception.

Despite the size and exponent parameters of a posit configuration being arbitrary, there are 3 standardized configurations and its parameters are represented in Table 2.4.

The equations that define the quire parameters bit-width on the standard do not adjust to the dynamic

| 1  bit   | MSB          | c bits      | LSB              | MSB          | nq bits     | LSB        | MSB   | nq bits      | LSB        |

|----------|--------------|-------------|------------------|--------------|-------------|------------|-------|--------------|------------|

| S (sign) | С            | (carry guar | d)               |              | I (integer) |            |       | F (fraction) |            |

|          | $C_0 \ldots$ |             | $\ldots C_{c-1}$ | $I_0 \ldots$ |             | $I_{nq-1}$ | $F_0$ |              | $F_{nq-1}$ |

Figure 2.5: Binary quire format [4].

| Parameter                  | posit8 | posit16 | posit32 |

|----------------------------|--------|---------|---------|

| whole representation $(n)$ | 8      | 16      | 32      |

| max exponent es            | 2      | 2       | 2       |

| quire (16n)                | 128    | 256     | 512     |

Table 2.4: Parameters of standardized posit configurations.

range of all the configurations, in fact, they are simplifications tailored for the configurations of Table 2.4. The generic size of the quire for a given configuration is given by Equation 2.6. The 1 is for the sign, the *cg* is self-explanatory, the remaining factor corresponds to the integer and fraction parameters  $(nq = 2^{es+1} \times (n-2))$ .

$$qsize = 2^{es+2} \times (n-2) + 1 + cg$$

(2.6)

### 2.2 Floating-point arithmetic structures

This section presents an overview of the most relevant IEEE-754 and Posit floating-point arithmetic operations and their computing architecture. These include common operations, such as addition/sub-traction, multiplication, division, as well as fused operations, such as Fused Multiply-Add (FMA) and Multiply-Accumulate (MAC). The latter are particularly used in deep learning applications for dot prod-ucts, matrix operations and convolutions.

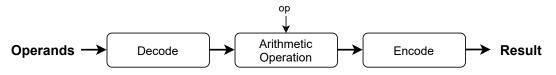

A typical Floating-Point Unit (FPU) structure is depicted in Figure 2.6. The computation is usually in three main phases: *i*) decoding; *ii*) operation; and *iii*) encoding. In the decoding stage, special encodings (e.g. NaN for IEEE-754 floats and NaR for posits) are detected and the fields of the operands are extracted. After properly decoded, the respective arithmetic operation is conducted, whose result must be normalized and the exponent/scale factor properly adjusted. In the encoding stage, the result is rounded and packed, and exception flags are generated. While the various arithmetic operations are mostly identical and independent from the format, the decode and encode stages are naturally dependent on it. In particular, those for the Posit format are more complex, therefore, they will be addressed independently.

Figure 2.6: Floating-point unit structure.

### 2.2.1 IEEE-754 Format Decoding

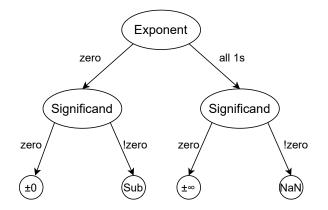

To decode IEEE-754 floats, it is only necessary to unpack all the fields (sign, exponent, and significand), since they can be directly obtained from the encoded binary, only exception cases ( $\pm 0$ ,  $\pm \infty$  and NaN) need to be processed. Nevertheless, first, the three fields are extracted and the hidden bit (obtained through the exponent) is concatenated with the significand. Figure 2.7 depicts how to detect the various special encodings. Specifically, if the exponent is 0, the hidden bit is 0, otherwise, the hidden bit is 1. This logic does not influence the  $\pm \infty$  and NaN decoding since they are usually decoded to flags. Furthermore, as there are two types of NaN and since the standard does not provide details on how to distinguish between a qNaN and a sNaN, they depend on the implementation.

Figure 2.7: Decision tree representation of the IEEE-754 special encodings.

### 2.2.2 Posit Decode

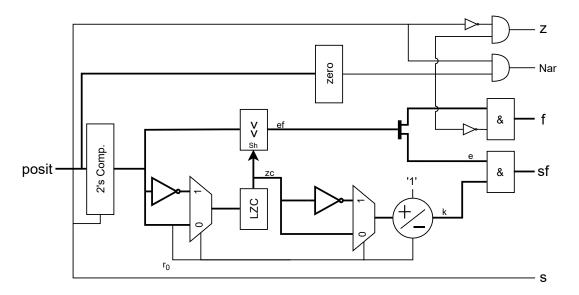

In contrast with the IEEE-754 format, where the location of the fields is known a priori, the location of the fields in a posit varies depending on the magnitude of the encoded number. Therefore, the decoding of a posit number is much more complex. This can be observed in Figure 2.8, where the common structure of a posit decoding module is illustrated.

The decode stage translates a posit value to their corresponding sign (s), scale factor (sf) and fraction (frac) fields, while signaling the exceptions NaR and zero (z) through flags. Posit decoding is a process that includes several steps. First, the sign is extracted from the most significant bit (MSB) and the 2's complement is taken according to the sign value. Next, the regime run-length (zc) is decoded by means of a leading zero counter (LZC). However, if the run-length starts with '1' the value ( $r_0$ ='1') is first inverted. Alternatively, the run-length can be obtained with a LZC in parallel with a leading one counter, being the result selected according with  $r_0$ .

Then, the value encoded in the regime (k) is calculated according to equation 2.3, which is controlled by the  $r_0$  bit. At the same time, the regime is shifted out of the 2's complemented posit value according

Figure 2.8: Typical posit decoding module.

to the zc, leaving the exponent and fraction (ef). Since the exponent size is known (defined by es), the exponent and fraction can be easily detached. Finally, the k value is concatenated with the exponent to obtain sf, and the hidden bit is concatenated, resulting in the fraction (f). The hidden bit is '1' if the posit is not an exception (zero or NaR).

### 2.2.3 Addition/subtraction

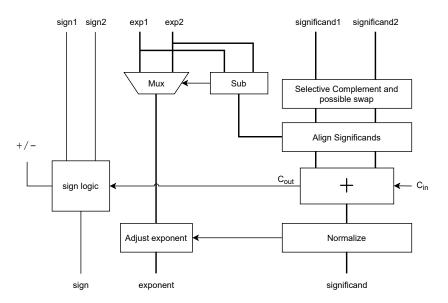

Floating-point addition/subtraction is regarded as a very complex operation involving several steps. A simplified version of the classical structure for floating-point addition/subtraction [31, 32] is represented in Figure 2.9.

Suppose we want to add the 8-bit binary numbers  $1.1010110 \times 2^{10}$  and  $1.1011001 \times 2^5$ . Mathematically, to add two exponential numbers, their exponents need to be equal for the significands to be added. In case they are not, there are two possible ways to achieve this. The largest exponent can be decremented (significand left-shifted) or the smallest exponent can be incremented (significand right-shifted). Since there is a finite number of bits, there will be a loss of precision. Left shifting the significand affects the MSBs of the significand, while right shifting affects the LSBs. Loss of MSBs implies more precision loss, therefore the smaller exponent is usually incremented and the correspondent significand right shifted. Moreover, pre-shifting is typically applied to only one of the operands, therefore, swap capability is also provided. With the significands aligned, the addiction/subtraction can be conducted. Subsequently, if the operation produces a carry-out bit, the resulting significand value of the addition corresponds to a number in the interval [0,4[. In such a case, the result must be normalized to the interval [1,2[, with corresponding exponent adjustments.

Figure 2.9: Floating-point addition/subtraction structure.

The posit addition/subtraction is very similar to the IEEE-754 operator, it solely differs on the way exponent and scale factor are handled. In Posit format, the scale factor is usually in 2's complement, therefore, 2's complement comparison is needed. However, the detection of larger and smaller operands is done with a simple integer comparison of the posit values (complemented if negative).

### 2.2.4 Multiplication and Division

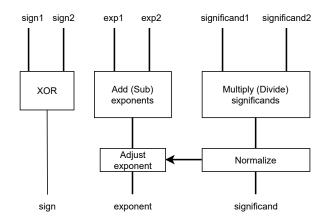

The floating-point multiplication and division operations are mathematically simpler than addition/subtraction operations and their implementation is much more straightforward. The classical structure for the floating-point multiplication/division [31,32] is represented in Figure 2.10. The significands are multiplied/divided, the exponents are added/subtracted (with the proper bias subtraction) to calculate a temporary exponent, and the sign is computed with a XOR operation.

The significand division corresponds to an integer divisor and can be performed with different algorithms. The most common are digit recurrence algorithms and functional iteration algorithms [33]. The first class is a slow division algorithm that produces one digit of the final quotient per iteration, converging linearly to the result. The second class is a fast division algorithm that represents the division or reciprocal operation as a function and uses function-solving techniques such as the Newton-Raphson method [33] to converge to the quotient or reciprocal.

For posit multiplication, the only difference is the scale factor calculation, which does not involve a bias.

Figure 2.10: Floating-point multiplication/division structure.

### 2.2.5 Fused Multiply-Add

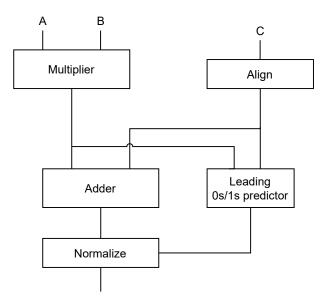

A fused multiply–add (FMA) operator (defined as  $(A \times B)+C$ ) is a floating-point operation that performs a multiplication followed by an addition between three operands, without intermediate normalization/round-ing (fusing). A simplified version of a FMA structure [32, 34] is represented in Figure 2.11.

Since the FMA operator is a combination of a multiplier and an adder/subtractor without the intermediate rounding step, it is necessary to include a larger adder (when compared to a single addition operation) and alignment logic. Similarly, to the single multiplication, the significands are multiplied; the exponents are added, and the sign is computed with a XOR operation. With the resulting exponent, alignment is conducted with the third operand exponent. This concludes the multiplication. The resulting significand is added/subtracted with the aligned significand of the third operand and a leading zero/one

Figure 2.11: Floating-point FMA structure.

predictor is used to shorten the critical path of the normalization. After normalizing the significand, the signals enter the encoding module.

Remembering the reader that the posit standard defines a long accumulator for fused operations, the quire, however, its use is not mandatory. In fact, the standard [4] states that fused expressions (such as fused multiply-add and fused multiply-subtract) do not need to be performed in the quire to be compliant. Therefore, this structure can be applied in the posit environment.

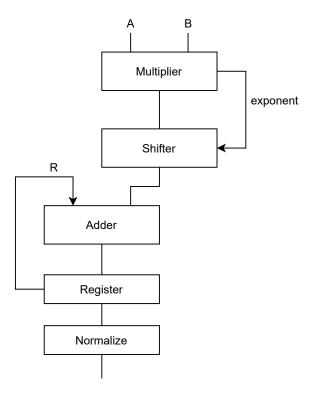

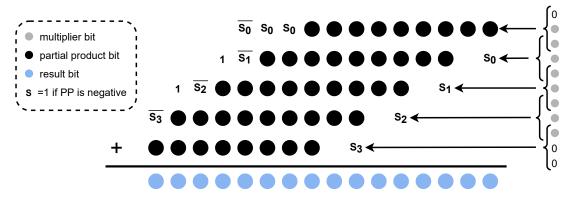

#### 2.2.6 Multiply-Accumulate

This operation implements the multiplication of two elements followed by a continuous accumulation of the multiplication results (defined as  $R \leftarrow R + (A \times B)$ ). This structure is particularly useful to compute several dot products with minimal deviations from the exact result. While there are different solutions for accumulations, the most relevant for this work is the Long Accumulator.

The first Long Accumulator (Kulisch accumulator) was proposed by Ulrich W. Kulisch in [30], which corresponds to a 2's complement fixed-point accumulator to process the dot product of IEEE-754 floats with full accuracy. The structure of a basic long accumulator is depicted in Figure 2.12.

The multiplication result is converted to a 2's complement fixed-point notation which is accumulated with the value stored in the register. The result of each accumulation is normalized and propagated to

Figure 2.12: MAC structure with Long Adder and Long Shifter.

be encoded back to the IEEE-754 format.

While this operation is not included in the IEEE-754 standard, the Posit standard defines a similar structure named quire, which is specific for accumulation. Nonetheless, several IEEE-754 accumulators have already been proposed and differ from the Posit format mainly in the accumulator sizes, since the formats have different dynamic ranges. While the size of the quire is given by Equation 2.6, an analogous for IEEE-754 is given by Equation 2.7, for the Kulisch accumulator:

$$asize = 2e_{max} + 2n + 2|e_{min}| + cg$$

(2.7)

#### 2.2.7 IEEE-754 Format Encoding

Floating-point arithmetic operation results are encoded to the IEEE-754 format by translating the sign, exponent, and significand fields to a binary format. Since the position to which a value must be rounded is known when performing this conversion, the encoding is fairly straightforward. It is only necessary to apply a rounding scheme and result selection, according to the special cases defined by the format. Some encodings may also produce some of the following status flags:

- Inexact: set if the result is different from the mathematically exact result of the operation.

- · Underflow: set if the rounded value is tiny and inexact.

- Overflow: set if the absolute value of the rounded value is too large to be represented.

- Divide-by-zero: set if the result is infinite given finite operands.

- Invalid: set if a real-valued result cannot be returned (e.g.,  $0 \times \infty$ ,  $+\infty \infty$ ).

Some of the status flags have an associated result. The overflow outputs  $\pm \infty$  (depending on the sign), the divide-by-zero and invalid outputs qNaN.

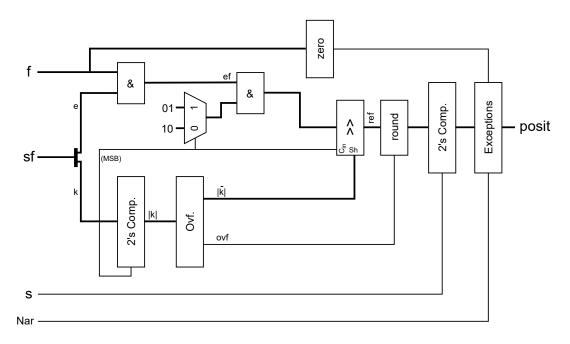

#### 2.2.8 Posit Format Encoding

To encode a posit value, it is necessary to translate the sign (s), scale factor (sf), and fraction (f) fields to a Posit binary format. In Figure 2.13 is represented the common structure of a posit encoding module.

The encoding process starts by detaching the regime value (k) from the exponent (e), according to the exponent size *es*. The k value's 2's complement is taken and the corresponding encoded regime value is shifted-in (according to k's sign) to the exponent and fraction fields that are concatenated in parallel (ef). The resulting signal (ref) is rounded. Since posits do not overflow and underflow, when the k's value is greater in the module than the maximum regime value, no round-up is allowed. The rounded value is then 2's complemented according to s. Finally, the result is obtained considering the special cases zero and NaR.

Figure 2.13: Typical posit encoding module.

# 2.3 Floating-point Hardware Units

Alternative floating-point formats with reduced precision have been gaining attention in the DL and artificial intelligence application domains. In fact, several implementations already exploit low-precision/custom floating-point formats. Such is the case of NVIDIA's Graphics Processing [7] Units and Google's Tensor Processing Units [35], both supporting the FP16 and bfloat16 formats. However, some DL operations do not need as much precision, resulting in the growing interest in exploiting low-precision posits.

The DL inference stage tends to have low sensitivity to errors, often allowing good performance to be achieved with very low precisions (e.g. 8-bit posits [36, 37]). Conversely, the training phase is more challenging and the most computationally demanding stage. Recent results suggest that posits can consistently achieve similar accuracies to IEEE-754, with precisions as low as half of those used by the IEEE-754 standard [8, 38, 39]. However, resources, energy, and performance optimizations are not guaranteed if the posit hardware is more costly. To assess the posit potential, it is necessary to compare posit hardware implementations with IEEE-754 implementations.

Most common hardware units provide support both for the elementary and fused operators, such as addition, subtraction, multiplication, division, and fused multiply-add. Both standards include the first four. However, in what regards fused operators, the IEEE-754 standard [1], only supports fused multiply-add, which requires a rounding step at every multiply-add operation. In contrast, the Posit standard [4], supports FMA and MAC, making use of the quire for fused operations, specializing in continuous accumulation, with rounding errors being introduced only after the last operation.

| Format   | Operator | Ref. | Sup. Device | FPGA          | Lat.(cycle) | LUTs  | Reg. | DSPs | Freq.(MHz) |

|----------|----------|------|-------------|---------------|-------------|-------|------|------|------------|

|          |          | [44] | FPGA        | Zynq 7000 SoC | 5           | 388   | 252  | 0    | 107.5      |

|          | Add      | [46] | FPGA        | Zynq 7000 SoC | 6           | 503   | 290  | 0    | 83         |

|          |          | [47] | FPGA        | Zynq 7000 SoC | 7           | 448   | 360  | 0    | 126.6      |

|          |          | [44] | FPGA        | Zynq 7000 SoC | 4           | 263   | 234  | 1    | 161.3      |

|          | Mult     | [46] | FPGA        | Zynq 7000 SoC | 4           | 328   | 153  | 1    | 120.5      |

| IEEE-754 |          | [47] | FPGA        | Zynq 7000 SoC | 12          | 610   | 445  | 0    | 126.6      |

|          | Div      | [44] | FPGA        | Zynq 7000 SoC | 12          | 823   | 539  | 0    | 92.6       |

|          |          | [47] | FPGA        | Zynq 7000 SoC | 35          | 627   | 525  | 0    | 126.6      |

|          | FMA      | [44] | FPGA        | Virtex-7      | 6           | 258   | 296  | 2    | 196        |

|          |          | [45] | FPGA        | Virtex-7      | 19          | 989   | 1210 | 3    | 493        |

|          | MAC      | [50] | FPGA        | Zynq 7000 SoC | 12          | 5300  | 1900 | 2    | 90         |

|          |          | [51] | FPGA/ASIC   | Zynq 7000 SoC | 0           | 1103  | 0    | 0    | 31.7       |

|          |          |      | FPGA/ASIC   | Zynq 7000 SoC | 5           | 884   | 254  | 0    | 113.6      |

|          | Add      | [10] | FPGA/ASIC   | Zynq 7000 SoC | 0           | 981   | 0    | 0    | 25         |

|          |          | [25] | FPGA        | Zynq 7000 SoC | 0           | 745   | 0    | 0    | 41.7       |

|          |          |      | FPGA        | Kintex-7      | 22          | 738   | 811  | 0    | 376        |

|          |          | [51] | FPGA/ASIC   | Zynq 7000 SoC | 0           | 616   | 0    | 4    | 36.1       |

|          |          | [51] | FPGA/ASIC   | Zynq 7000 SoC | 6           | 802   | 204  | 1    | 108.7      |

|          | Mult     | [10] | FPGA/ASIC   | Zynq 7000 SoC | 0           | 572   | 0    | 4    | 30.3       |

| Posit    |          | [25] | FPGA        | Zynq 7000 SoC | 0           | 469   | 0    | 4    | 37         |

| Posit    |          | [20] | FPGA        | Kintex-7      | 21          | 544   | 710  | 4    | 413        |

|          |          | [51] | FPGA/ASIC   | Zynq 7000 SoC | 12          | 922   | 538  | 5    | 129.9      |

|          | Div      |      | FPGA/ASIC   | Virtex-7      | 0           | 4,050 | 0    | 0    | 21.7       |

|          |          | [53] | FPGA        | Virtex-7      | 0           | 828   | 0    | 0    | 4.7        |

|          | MAC      | [25] | FPGA        | Kintex-7      | 40          | 5068  | 6256 | 4    | 112        |

|          |          | [13] | FPGA/ASIC   | Virtex-7      | 6           | 4134  | 1580 | 4    | 85         |

|          | FMA      | [54] | FPGA        | Artix-7       | 0           | 1740  | 0    | 0    | 18         |

|          |          | [55] | FPGA        | Artix-7       | 0           | 1797  | 0    | 0    | 21         |

Table 2.5: Arithmetic unit architectures for IEEE-754 and Posit.

While the hardware for floating-point operators has been extensively studied in the literature [20, 40–50] and the Posit format has arisen the interest of many researchers in the community and there is already a considerable amount of studies for hardware implementations [10, 12, 13, 19, 21, 25, 51–55]. Table 2.5 presents some of the most relevant works with the respective hardware metrics for 32-bits operators. The aim of this table is to assess the posit potential, not to list all the implementations, therefore, only the comparable implementations, in terms of architecture or technology differences, are listed.

#### IEEE-754 floating-point unit architectures

Since the IEEE-754 standard was established in 1985, there are plenty of hardware implementations for addition/subtraction [40–44, 46, 47], multiplication [44–47] and division [44, 47, 49]. Regarding fused operations, the implementations from [44,45] correspond to classical FMA architectures, while [20] goes a little further, with native support for vectorization ( $1 \times 128$ -bit,  $2 \times 64$ -bit,  $4 \times 52$ -bit or  $8 \times 16$ -bit precision parallel operations). Although accumulation is not compliant with the IEEE-754 standard, there are plenty of MAC units, one recent example was proposed in Fiolhais et al. [50]. There are some differences between the architectures, however, the most relevant corresponds to the subnormal number support,

which is only provided by [20, 40, 42, 46, 47].

#### **Posit-based architectures**

Regarding the posit hardware implementations, studies [10, 25, 51, 52] implement the fundamental arithmetic operators (adder/subtractor and multiplier) while others implement dividers [51, 53]. Regarding fused operations, Forget et al. [25] implement a MAC unit based on the Kulish accumulator, using the quire to store accumulations. Classical FMA architectures [12, 54, 55] were also implementation. In [13] it is proposed a MAC architecture, which supports both accumulation or addition with a third operand. They also proposed a 64-bit vectorized MAC posit unit (1×64-bit, or 2×32-bit, or 4×16-bit, or 8×8-bit parallel operations) integrated in a reconfigurable tensor unit [19]. More recently, Zhang et al. [21] proposed a Posit vectorized variable precision architecture, however, it only performs multiplication.

For this format, the architectural differences are more significant, in particular, Jaiswal et al. [51] does not concatenate the regime and the exponent, Forget et al. [25] propose a C++ template library and uses a scale factor with bias (just like IEEE-754 floats), Xiao et al. [53] keeps the 2's complement format, and Neves et al. [13] supports different exponents values dynamically through a set of shifters.

#### IEEE-754 vs Posit

Observing the results represented in Table 2.5 for the referred implementations, it can be concluded that the posit hardware has an overhead in terms of time and resources in both operators. This occurs because of the complexity of the encode and decode steps, as a result of the format's non-uniform encoding scheme. Additionally, the quire has considerable overheads of resources and timing, as expected of a long accumulator.

In terms of division operators, a fair comparison between the formats is not possible since the implementations use different division algorithms, which would only highlight the differences between them, not the differences between the formats. Therefore, regarding the digit recurrence methods [44] and [53] (see Table 2.5) have similar resource utilization. However, the posit divider [53] is not pipelined therefore, a totally fair comparison is not possible. Nonetheless, it can be estimated that both standards have similar resources utilization. In terms of timing, a comparison is not possible because of the referred differences.

The metrics of the IEEE-754 fused operators [44] and [50] (see Table 2.5) reveal the trade-off of having exact accumulation without loss of precision. As such, a significant difference is visible in resource utilization and maximum operating frequency. The same situation occurs if a IEEE-754 FMA implementation is compared with a Posit implementation supporting exact accumulation (see metrics from [25] and [13] in Table 2.5). This reveals a problem for the Posit format, and in general, of exact accumulators, it is an extremely costly architecture, almost prohibitive with more than 32-bits. In conclusion, for the same precision, posit arithmetic is slightly more costly because of its variable size fields. The quire is also extremely costly in terms of resources, since its size grows exponentially with the precision. However, posits can be used with fewer bits. Which suggests an energy and memory save, and performance boost for several applications, such as DL.

# 2.4 Discussion

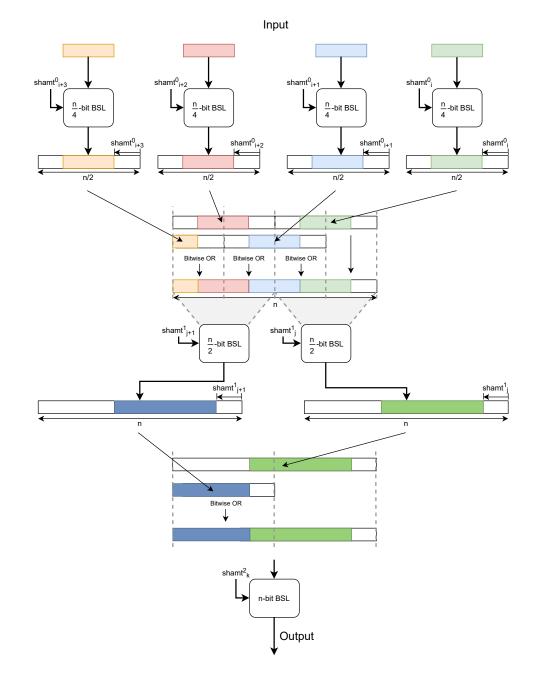

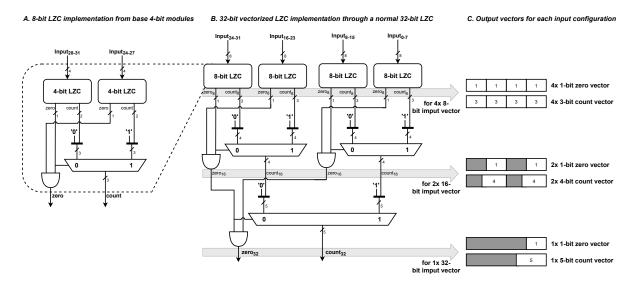

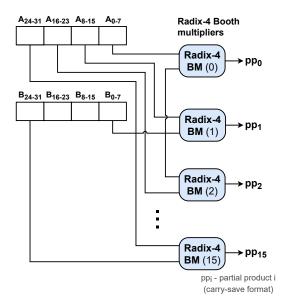

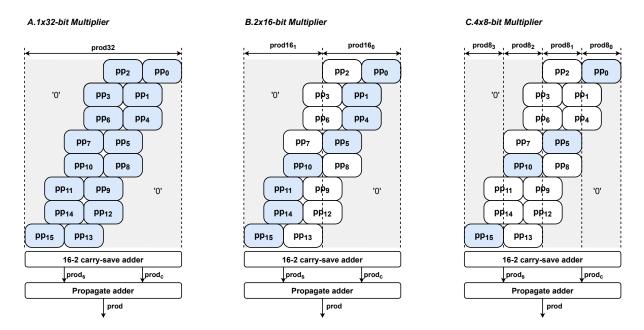

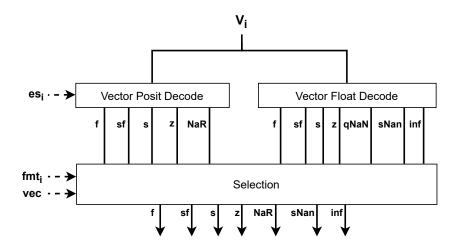

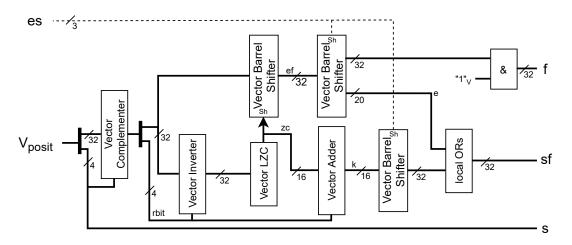

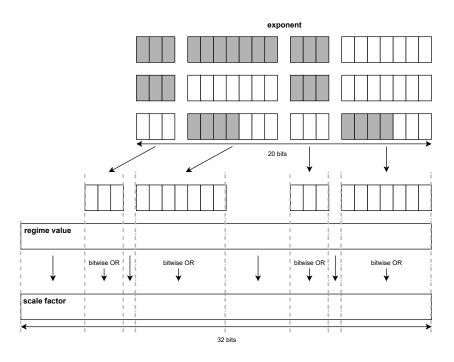

As it was discussed in the previous sections, the Posit format presents several advantages over IEEE-754 floats, such as improved accuracy and larger dynamic ranges with lower precision (fewer bits). These make posits especially suited for low-precision arithmetic. However, posits represent numbers with a non-uniform format. In particular, for smaller values (in magnitude), the Posit format can provide more accuracy and for large values (in magnitude) the accuracy is reduced. This makes it suitable for applications such as DL, but unsuited for other domains, such as particle physics simulations and integration methods, where the numerical values of the result is often unbounded [24]. Moreover, modern computing systems have the IEEE-754 standard deeply embedded in compilers and low-level software routines. Therefore, a drastic replacement of the IEEE-754 standard to the Posit format may be unfeasible [24]. In terms of hardware overhead, for the same precision, Posit arithmetic is slightly more costly because of its variable size fields (i.e., regime). The quire is also extremely costly in terms of resources since its size grows exponentially with Posit precision. Instead of looking at the Posit format as an alternative to the IEEE-754 standard, it is more suited to look at it as a complement. Since their intermediate format (after decoded) is quite similar, an arithmetic unit with a shared datapath that supports both representations is accomplishable and may provide important steps towards the proliferation of transprecision computing.