# **Non-Destructive Testing Based on Eddy Currents**

Detector de Falhas em Soldaduras

## Luís Filipe Soldado Granadeiro Rosado

# Master's Degree Dissertation in Electronics Engineering

President: Prof. Maria Beatriz Mendes Batalha Vieira Vieira Borges

Supervisor: Prof. Moisés Simões Piedade

Co-supervisor: Prof. Pedro Miguel Pinto Ramos

Member: Prof. Leonel Augusto Pires Seabra de Sousa

Member: Prof. Mário Ventim Neves

November 2009

## **Abstract**

Non-destructive testing plays a crucial role in quality management and on ensuring safety of use to a broad range of industrial components especially in aerospace, power generation, automotive, railway and petrochemical applications. From the several non-destructive testing methods, eddy currents evaluation is the preferred method to inspect metallic parts and welding joints searching for flaws and other material discontinuities. Eddy currents evaluation is based on the generation and analysis of electrical currents through the test material.

Friction stir welding is a solid-state joining process executed without any material addiction and at lower temperatures than the fusion temperature of the involved materials. This process leads to lower joint distortions and residual tensions together with excellent mechanical properties. Friction stir welding is seen as a great potential technology but the actual technological state on non-destructive testing isn't able to ensure the detection of defects with structural influence. This work studies a new concept of eddy currents probe by analytical and finite element models together with their experimental validation. This new IOnic probe and a preliminary version of a non-destructive testing system were used to inspect friction stir welds on industrial conditions detecting superficial defects about 60 µm deep.

To extract the maximum advantage from the new probe concept, a tailor-made non-destructive testing system was developed. This new system has a Field Programmable Gate Array based processing core enabling the digital generation and analysis of the probe signals through multiple digital signal processing algorithms. Communication with personal computers is ensured by Ethernet 10/100 or USB 2.0 High Speed interfaces. The proposed system architecture enables to set several combinations of peripherals cards to generate or acquire probe signals. Two different peripheral cards have been developed to interface the IOnic probes. Signal acquisition is guaranteed by a programmable gain amplifier and an analog to digital converter while the signal generation is made through a digital to analog converter and a high output current transconductance amplifier. Together, the two peripherals cards are able to operate the probe within the frequency range from 10 kHz up to 10 MHz.

# Keywords

Non-Destructive Testing, Eddy Currents, Planar Probe, Field Programmable Gate Array, Digital Signal Processing.

### Resumo

O ensaio não destrutivo tem um papel crucial no processo de gestão da qualidade bem como em garantir segurança de utilização a uma vasta gama de componentes para aplicações aeroespaciais, geração de energia, transportes rodoviário e ferroviário e nas industrias química e petrolífera. Dos vários métodos de análise não destrutiva, o ensaio por correntes induzidas (*eddy currents*) é o preferido para inspeccionar componentes metálicos e soldaduras, localizando defeitos e outras descontinuidades materiais. O ensaio por correntes induzidas baseia-se na geração e análise de correntes eléctricas no material a testar.

A soldadura por fricção linear é um processo de ligação no estado sólido levado a cabo sem qualquer adição de material e a temperaturas abaixo das temperaturas de fusão dos materiais envolvidos. Por este processo, é possível obter juntas com uma baixa distorção e baixas tensões residuais e ao mesmo tempo com excelentes características mecânicas. Apesar do seu potencial, o estado actual em matérias de controlo não destrutivo não permite a detecção de defeitos com influência estrutural relevante nas juntas obtidas por este método. Este trabalho estuda um novo conceito de sonda de correntes induzidas através da sua modelação analítica e por elementos finitos bem como através de validação experimental. A nova sonda lOnic em conjunto com um sistema preliminar de ensaios não destrutivo, foram utilizados na inspecção de juntas obtidas pelo processo de fricção linear em condições industriais detectando defeitos superficiais com cerca de 60 µm de profundidade.

Para extrair a máxima performance do novo conceito de sonda, um sistema de ensaio não destrutivo foi especialmente projectado. Este novo sistema possui um núcleo de processamento baseado num dispositivo de lógica programável permitindo a geração e análise dos sinais na sonda através de múltiplos algoritmos de processamento digital de sinal. A comunicação com computadores pessoais é assegurada pelas interfaces Ethernet 10/100 e USB 2.0 *High Speed*. A arquitectura do sistema proposto permite a configuração de múltiplas combinações de periféricos para geração e aquisição dos sinais na sonda. A aquisição de sinais é garantida por um amplificador de ganho programável e um conversor analógico-digital enquanto que a geração de sinais é conseguida através de um conversor digital-analógico e um amplificador de transcondutância com elevada corrente de saída. Em conjunto, os dois periféricos mostraram-se adequados para operar a sonda na gama de frequências desde 10 kHz a 10 MHz.

# Palavras-chave

Ensaio não destrutivo, Correntes Induzidas, Sonda planar, Dispositivo de Lógica Programável, Processamento Digital de sinal.

# **Acronyms**

ADC Analog to Digital Converter

**ALU** Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

ATX Advanced Technology Extended

CAD Computer Aided DesignDAC Digital to Analog ConverterDFT Discrete Fourier Transform

**DIL** Dual In-Line

DSP Digital Signal ProcessingENOB Effective Number of BitsFEM Finite Element Modeling

FIFO First In First Out

**FPGA** Field Programmable Gate Array

FR4 Flame Retardant 4

FSW Friction Stir Welding

GBW Gain-Bandwidth Product

GMI Giant Magneto Impedance

GMR Giant Magneto Resistance

I<sup>2</sup>C Inter-Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IO Input/Output

IP Intellectual PropertyJTAG Joint Test Action GroupLAN Local Area NetworksLED Light Emitting Diode

LVDS Low Voltage Differential Signaling

MAC Media Access ControllerMII Media Independent Interface

MOSFET Metal Oxide Semiconductor Field Electric Transistor

MSPS Mega Samples per Second

MWM Meandering Winding Magnetometer

NCO Numerically Controlled Oscillator

NDT Non-Destructive Testing

OPAMP Operational Amplifier

PCB Printed Circuit Board

PDN Power Distribution Network

PGA Programmable Gain Amplifier

PLB Peripheral Local Bus

POR Power On Reset

RAM Random-Access Memory

**RISC** Reduced Instruction Set Computer

**ROM** Read Only Memory

**SIMM** Single In-Line Memory Module

SPI Serial Peripheral Interface

**SQUID** Superconducting Quantum Interference Devices

**THD** Total Harmonic Distortion

USB Universal Serial BusVBE Voltage Base to Emitter

# **Acknowledgments**

First of all, I would like to thank my supervisors, Professor Moisés Piedade and Professor Pedro Ramos for the support, guidance and helpful suggestions through the elaboration of this dissertation. I sincerely thank them for the knowledge, experience and inspiration they brought to my work during the last five years.

A special thanks to the Professor Telmo Santos and Professor Pedro Vilaça for all the support regarding mechanical technology and non-destructive testing applications. Working with them has been an extremely valuable experience.

I would like to express my gratitude for all my colleagues and friends at Instituto Superior Técnico. To them, I thank the friendship and company during the lazy days and long nights where this work has been made. Also, I would like to thank Mr. Pina dos Santos for his valuable advices.

I would like to show my appreciation to my girlfriend Ana Margarida for the motivation and patience when it was most required.

This work is dedicated to my parents Filipe and Fernanda and my sister Daniela. I thank them for the unconditional support and encouragement.

Luis Boosodo

# **Table of contents**

| Abstract                                      |     |

|-----------------------------------------------|-----|

| Keywords                                      | Ī   |

| Resumo                                        | II  |

| Palavras-chave                                | II  |

| Acronyms                                      | III |

| Acknowledgments                               | V   |

| Table of contents                             | VII |

| List of figures                               | IX  |

| List of tables                                | XI  |

| Chapter 1 – Introduction                      | 1   |

| 1.1 Purpose and motivation                    | 1   |

| 1.2 Goals and challenges                      | 2   |

| 1.3 Document organization                     | 2   |

| Chapter 2 – Eddy currents evaluation overview | 3   |

| 2.1 Introduction                              | 3   |

| 2.2 Conventional eddy currents evaluation     | 3   |

| 2.2.1 Eddy currents phenomenon                | 4   |

| 2.2.2 Depth of penetration                    | 4   |

| 2.2.3 Impedance plane                         | 5   |

| 2.2.4 Eddy currents probes                    | 6   |

| 2.2.5 Advantages of eddy currents evaluation  | 7   |

| 2.3 Friction Stir Welding: A challenge on NDT | 7   |

| 2.4 State-of-the-art                          | 9   |

| 2.5 Summary                                   | 10  |

| Chapter 3 – IOnic Probe                       | 11  |

| 3.1 Introduction                              | 11  |

| 3.2 Probe morphology and operation theory     | 11  |

| 3.2.1 Electromagnetic Phenomena               | 12  |

| 3.2.2 Finite Element Modeling                 | 13  |

| 3.3 Preliminary NDT system                    | 17  |

| 3.3.1 Probe driver                            | 18  |

| 3.3.2 Amplitude and phase difference detector | 19  |

| 3.3.3 Analog Electronic System Prototype      | 20  |

| 3.4 IOnic probe concept validation            | 20  |

| 3.5 IOnic concept advantages                  | 23  |

| 3.6 IOnic concept variations                            | 24 |

|---------------------------------------------------------|----|

| 3.6.1 IOnic Plus                                        | 24 |

| 3.6.2 IOnic Matrix                                      | 26 |

| 3.6.3 IOnic Active                                      | 27 |

| 3.7 Summary                                             | 27 |

| Chapter 4 – ECscan NDT System Hardware                  | 29 |

| 4.1 Introduction                                        | 29 |

| 4.2 ECscan Main Board                                   | 30 |

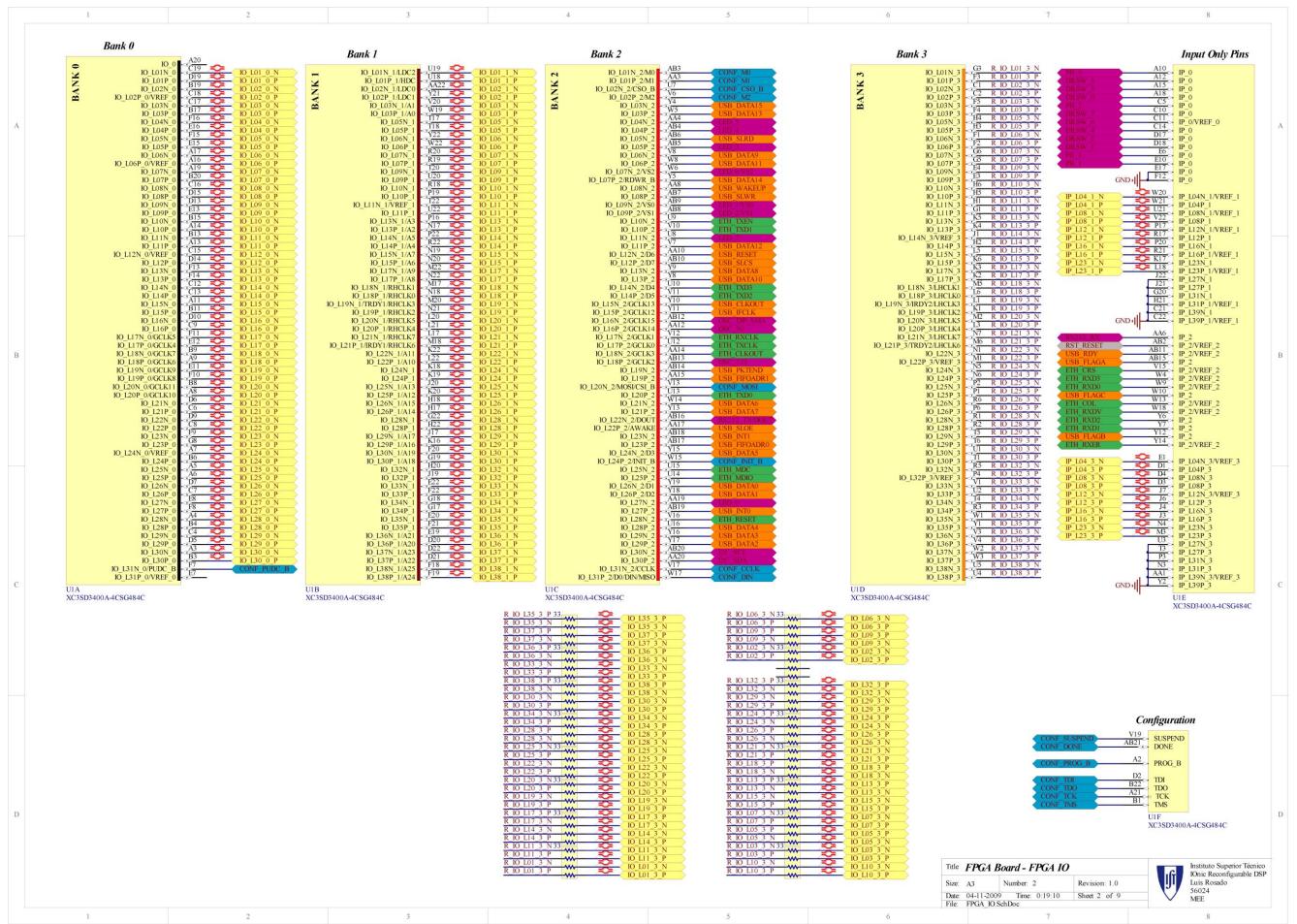

| 4.2.1 FPGA based processing core                        | 31 |

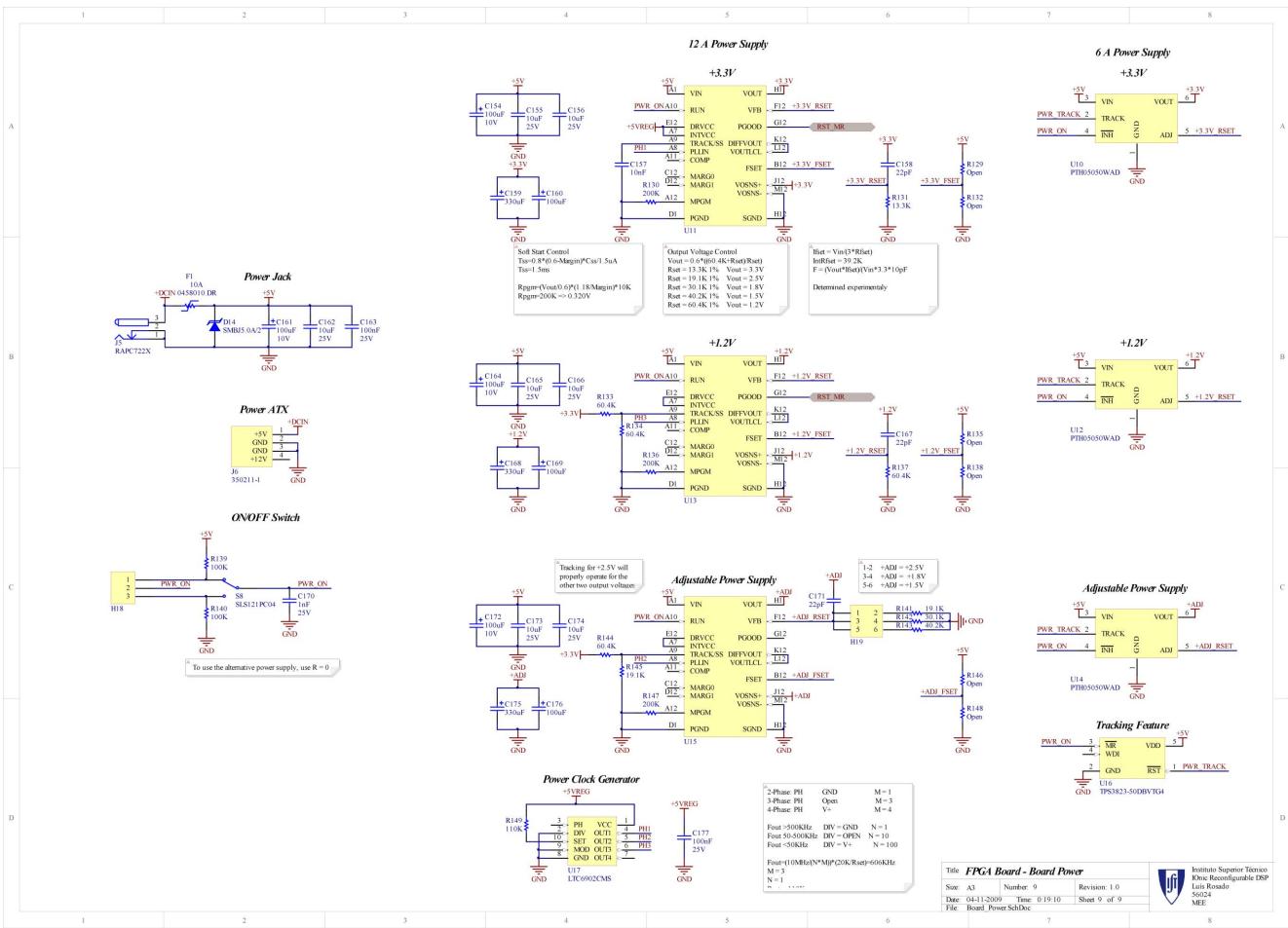

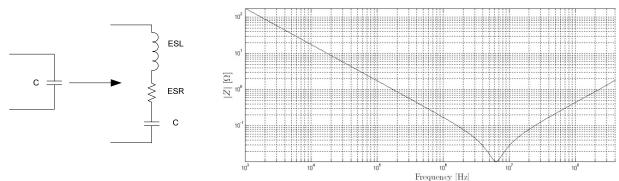

| 4.2.2 Power Management and Power Distribution Network   | 33 |

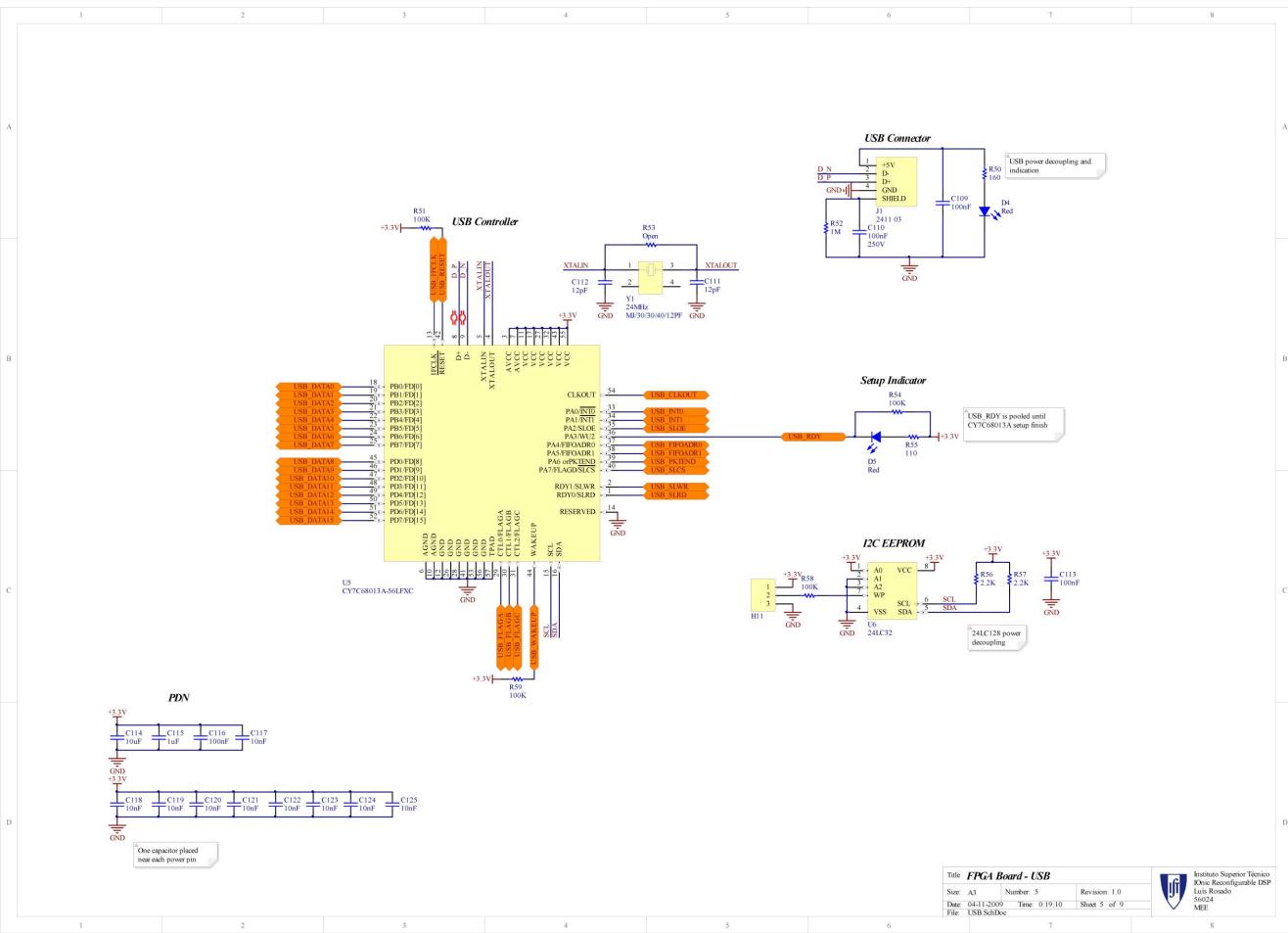

| 4.2.3 USB Interface                                     | 33 |

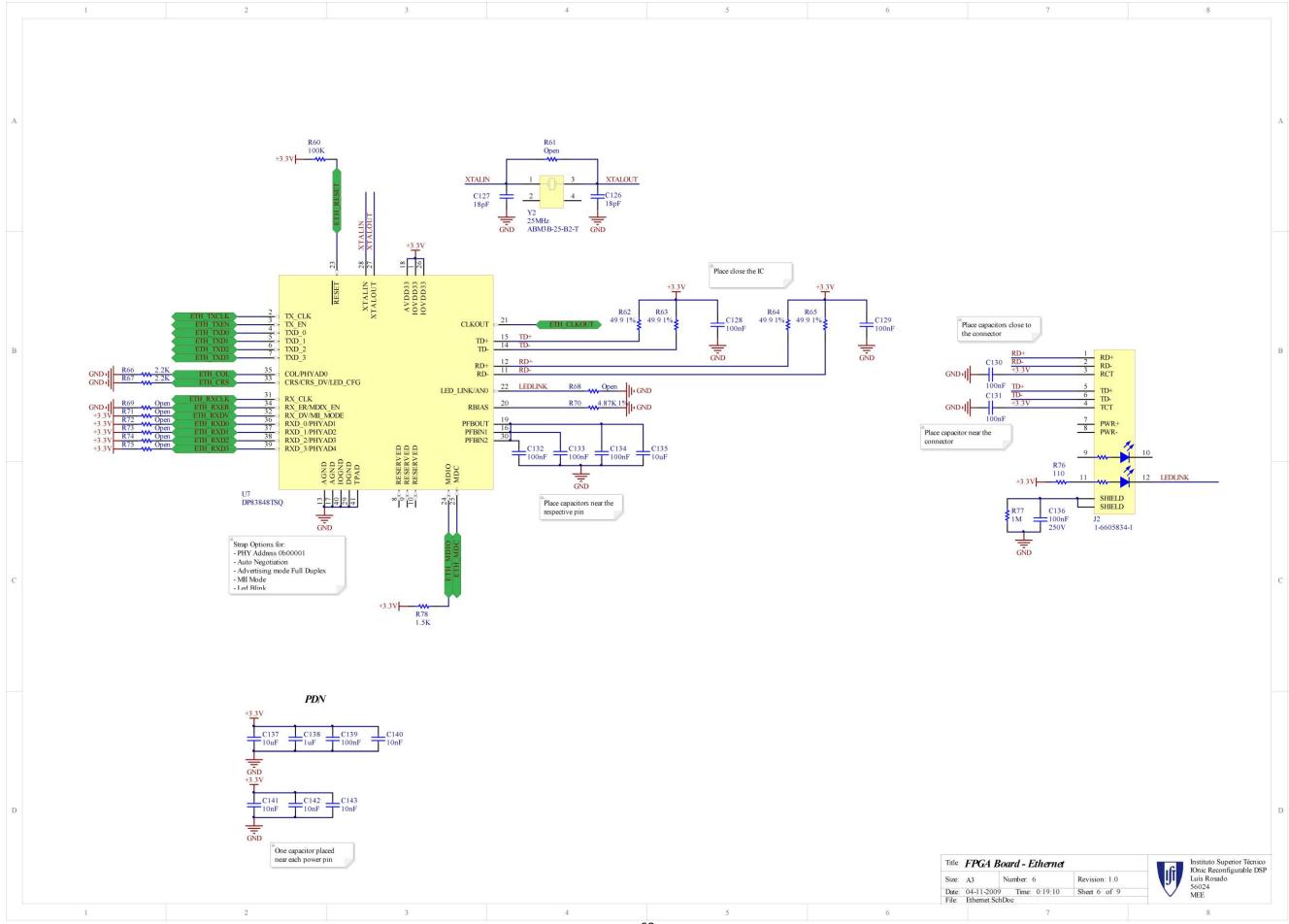

| 4.2.4 Ethernet Interface                                | 36 |

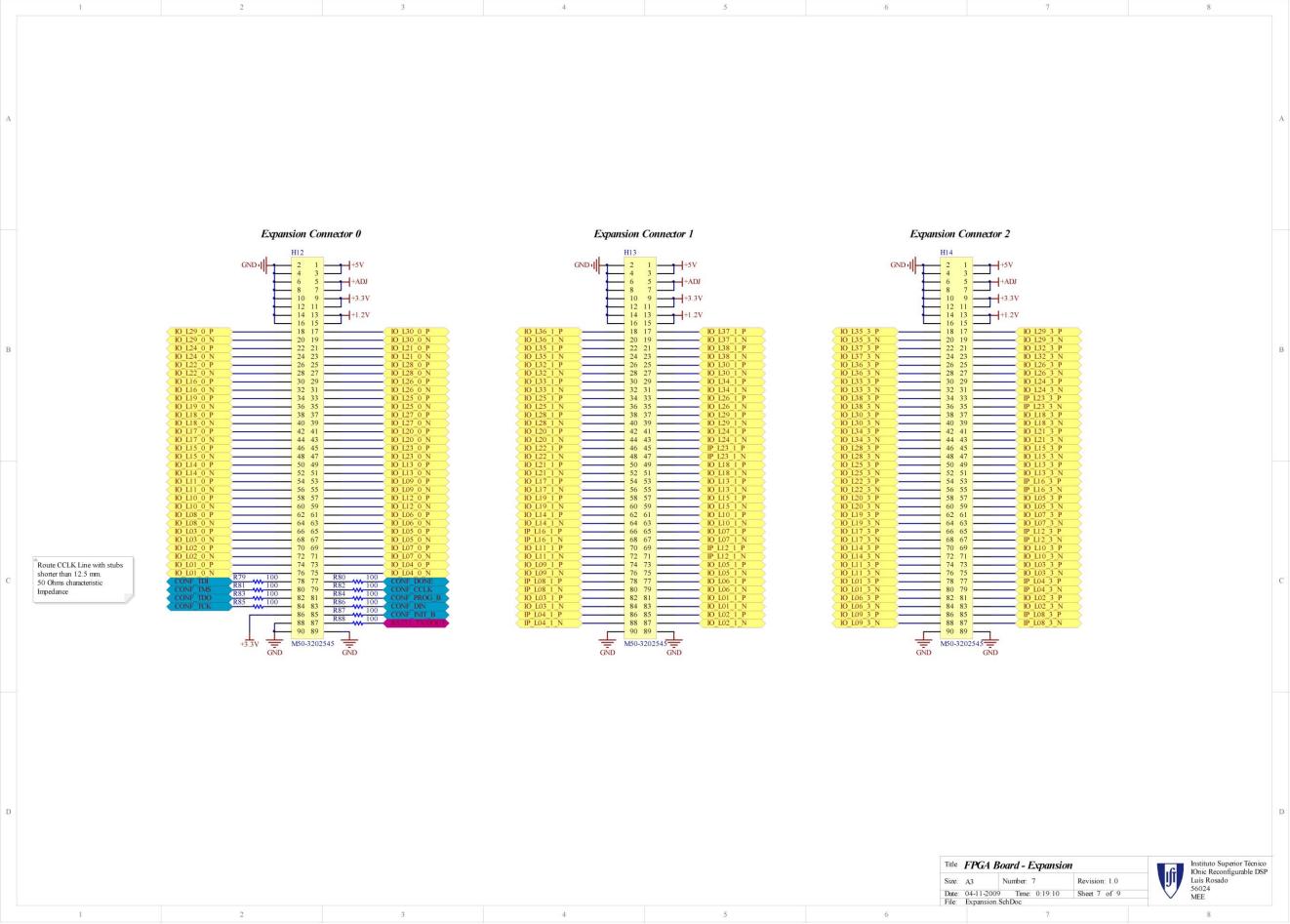

| 4.2.5 Peripheral Connectors                             | 37 |

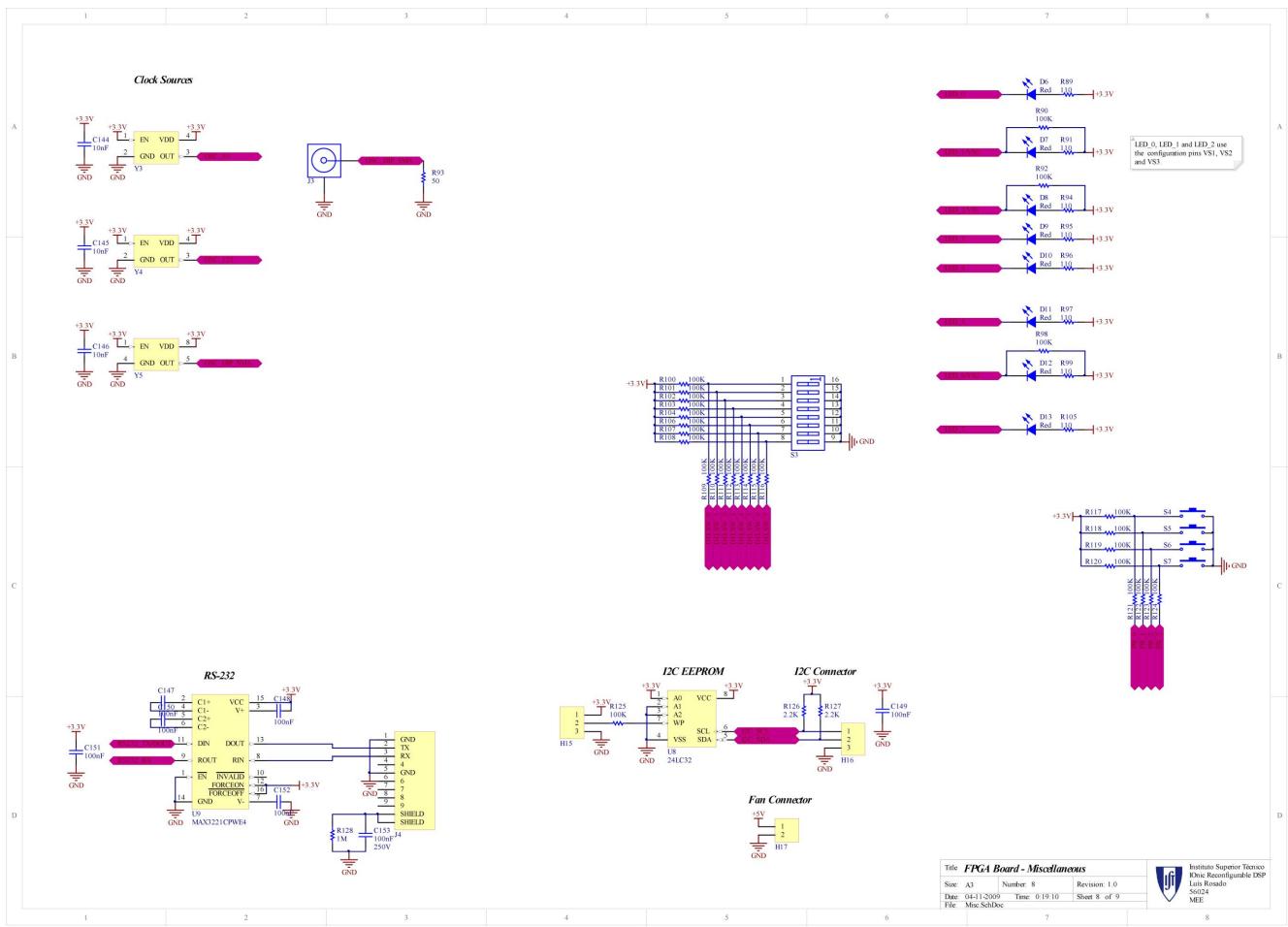

| 4.2.6 Other Features                                    | 38 |

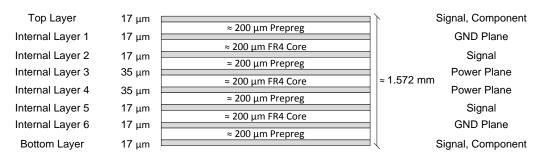

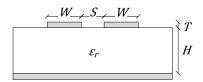

| 4.2.7 PCB Stack up and Impedance Control considerations | 38 |

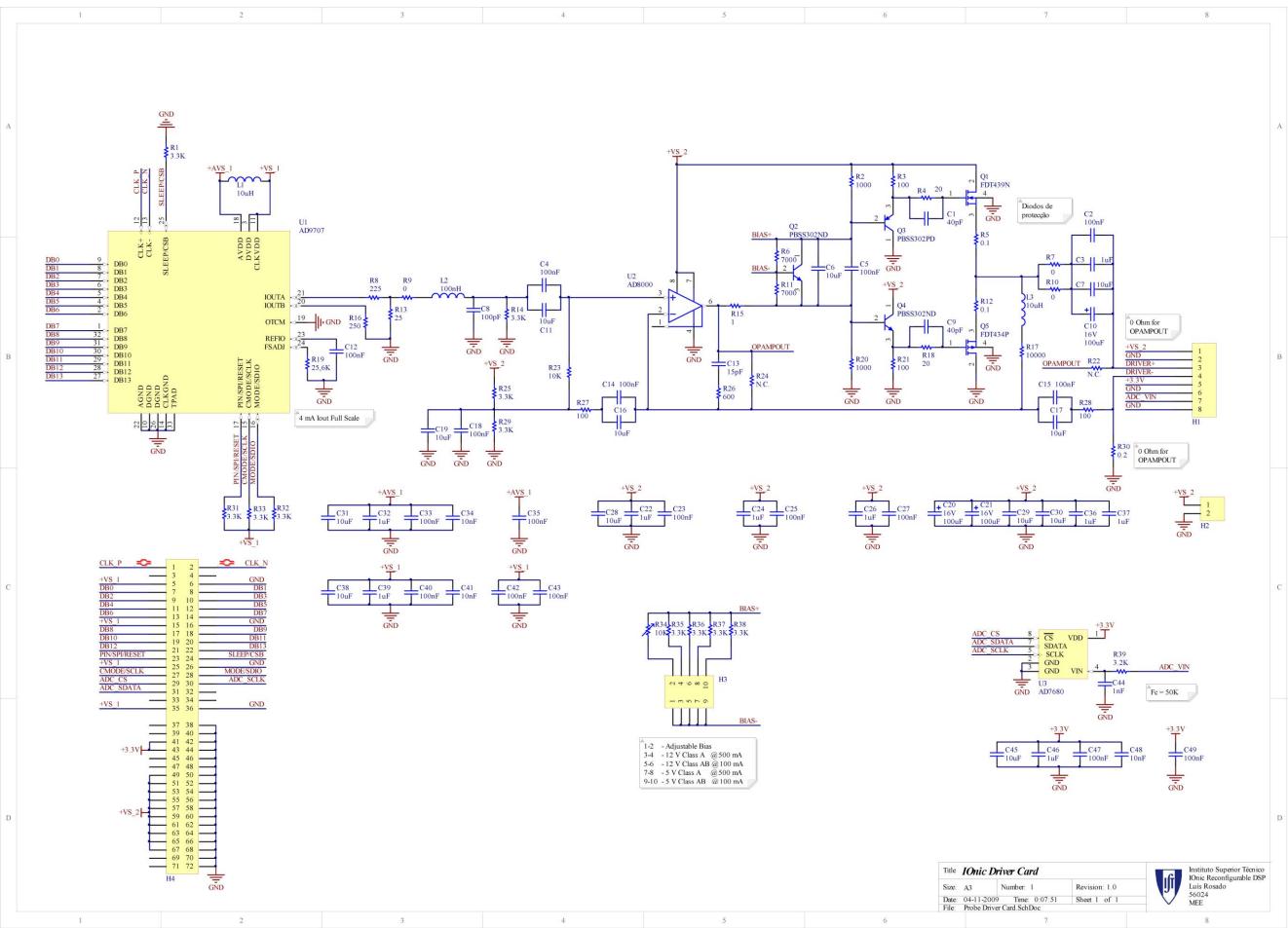

| 4.3 IOnic Driver Card                                   | 39 |

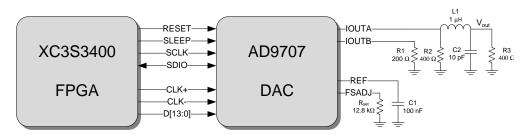

| 4.3.1 Digital to Analog Converter                       | 39 |

| 4.3.2 Driver Circuit                                    | 40 |

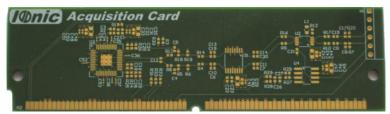

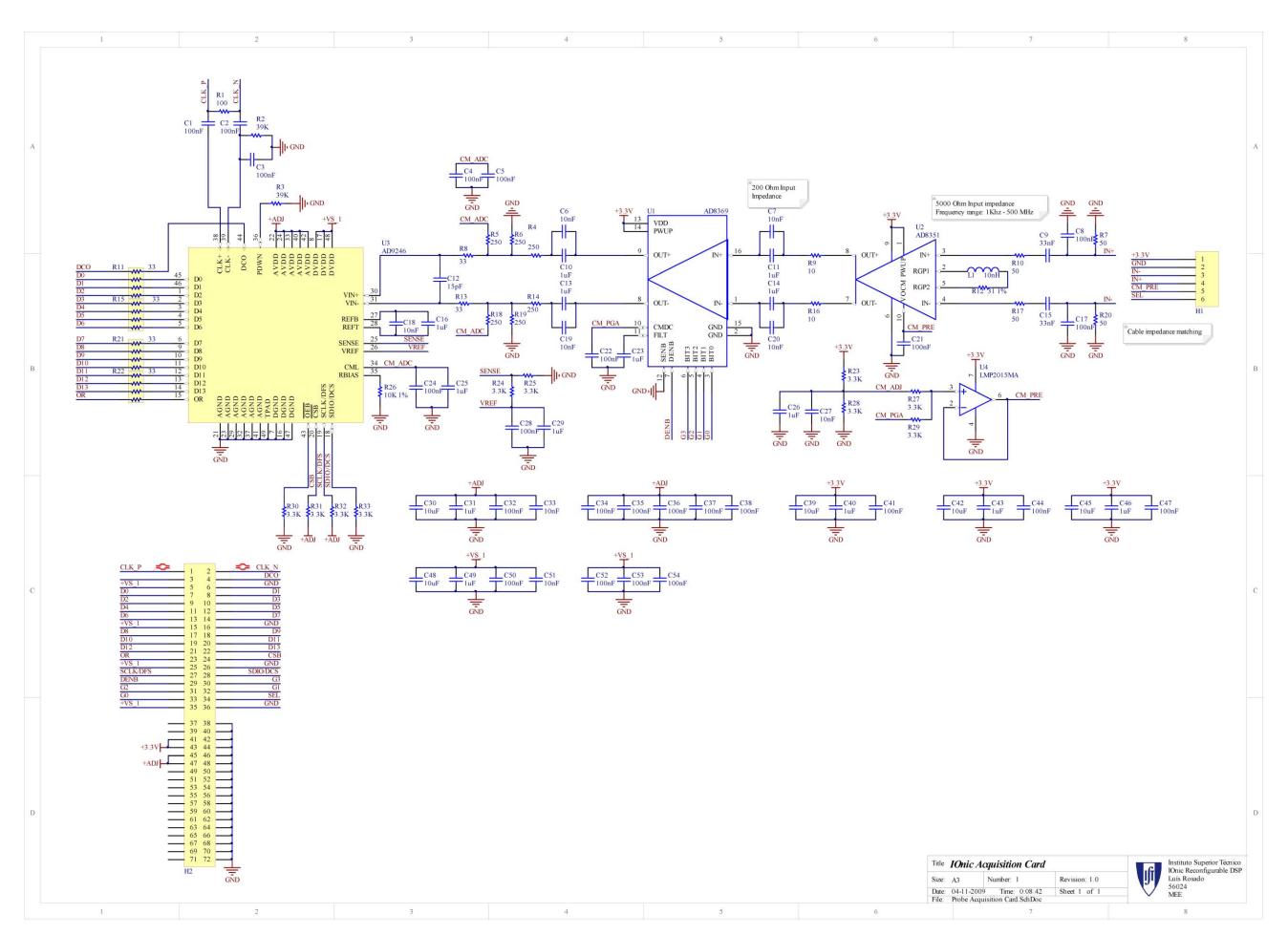

| 4.4 IOnic Acquisition Card                              | 46 |

| 4.4.1 Analog to Digital Converter                       | 46 |

| 4.4.2 Programmable Gain Amplifier                       | 47 |

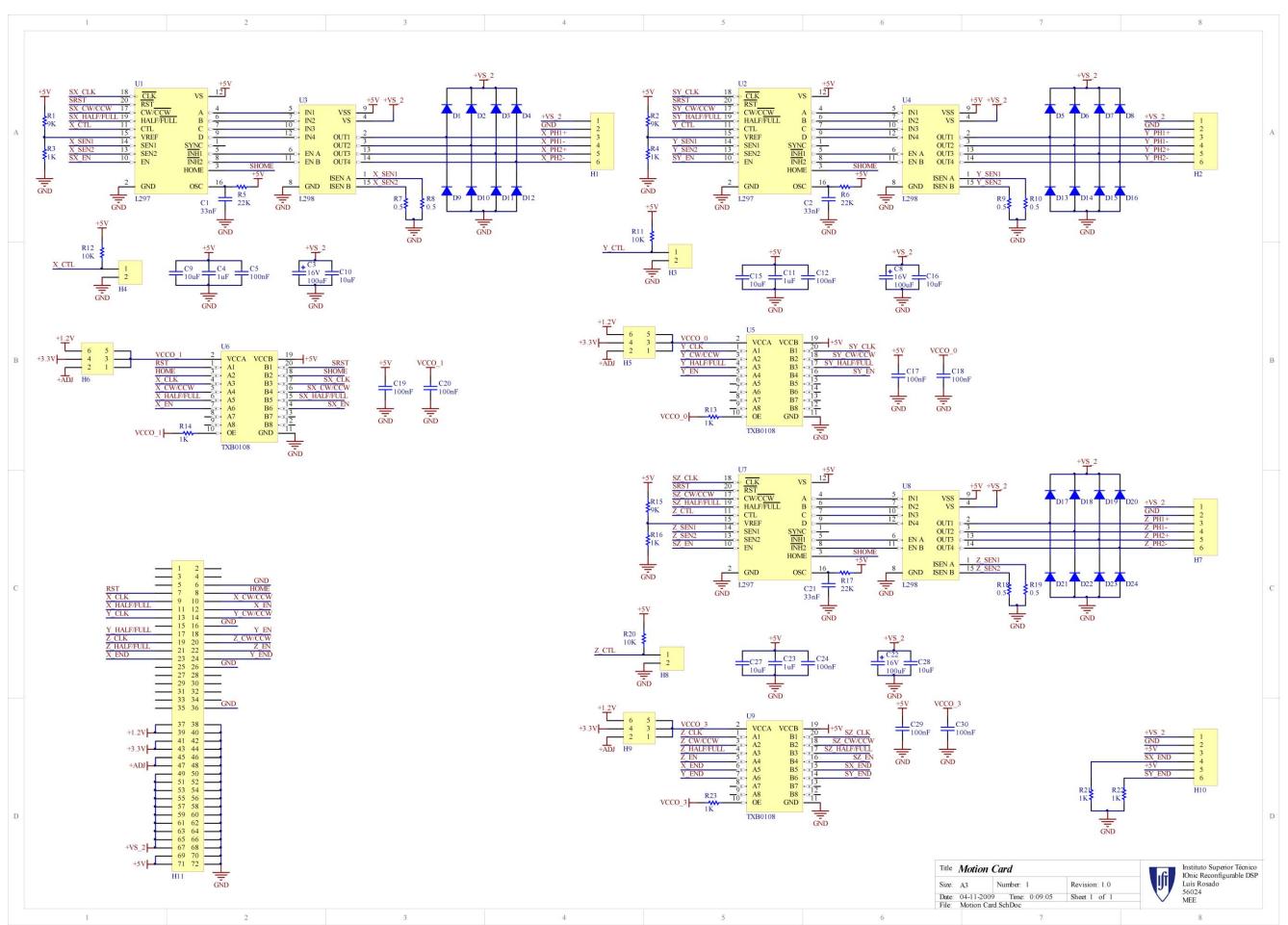

| 4.5 Motion Control Card                                 | 50 |

| 4.6 Budget and Prototyping                              | 50 |

| 4.7 Summary                                             | 52 |

| Chapter 5 – ECscan NDT System Software                  | 53 |

| 5.1 Introduction                                        | 53 |

| 5.2 Embedded application development                    | 53 |

| 5.2.1 USB FIFO Core and CY7C68013A firmware             | 54 |

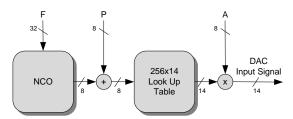

| 5.2.2 Signal Generator Core                             | 56 |

| 5.3 Summary                                             | 58 |

| Chapter 6 - Conclusions                                 | 59 |

| References                                              | 61 |

| Appendix I - ECscan Schematics                          | 63 |

| Appendix II - Power Distribution Network Design         | 79 |

| Appendix III - Microstrip and Stripline Design          | 81 |

| Appendix IV - ECscan System Budget                      | 83 |

| Appendix V - USB_FIFO VHDL Description                  | 85 |

| Appendix VI - Signal Generator VHDL Description         | 93 |

# List of figures

| Figure 2.1 - Eddy currents density generated by a coil, sectional view                                  | 4    |

|---------------------------------------------------------------------------------------------------------|------|

| Figure 2.2 - Standard depth of penetration for aluminum ( $\mu$ 0 = 1.000022 and $\sigma$ = 3.54 × 107) | 5    |

| Figure 2.3 - Impedance plane analysis.                                                                  | 5    |

| Figure 2.4 - FSW process [12].                                                                          | 7    |

| Figure 2.5 - Sectional view of a friction stir weld bead and their possible defects [13]                | 8    |

| Figure 3.1 - IOnic probe tri-dimensional view. A) Driver trace, B) Pickup coil                          | .11  |

| Figure 3.2 - Electromagnetic relations on an infinite, straight and current carrying wire               | .12  |

| Figure 3.3 - Current carrying wire over an aluminum piece. A - Magnetic field, B - Eddy currents        | .13  |

| Figure 3.4 - Eddy currents induced by a limited length current carrying wire                            | .13  |

| Figure 3.5 - Eddy currents induced with the wire array.                                                 | .14  |

| Figure 3.6 - Basic probe model and superficial eddy currents                                            | .14  |

| Figure 3.7 - Advanced probe model and superficial eddy currents.                                        | . 15 |

| Figure 3.8 - FEM Convergence analysis                                                                   | . 15 |

| Figure 3.9 - Defect characterization sweep.                                                             | .16  |

| Figure 3.10 - Real and imaginary part of the ratio $Uout/I$ along the sweep                             | .16  |

| Figure 3.11 - Preliminary NDT system overview                                                           | . 17 |

| Figure 3.12 - Analog electronics system functional diagram.                                             | .18  |

| Figure 3.13 - Probe driver circuit                                                                      | .18  |

| Figure 3.14 - Amplitude and phase difference detectors circuits                                         | .19  |

| Figure 3.15 - Analog electronics system prototype                                                       | .20  |

| Figure 3.16 - Manufactured IOnic probe.                                                                 | .20  |

| Figure 3.17 - Experimental and FEM results for the standard defect.                                     | .21  |

| Figure 3.18 - Results for the FSW bead on plate for 50, 100 and 250 kHz                                 | .21  |

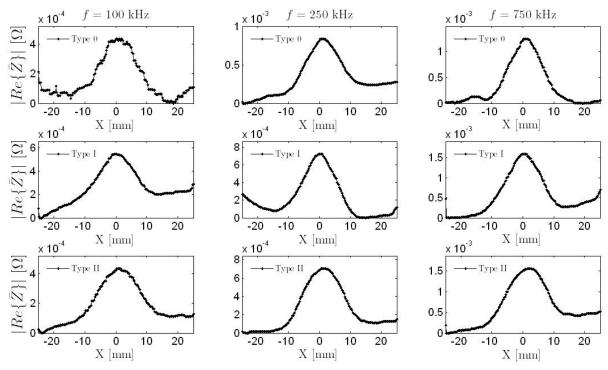

| Figure 3.19 - Transversal macrographs of three different FSW defective weld beads                       | .22  |

| Figure 3.20 - Results for the FSW weld beads with defect types 0, I and II for 50, 100 and 250 kHz.     | 22   |

| Figure 3.21 - Results for the FSW weld beads with a conventional planar probe                           | .23  |

| Figure 3.22 - IOnic Plus morphology and prototype.                                                      | . 24 |

| Figure 3.23 - IOnic Plus standard defect inspection results.                                            | . 25 |

| Figure 3.24 - IOnic Plus static operation mode configurations.                                          | . 25 |

| Figure 3.25 - IOnic Plus driver trace connections for the dynamic operation mode                        | . 26 |

| Figure 3.26 - IOnic Array illustration.                                                                 | .26  |

| Figure 3.27 - IOnic Active bottom view.                                                                 | . 27 |

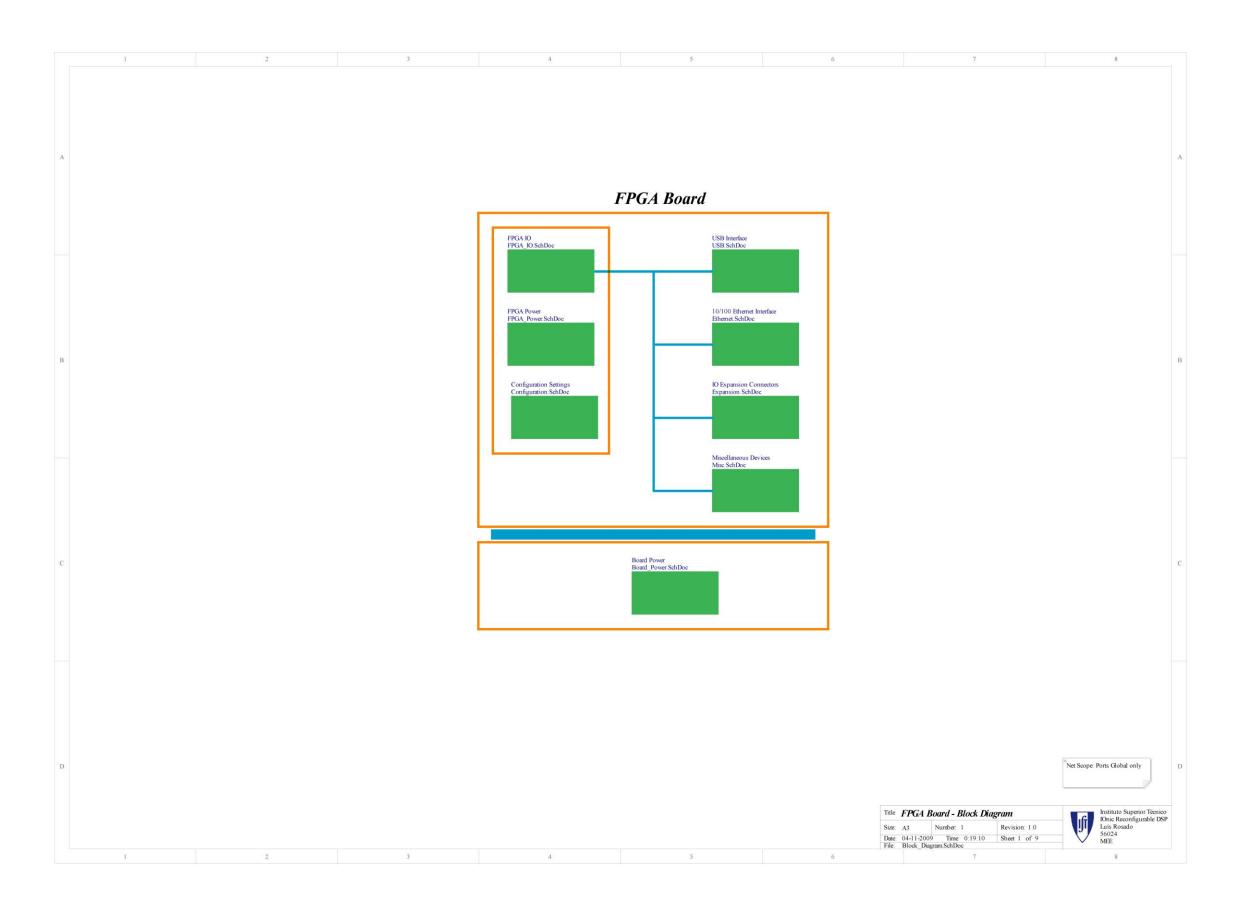

| Figure 4.1 - ECscan system Overview.                                                                    | . 29 |

| Figure 4.2 - Main board functional diagram.                                                             | .30  |

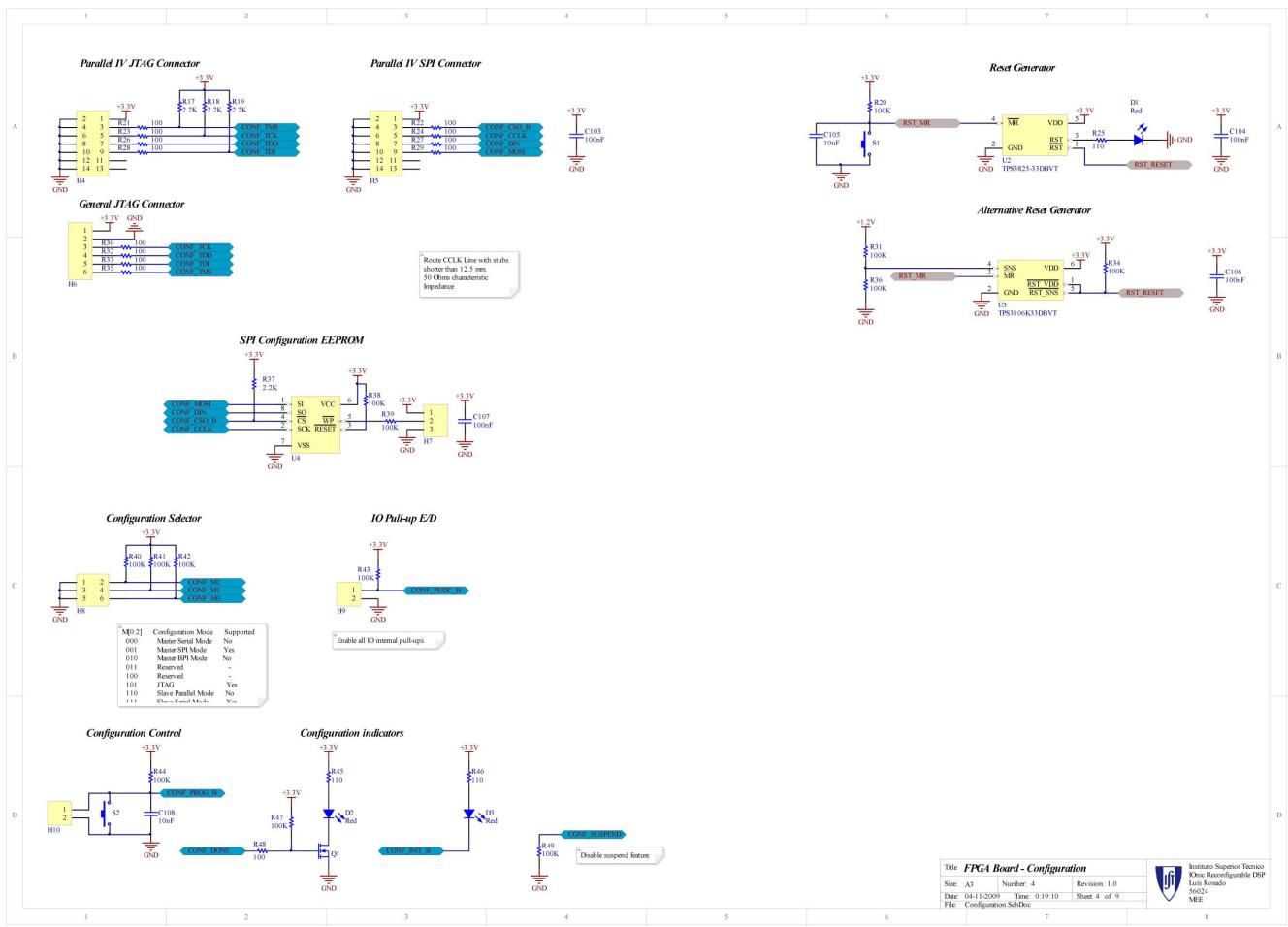

| Figure 4.3 - FPGA configuration sources and control.                                                    | .32  |

| Figure 4.4 - PTH05050 connections and tracking Feature.                                                 | . 33 |

| Figure 4.5 - Cypress FX2 USB CY7C68013A to FPGA connections                                             | 34   |

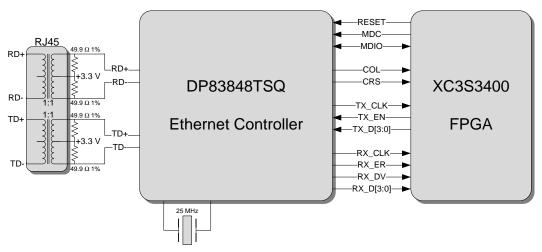

| Figure 4.6 - National Semiconductor DP83848TSQ to FPGA connections                                 | 36    |

|----------------------------------------------------------------------------------------------------|-------|

| Figure 4.7 - Main board features                                                                   | 38    |

| Figure 4.8 - PCB Stackup and Layers.                                                               | 38    |

| Figure 4.9 - AD9707 DAC to FPGA connections                                                        | 39    |

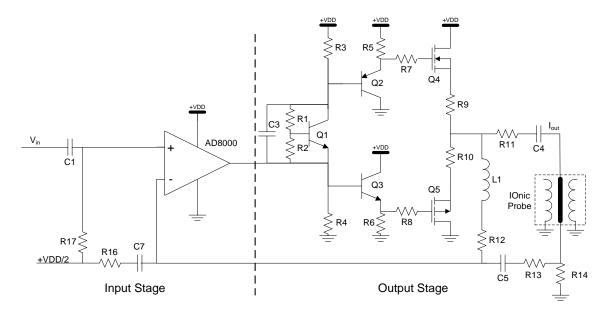

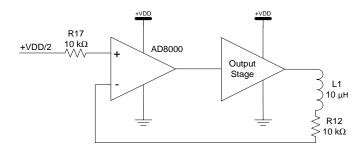

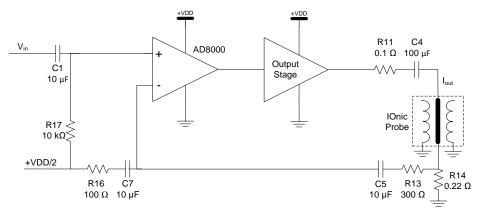

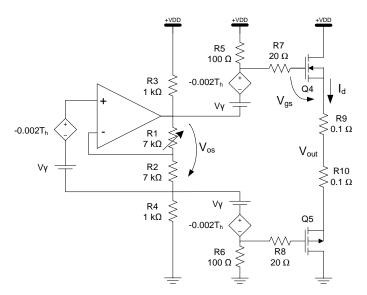

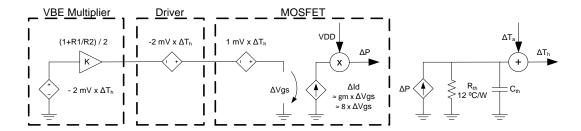

| Figure 4.10 - Driver Circuit                                                                       | 40    |

| Figure 4.11 - Input stage and DC feedback                                                          | 41    |

| Figure 4.12 - Probe driver circuit input stage and AC feedback                                     | 41    |

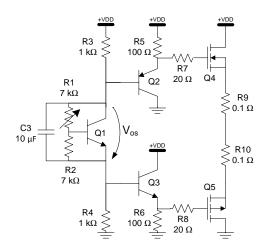

| Figure 4.13 - Output Stage                                                                         | 42    |

| Figure 4.14 - Output stage thermal compensation mechanism                                          | 42    |

| Figure 4.15 - Incremental model for thermal compensation.                                          | 43    |

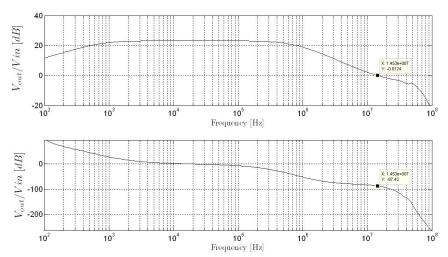

| Figure 4.16 - Probe driver circuit voltage open loop frequency response                            | 44    |

| Figure 4.17 - Probe driver circuit closed loop frequency response                                  | 44    |

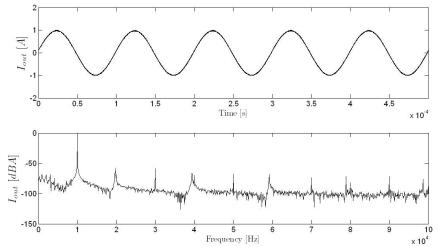

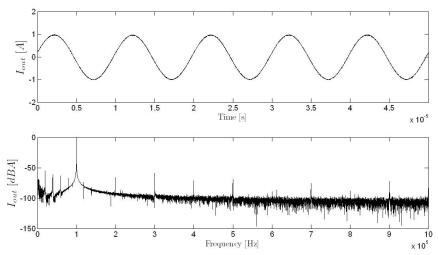

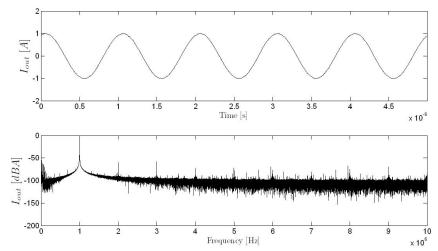

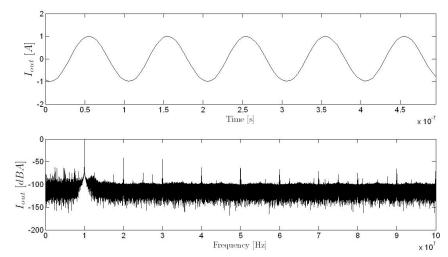

| Figure 4.18 - Probe driver circuit performance for 10 kHz, 1 A amplitude sine wave output current. | 45    |

| Figure 4.19 - Probe driver circuit performance for 100 kHz, 1 A amplitude sine wave output current | i. 45 |

| Figure 4.20 - Probe driver circuit performance for 1 MHz, 1 A amplitude sine wave output current   | 45    |

| Figure 4.21 - Probe driver circuit performance for 10 MHz, 1 A amplitude sine wave output current. | 46    |

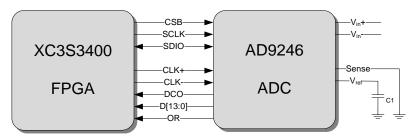

| Figure 4.22 - AD9246 ADC to FPGA interface.                                                        | 47    |

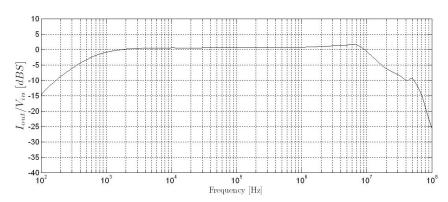

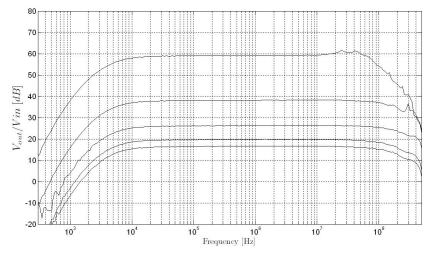

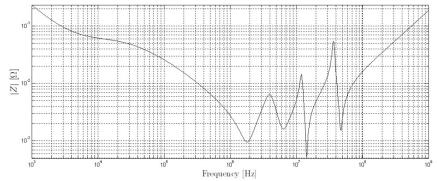

| Figure 4.23 - PGA frequency response for the selected gains                                        | 48    |

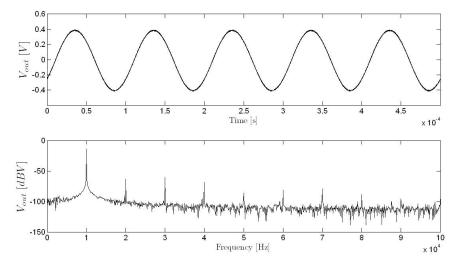

| Figure 4.24 - PGA performance for 10 kHz, 0.5 mV amplitude sine wave input voltage                 | 48    |

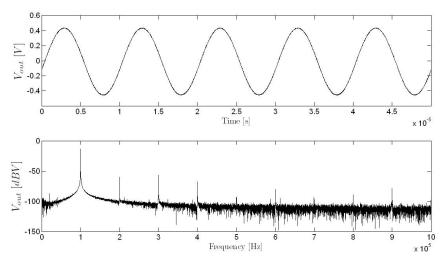

| Figure 4.25 - PGA performance for 100 kHz, 0.5 mV amplitude sine wave input voltage                | 49    |

| Figure 4.26 - PGA performance for 1 MHz, 0.5 mV amplitude sine wave input voltage                  | 49    |

| Figure 4.27 - PGA performance for 10 MHz, 0.5 mV amplitude sine wave input voltage                 | 49    |

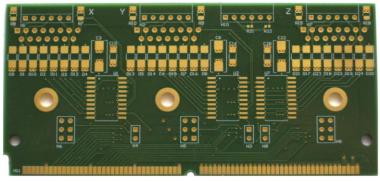

| Figure 4.28 - Main Board PCBs                                                                      | 51    |

| Figure 4.29 - IOnic Driver Card PCB.                                                               | 51    |

| Figure 4.30 - IOnic Acquisition Card PCB                                                           | 52    |

| Figure 4.31 - Motion Control Card PCB                                                              | 52    |

| Figure 5.1 - Embedded application software blocks                                                  | 54    |

| Figure 5.2 - Signal Generator logic.                                                               | 56    |

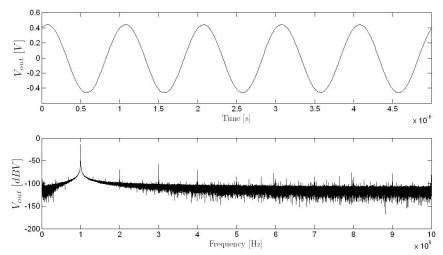

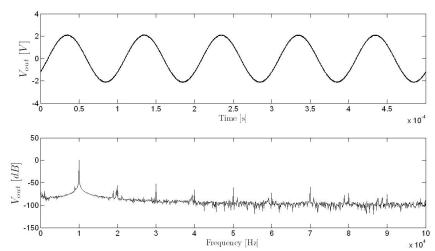

| Figure 5.3 - 10 kHz, 2 V amplitude sine wave synthesized by the signal generator core              | 57    |

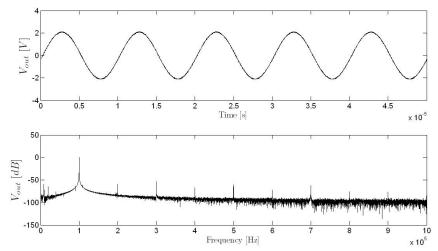

| Figure 5.4 - 100 kHz, 2 V amplitude sine wave synthesized by the signal generator core             | 57    |

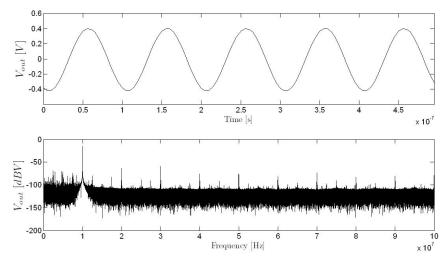

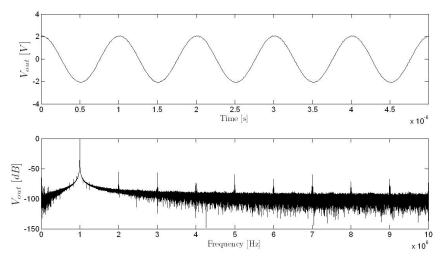

| Figure 5.5 - 1 MHz, 2 V amplitude sine wave synthesized by the signal generator core               | 58    |

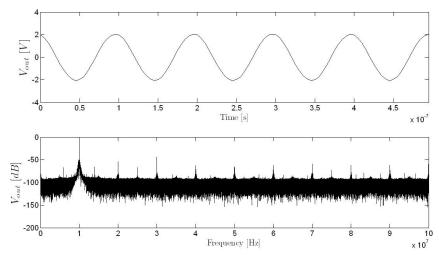

| Figure 5.6 - 10 MHz, 2 V amplitude sine wave synthesized by the signal generator core              | 58    |

# List of tables

| Table 2.1 - Historical outline of eddy currents evaluation                | 3  |

|---------------------------------------------------------------------------|----|

| Table 4.1 - XC3S3400A-4CSG484C FPGA characteristics                       | 31 |

| Table 4.2 - Configuration mode selection.                                 | 32 |

| Table 4.3 - CY7C68013A FIFO interface with the FPGA.                      | 35 |

| Table 4.4 - Parameter values for the differential microstrip lines design | 35 |

| Table 4.5 - DP83848TSQ interface with the FPGA.                           | 37 |

| Table 4.6 - Resources on each peripheral connector.                       | 37 |

| Table 4.7 - DAC FPGA interface                                            | 39 |

| Table 4.8 - Probe Driver Circuit THD.                                     | 46 |

| Table 4.9 - ADC FPGA Interface.                                           | 47 |

| Table 4.10 - Gain codes and overall gain.                                 | 48 |

| Table 4.11 - Programmable gain amplifier THD.                             | 50 |

| Table 4.12 - L297 stepper motor controller to FPGA interface.             | 50 |

| Table 4.13 - ECscan system overall production cost (without assembly)     | 50 |

| Table 5.1 - USB FIFO Core Entities                                        | 55 |

| Table 5.2 - USB FIFO Core control register                                | 55 |

| Table 5.3 - USB FIFO Core status register.                                | 55 |

| Table 5.4 - Signal Generator Core Entities                                | 56 |

# Chapter 1 - Introduction

### 1.1 Purpose and motivation

Non-Destructive Testing (NDT) comprise the techniques that are based on the application of physical principles employed for the purpose of determining the characteristics of materials and for detecting and assessing the flaws and harmful defects without any change on their usefulness or serviceability [1]. These techniques concern all aspects of material carachterization, their microstructure, texture, morphology, and physical and chemical properties [2]. NDT has gained in importance as a result of the rapid technological progress made during the past half-century and is considered today one of the fastest growing technologies.

NDT plays a crucial role in ensuring cost effective operation, safety of use and reliability of a wide range of industrial components especially on aerospace, power generation, automotive, railway and petrochemical applications. Although NDT was originally intended to be applied only for human safety reasons, nowadays, it is widely accepted as a cost saving technique in the quality assurance process performed by almost all manufacturing companies.

There is a broad range of NDT methods based on different physical principles but the most commonly used are ultra-sonic, eddy currents evaluation, X-radiography, magnetic particles inspection and dye penetrant application [3]. The choice between these methods should take in account safety, economic and efficiency issues. Eddy currents evaluation is the preferred NDT method for superficial and internal flaws detection on conducting materials especially on metal welding applications. Eddy currents evaluation is based on electromagnetic induction and analysis of electrical currents on conductive materials. This method is used for thickness measurements, corrosion evaluation, electrical conductivity measurements, magnetic permeability measurements and flaw detection. The principal advantages on using this technology are that surface preparation is minimal and it is a quite intuitive method, setting aside the need for highly qualified personnel.

The development of new welding and joining processes leads to a constant demand on improved NDT techniques. In fact, the quality assessment of Friction Stir Welding (FSW) remains an actual paradigm on NDT technology. As an example, the defects created on friction stir welds are characterized by no physical material discontinuities with very low size and low energy reflection effect leading to increased difficulties in their detection [4]. In order to increase the defects detection on such applications, a new type of eddy currents probe was designed and patented [5].

The new IOnic probe is based on an entirely new concept and allows enhanced probe lift-off immunity and improved sensitivity for micro size defects. To extract the maximum advantage from this new technology it is essential the study of its operation theory together with the development of a tailor-made electronic system featuring the digital generation and processing of the probe signals.

## 1.2 Goals and challenges

The main goal of this work is to build a NDT system based on the new IOnic probes. To accomplish this task, three key objectives have been established:

- Study the IOnic probe operation theory with Finite Element Modeling (FEM) and experimental validation;

- Build a digital signal processing system to use together with the new probe. This new system

features a Field Programmable Gate Array (FPGA) processing core, communication interfaces

and conversion devices attached to analog electronics to interface the probe;

- Design an embedded software application to control the signal generation and acquisition of the probe signals. The application should communicate with a personal computer to exchange characterization parameters and data.

The central challenge is to design high speed analog, data conversion and digital processing electronic to handle the IOnic probe. Driving the probe along a wide range of frequencies will permit to extract maximum information about the defects presence, thus the target frequency operation range for probe stimulus was set from 10 kHz to 10 MHz.

## 1.3 Document organization

Chapter 2 includes an overview on eddy currents evaluation covering the associated physical phenomenon, applications and the state-of-the-art on this topic. Some considerations on FSW process are presented. The purpose of this chapter is to transmit to the reader an essential background to understand the next content.

On the third chapter, the innovative concept of IOnic probe and their electromagnetic simulation using a FEM analysis tool is presented. Further content on this chapter describes the design and application of a preliminary version of the NDT system used for the experimental validation of the IOnic design. Results on inspecting FSW specimens are included highlighting the potential of the probe on such application.

Chapter 4 introduces a new approach to handle the probes. This new system addresses the Digital Signal Processing (DSP) of the probe signals, in order to overcome the limitations found in the first approach. Emphasis is given to the analog electronics designed to interface the probe including their dynamic characterization results.

In Chapter 5, an embedded software application designed to the new system is presented. Some considerations about their architecture are discussed and the design of the application cores is described.

Finally, some conclusions about the achieved results and future work suggestions are presented in Chapter 6.

# Chapter 2 – Eddy currents evaluation overview

#### 2.1 Introduction

Even though the validation of eddy currents physical principle enunciated by Faraday dates back to 1851 when Jean Bernard Léon Foucault demonstrated that electrical currents are set up in a copper disk moving in a inhomogeneous magnetic field, the first recorded eddy currents test was performed in 1879 by Hughes [6]. At that time, Hughes was able to distinguish the difference between some metals by registering the coil inductance variation when approaching the metals to the coil. On 1926, the first eddy currents based instrument with the ability to measure metal thickness was developed. Through World War II and the early 1940s, further developments resulted in better and more practical eddy currents instruments. The principal discoveries, observations and explanations of eddy currents phenomenon are listed on Table 2.1.

Table 2.1 - Historical outline of eddy currents evaluation.

| Individual                    | Year | Description                                                              |

|-------------------------------|------|--------------------------------------------------------------------------|

| H.C. Oersted                  | 1819 | Change of electric current affected a magnet                             |

| W. Sturgeon                   | 1823 | Copper wire around a horseshoe produced an electromagnet                 |

| Gamby                         | 1824 | Oscillations of suspended bar magnet damped by presence of metal plate   |

| M. Faraday                    | 1832 | Law of electromagnetic induction                                         |

| J. B.Foucault                 | 1851 | Demonstrated existence of eddy currents                                  |

| D.E. Hughes                   | 1879 | Electric pulses from a microphone coil to induce eddy currents in metals |

| F. Krantz                     | 1920 | Eddy currents thickness measurements                                     |

| C. Farrow                     | 1926 | Eddy currents inspection of steel tubes on an industrial scale           |

| Reutlingen Institute, Germany | 1948 | Development of eddy currents instrumentation                             |

| F. Förster                    | 1952 | Impedance plane diagrams                                                 |

Recently, a confluence of developments in the fields of electronics, computer technology, simulation tools and signal processing is contributing to exciting developments and unprecedented performance on eddy currents evaluation [7].

# 2.2 Conventional eddy currents evaluation

An alternating current made to flow in a coil produces an alternating magnetic field around it. This coil, when brought close to the surface of a metallic material, induces an eddy current in the material due to electromagnetic induction generally parallel to the coil winding, Figure 2.1. These eddy currents, in turn, will change the magnetic field disposition. This alteration may be detected either with a magnetic field sensitive sensor or by the change in the original coil impedance.

Figure 2.1 - Eddy currents density generated by a coil, sectional view.

#### 2.2.1 Eddy currents phenomenon

Eddy currents phenomenon can be explained using Maxwell equations. The involved electromagnetic relations are

$$\oint_{S} \vec{H} \, d\vec{l} = I_{S} + \frac{d\phi_{\vec{D},S}}{dt}, \quad \vec{D} = \varepsilon \vec{E} \tag{2.1}$$

$$\oint_{P} \vec{E} \ d\vec{l} = -\frac{d\phi_{\vec{B},P}}{dt}, \quad \vec{B} = \mu \vec{H}.$$

(2.2)

Assuming a one loop coil called L close to a metallic material, and S an orthogonal and concentric surface around the coil, and that the frequency is low enough to discard the displacement current term in (2.1), the magnetic field lines around L are governed by

$$\oint_{S} \vec{H} \, d\vec{l} = I_{L}. \tag{2.3}$$

Now, considering P as a surface defined on the material and dA their area element, the magnetic flux through P is given by

$$\phi_{\vec{B},P} = \int_{P} B \, dA \,, \quad B = \mu H$$

(2.4)

and the induced electromotive force

$$\oint_{\partial P} \vec{E} \ dl = -\frac{d\phi_{\vec{B},P}}{dt}.\tag{2.5}$$

By finding a conductive path, this electromotive force creates eddy currents in the test material.

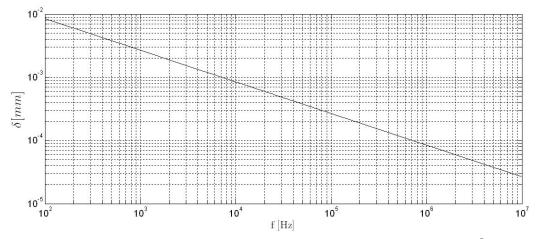

#### 2.2.2 Depth of penetration

The importance of the magnetic field frequency is that it determines eddy currents depth of penetration in the material. Electric current density decreases exponentially from the material surface with rate determined by frequency, electrical conductivity and magnetic permeability [8]. For a given frequency f the eddy currents density at depth f is

$$J_x = J_0 e^{-x(\pi f \mu_0 \mu_r \sigma)^{1/2}}$$

(2.6)

where  $J_0$  is the superficial current density,  $\mu_0$  the free space magnetic permeability expressed in H/m,  $\mu_r$  the material relative magnetic permeability and  $\sigma$  the material electrical conductivity expressed in S/m.

The standard depth of penetration is defined as the point where the electric current density has decreased by the factor of  $^1/_e \approx 36.8 \,\%$  [9] and can be determined by

$$\delta = \frac{1}{\sqrt{\pi f \mu_0 \mu_r \sigma}}.$$

(2.7)

By reducing the test frequency, it is possible to achieve higher penetration depths. However, this will also reduce the superficial current density. The chart on Figure 2.2 shows the different standard penetration depths as a function of frequency for aluminum.

**Figure 2.2** - Standard depth of penetration for aluminum ( $\mu_0 = 1.000022$  and  $\sigma = 3.54 \times 10^7$ ).

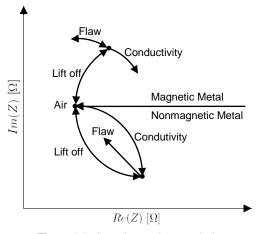

#### 2.2.3 Impedance plane

Eddy currents are mainly affected by electrical conductivity, magnetic permeability, geometry of the material, test frequency and the distance between coil and material (also known as lift-off). Furthermore, flaws and other material discontinuities modify the eddy currents so that the magnetic field disposition is altered.

Measuring the coil impedance provides information about eddy currents disposition and intensity on the material. Impedance planes allow an easy interpretation of inspection results based on comprehensive changes. Figure 2.3 shows an impedance plane and the effect of different sources perturbations.

Figure 2.3 - Impedance plane analysis.

When the coil is moved from air to a nonferromagnetic metal, the real component of the impedance will increase as the generation of eddy currents will take energy from the coil. This happens because the material is not a perfect conductor. Furthermore, eddy currents affect the magnetic field through the coil by reducing it and consequently the imaginary part of the impedance. If a flaw is present in the material, fewer eddy currents will be able to form increasing the imaginary part and decreasing the real part.

If the coil is placed on a ferromagnetic metal something different happens. Like with nonferromagnetics, because of the material resistivity, eddy currents will be wasting some energy from the coil, increasing the impedance real component. However the imaginary part increases as the field strength is augmented by the presence of such materials.

#### 2.2.4 Eddy currents probes

There are several types of eddy currents probes and each one is adjusted to a special evaluation purpose. Although there isn't a rigid probe classification, based on their operating mode is possible to define some usual arrangements:

- Absolute mode probes, devices containing a single coil that is used to generate eddy currents

and sense changes in the magnetic field. They can be used for defects detection, and for

conductivity and thickness measurements;

- Differential mode probes have two active coils usually wounded in opposition. When the two coils are over a defect-free material area, there is no signal developed between the coils since the common mode contribution is canceled. However, when only one coil is over a defect, the signal developed between the two coils increases. These probes are very sensitive to defects yet insensitive to unwanted variations. There are also disadvantages on using this type of probes, especially the difficult on the output signal interpretation;

- Reflection probes employ one coil for eddy currents dissemination and another to sense the

magnetic field among the material. This arrangement is often referred to as driver/pickup and

allows to independently optimizing each coil for their intended purpose. The driver coil can be

wounded to produce a strong and uniform flux field, while the pickup coil can be made very

small in order to increase their sensibility to small defects;

- A hybrid probe makes use of a coil to disseminate eddy currents but uses a different type of magnetic sensitive element to detect changes in the material. Hall Effect and Giant Magneto Resistance (GMR) sensors are the most commonly used.

Eddy currents probes can be made helicoidally or on a planar disposition. Planar probes provide a better contact with the material and can be flexible, allowing the inspection of complex geometry surfaces. Probe shielding can be added to reduce the interaction of the generated magnetic field with non relevant structures near the probe. Also, ferrite cores can be used as magnetic flux concentrators leading to more sensitive probes.

#### 2.2.5 Advantages of eddy currents evaluation

There are some advantages on using eddy currents for NDT purposes:

- Quick, simple, and reliable inspection technique to detect surface and near-surface defects;

- It can be used to perform several tasks like thickness measurements, corrosion valuation electrical and magnetic permeability measurements;

- There is no need for consumables and the inspection surface preparation is minimal;

- Results are drawn immediately. Equipment can be made very portable;

- It is well suited for inspecting complex part geometries;

- Personal skills and training are low, it is a very intuitive evaluation method;

- Can be easily automated and included in production lines.

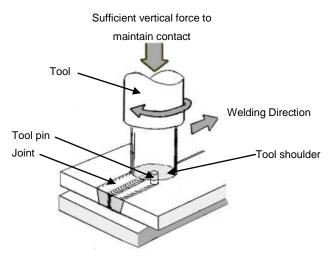

## 2.3 Friction Stir Welding: A challenge on NDT

FSW is a solid-state joining process patented by The Welding Institute UK in 1991 [10]. There is a huge potential on using this technology and it is considered the main advance on joining technology during the last decade [11]. FSW is performed without any filler material or gas protection and at lower temperatures than the fusion temperature of the involved materials, leading to a low level of joint distortion and residual tensions. In FSW, a non-consumable cylindrical tool is rotated at a constant speed through a joint line involving the work pieces to be joined which are overlapped or butted together, Figure 2.4. The pieces to be joined should be rigidly fixed to avoid their separation during the welding process.

Figure 2.4 - FSW process [12].

The tool pin length should be slightly less than the weld depth required and the tool shoulder should be in intimate contact with the work surface. Frictional heat is generated both internally by viscous dissipation and at the interfaces between the tool and the material of the work pieces. This heat causes the materials to soften without reaching the melting point, entering the plastic domain. As the tool is moved in the welding direction, its leading face forces plasticized material to flow back,

mainly around the retreating side, while applying a substantial force to consolidate the weld. FSW is based on severe plastic deformation in the solid state, involving the material crystal reconstruction.

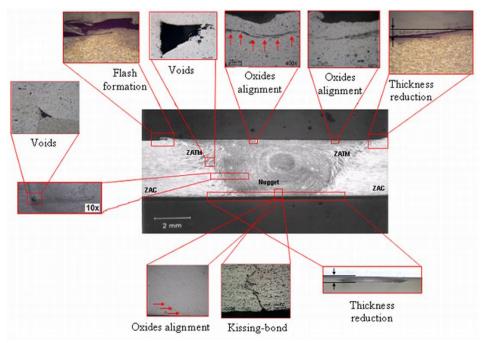

There are several welding parameters that influence the final weld quality, namely: vertical force, rotation speed, travel speed, tool geometry and tilt angle between the tool and welding materials. The right choice and application of the welding parameters will result in good welds. Nevertheless, under industrial production some defects may arise. Defects on FSW are very different from fusion weld typical defects and can have different origins, morphologies and sizes. Figure 2.5 shows the variety of defects that can be found on a FSW weld bead. In addition, there are conductivity changes that result from FSW process itself, even in a non-defective weld bead.

Figure 2.5 - Sectional view of a friction stir weld bead and their possible defects [13].

Friction stir welding can use purpose-designed equipment or modified existing machine tool technology. The process is also suitable for automation and adaptable for robot use. Other advantages are:

- Low mechanical distortion and excellent mechanical properties as proven by fatigue, tensile and bend tests;

- Energy efficient;

- Almost non-consumable tool;

- No grinding, brushing or pickling and excellent reproducibility make FSW suitable for mass production industry.

FSW has been applied in a broad range of applications like shipbuilding, aerospace, railway and others. However, FSW consolidation and application requires NDT procedures which the current development state does not allow to detect defects with influence over the structural performance of the weld beads [14].

#### 2.4 State-of-the-art

The main field of investigation on eddy currents evaluation relies on the development of new probes. Nevertheless, there are many works on the study of the electromagnetic phenomenon behind eddy currents and on the optimization of conventional probes.

In [15], the application of a FEM analysis with mesh refinement and error estimation to a conventional eddy currents probe is reported. Different error estimation criteria were defined and used to define the mesh refinement zone. Results include a convergence study for each criteria and the coil impedance calculation. In [16] the use of FEM to study the influence of several probe structural parameters over their linearity and sensibility is reported. An interesting work on the modeling of conventional eddy currents probes is shown in [17] where a genetic algorithm together with FEM are used to optimize the coil shape.

The electromagnetic induction in a coil is caused by changes on the magnetic field, thus, coils have less sensitivity at low frequency. The inspection of deep flaws is improved at low frequencies, creating the need for magnetic field sensors with frequency independent sensitivity. Hybrid probes with different magnetic field sensors are being developed. The use of Superconducting Quantum Interference Devices (SQUID) for analyzing eddy currents induced on the material is reported in [18]. In [19], an Hall Effect sensor together with a flat coil for eddy currents generation were used. In [20], the use of GMR sensors detecting flaws at 1.6 mm deep is reported. The employment of Giant Magneto Impedance (GMI) sensors for eddy currents testing is described in [21].

Due to the advantages on manufacturing and operating, planar probes are seen as promising for NDT. Meandering Winding Magnetometer (MWM) patented technology [22] is based on a driver/pickup arrangement where the driver element generates a magnetic field over a mesh of pickup coils. The entire probe is manufactured on a flexible substrate. Results on using this technology are presented in [23] and [24]. In [25], coils etched on thin Kapton film were used to inspect complex geometry surfaces. A comparison study between planar probes and the presentation of the first IOnic probe version are available in [26].

Pulsed eddy currents analysis is based on a different mode for stimulus generation. With this technique, a broadband pulse is applied as excitation and the transient response is analyzed. There is a big effort on this theme and new probes are been designed to improve this concept [27][28][29].

DSP techniques are being applied to extract the magnetic field information from raw voltage data. A good study on this theme is [30] where a DSP algorithm was used to improve the overall NDT system performance.

The use of personal computers in eddy currents evaluation supports complex analysis algorithms and provides powerful visualization modes. In [31] a commercial system based on a laptop computer is described and tested. Other researchers are using neural network analysis and pattern recognition to flaw reconstruction and classification [32][33].

## 2.5 Summary

In this chapter an overview about eddy currents NDT was discussed. Some basic concepts were introduced and the electromagnetic phenomenon behind eddy currents was described. Different types of probes were analyzed and some considerations on interpreting their behavior were registered. The state-of-the-art of eddy currents evaluation was presented in order to better understand the scope of this work. FSW joining process was described underlining the advantages resulting from its applicability and the increased difficulties regarding NDT techniques applied to FSW.

# Chapter 3 - IOnic Probe

#### 3.1 Introduction

IOnic is an emerging concept of eddy currents probe. This technology was patented in 2008 by a researchers group of IST [5] and their name is inspired on the likeness between the probe appearance and a Greek Ionic order column. This concept introduces a new approach to induce and sense the eddy currents in the material.

Along this chapter the morphology and operation theory of the IOnic probe will be discussed. The electromagnetic phenomena related with the probe operation theory will be described and analyzed making use of electromagnetism classic examples and FEM. After this initial content, some advantages of the IOnic concept when compared with conventional eddy currents probes will be presented. The design of a preliminary NDT system used in the probe experimental validation and its appliance to FSW it is reported. Finally, concept variations planned to overcome some of the probe limitations are presented at the end of the chapter.

## 3.2 Probe morphology and operation theory

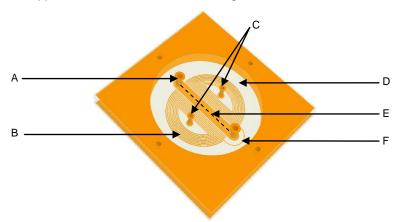

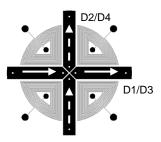

IOnic probe morphology exhibits a driver/pickup arrangement and at the same time, a differential based operation. The driver element is a copper trace placed in the middle of two pickup planar coils wired on opposite directions as shown in Figure 3.1.

Figure 3.1 - IOnic probe tri-dimensional view. A) Driver trace, B) Pickup coil

C) Pickup coils output terminals, D) Substrate, E) Symmetry axis, F) Pickup coils common terminal.

When an alternate current is made to flow in the driver trace, the lines of the generated magnetic field are orthogonal and concentric around it. This magnetic field induces eddy currents on the material and at same time is sensed on the pickup coils as electromotive force. By being symmetrical and sharing a common terminal, the pickup coils form a differential magnetic field sensor. In the presence of any perturbation that could modify the symmetry of the magnetic field among the axis on Figure 3.1, a signal is created between the pickup coils output terminals.

#### 3.2.1 Electromagnetic Phenomena

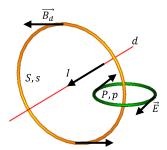

A good approach to understand how the magnetic stimuli are created and their response is sensed is to study an infinite, straight and current carrying wire. Figure 3.2 represent the infinite length wire d in where an electric current I is flowing. In a cross section like S, the magnetic field  $\overrightarrow{B_d}$  is tangent and uniform along their boundary circle S.

Figure 3.2 - Electromagnetic relations on an infinite, straight and current carrying wire.

Assuming a quasi-stationary condition, the magnetic field intensity for the successive s radius, r, is given by

$$B_d = \frac{\mu I}{2\pi r} \tag{3.1}$$

where  $\mu$  is the magnetic permeability of the medium around the wire. Considering the surface P orthogonal to the circle s and dA their area element, the magnetic flux through P is defined as

$$\phi_{\overrightarrow{B_d},P} = \int_P B_d \ dA \ . \tag{3.2}$$

If the boundary circle p is a one loop coil, the electric field is tangent and has the same magnitude on any point of the coil. Then, the electromotive force sensed by p is

$$\varepsilon = \oint_{p} \vec{E} \ d\vec{l} = -\frac{d\phi_{\overrightarrow{B_d},P}}{dt}.$$

(3.3)

If this wire is near to a metallic material, eddy currents appear as a reaction to oppose the magnetic field. Furthermore, these eddy currents modify the magnetic field disposition and intensity from the original  $\overrightarrow{B_d}$  to

$$\vec{B} = \vec{B_d} + \vec{B_e} \tag{3.4}$$

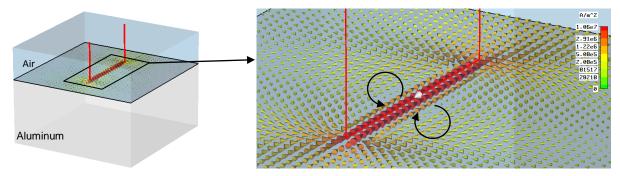

where  $B_e$  refers to the magnetic field generated by the eddy currents. The interaction between eddy currents and defects shows up as the magnetic field perturbation  $\overrightarrow{B_e}$  and can be sensed by a coil as seen before. Figure 3.3 shows the infinite length wire 100  $\mu$ m away from a piece of aluminum being driven by a sine wave I with 1 A amplitude and frequency of 500 kHz. These plots are drawn when the current I is at its maximum amplitude. As can be seen, the magnetic field around the wire is changed by the presence of the eddy currents which take the inverse direction of the electrical current on the wire.

Figure 3.3 - Current carrying wire over an aluminum piece. A - Magnetic field, B - Eddy currents.

#### 3.2.2 Finite Element Modeling

Two models were created using the finite element analysis software CST EM Studio. These models provided baseline information about the magnitude of the generated signals and the expected behavior in the presence of defects. From Figure 3.14 to Figure 3.7, a sine wave with 1 A amplitude and frequency of 500 kHz is flowing in the driver trace. Also, these plots are drawn when the stimulus current is at its maximum amplitude.

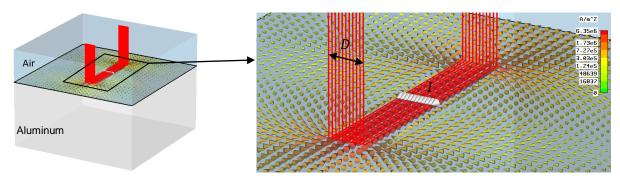

Unlike the previous wire, the driver trace has a finite length and is limited by two vertical segments. On those conditions, current flowing on the vertical segments will also generate magnetic field. Although, as the main component of the magnetic field generated by the vertical segments lays on the horizontal plane, few eddy currents will be induced due to this modification. However, limiting the wire length causes quite interesting changes over the induced eddy currents. They will describe loops passing underneath the driver trace and circular paths defined through the material, Figure 3.4.

Figure 3.4 - Eddy currents induced by a limited length current carrying wire.

To model the IOnic probe driver trace, there will be multiple current paths established trough a single trace. This is modeled by adding parallel wires carrying together the same current than the initial one. The initial trace can now be considered the array of *D* wires represented in Figure 3.5. It is possible to observe how the eddy currents have changed to occupy all the area underneath the wire array.

Figure 3.5 - Eddy currents induced with the wire array.

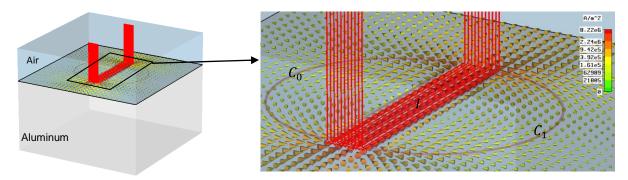

The subsequent and final step to complete the first probe model is to define the pickup coils. One of the available elements on the software package is an ideal coil defined by their path and loops number. Two D shaped ideal coils were created over the area where eddy currents flow, Figure 3.6. Both coils are constituted by P closed loops and were named  $C_0$  and  $C_1$ .

Figure 3.6 - Basic probe model and superficial eddy currents.

The electromotive force sensed on the coils can be modeled as

$$\varepsilon_{C_n} = P \sum_{i=0}^{D} -\frac{d\phi_{\overrightarrow{BD_i}, P_n}}{dt}$$

(3.5)

were  $P_n$  is the transversal area defined by the coil.

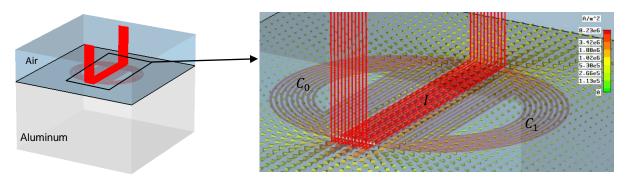

The second model was introduced to evaluate how the performance of the probe is changed by using spiral coils. The initial pickup coils were replaced by a more realistic coil model, Figure 3.7.

Figure 3.7 - Advanced probe model and superficial eddy currents.

By doing this, the area defined by each loop is approximated to that on the real probe. On those circumstances, the electromotive force on each coil is

$$\varepsilon_{C_n} = \sum_{i=0}^{D} \sum_{j=0}^{P} -\frac{d\phi_{\overline{BD_i}, P_j}}{dt}$$

(3.6)

where  $P_i$  is the transversal area defined by each loop.

Because of the common terminal and the fact that they are wired in opposite directions, considering the differential operation, the electromotive force induced between the two output terminals is, for both models,

$$U_{out} = \pm \varepsilon_{C_0} \mp \varepsilon_{C_1}. \tag{3.7}$$

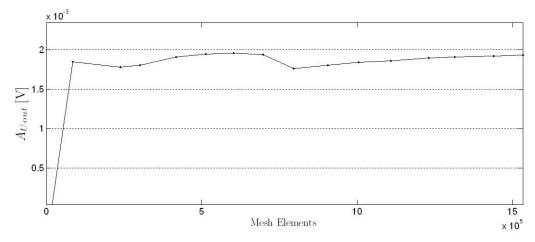

After modeling the probe, the structure was studied and a symmetry axis was defined. This symmetry axis was set perpendicular to the driver trace and equally on both models. In order to evaluate how many mesh elements were needed for a good analysis, a convergence study was then necessary. This convergence study was performed with the advanced model since it has a more complex structure than the basic one. On Figure 3.8 is represented the amplitude of the induced voltage on the coil  $C_0$ , when the driver trace current amplitude is 1 A, for an increasing number of mesh elements.

Figure 3.8 - FEM Convergence analysis.

It is observed that for a mesh with more than one million elements, the amplitude on the coil remains almost unchanged. On FEM, the calculation time is highly dependent on the number of mesh

elements. Thus, a mesh with 1.22 millions of elements was chosen as it provides a good approximation and yet a tolerable computation time. At this point, a defect with 10 mm depth and 300  $\mu$ m width was defined on the aluminum piece. Then, a positional sweep is performed with 500  $\mu$ m steps in the conditions shown on Figure 3.9.

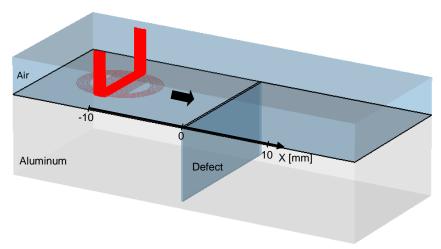

Figure 3.9 - Defect characterization sweep.

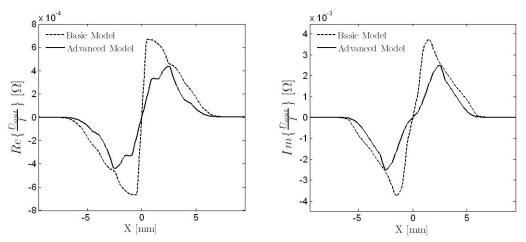

During the sweep, the successive values for the ratio  $\overline{U}_{out}/\overline{I}$  were registered. The results for both models are presented in Figure 3.10. As expected, when the probe is away from the defect, the induced voltage is roughly zero. Although, since the sensitive coils overlap the defect, the signal output increases returning to zero when the defect is perfectly centered with the probe. This behavior is observed on both real and imaginary part. However, the defect contribution is mainly observed on the imaginary part of  $\overline{U}_{out}/\overline{I}$  as the pickup coils voltage results from the electromagnetic induction. Due to the pickup coils differences, the basic probe model is much more sensitive than the advanced one where the maximum excepted output amplitude for defects like this and similar driver trace current is about 2.4 mV. The advanced model will be experimentally validated on the next pages.

**Figure 3.10** - Real and imaginary part of the ratio  $\overline{U}_{out}/\overline{I}$  along the sweep.

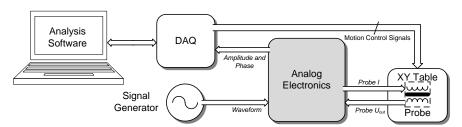

## 3.3 Preliminary NDT system

To perform the experimental validation of the probe concept, a preliminary version of the NDT system was developed in collaboration with the IST Solid-State Welding Group. The system provided a test bench to quickly bring the probe into operation and is composed by the following components:

- XY table to move the probe along the test material;

- Signal generator;

- IOnic eddy currents probe prototype;

- Analog electronics;

- National Instruments USB-6251 DAQ for data acquisition and to control the XY table;

- Analysis software developed on LabVIEW to process, and save the acquired signals.

The system architecture is shown in Figure 3.11. From all the represented components, this dissertation contributes mainly on the analog electronics whose architecture, design and prototyping will be discussed.

Figure 3.11 - Preliminary NDT system overview.

The analog electronics block is responsible for the generation of the driver trace current, and for recovering the amplitude and phase information of the probe output signal. In this first approach, this is achieved using general purpose analog integrated circuits which generate DC signals proportional to the probe output signal amplitude and the phase difference between this signal and the driver trace current. These DC signals are then acquired by the DAQ and received by a personal computer were the processing is done in a LabVIEW application. This application is also responsible for the probe positioning by controlling the stepper motors on the XY Table.

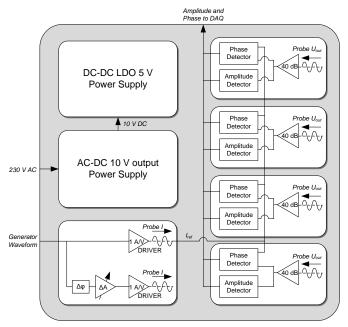

The functional diagram of the developed analog electronics system can be seen in Figure 3.12. Two driver circuits were included with the possibility to set the relative amplitude and phase difference between them. This feature was implemented to allow the operation of a concept variant based on the IOnic probe which will be described later. Four amplitude and phase detector were included allowing to simultaneous process the output signal from four pickup coils.

Probe driver circuits are powered by a 10 V AC-DC supply connected to 230 V AC power. The 5 V supply voltage needed for the amplitude and phase detectors is achieved with a Low Drop Out (LDO) linear regulator.

Figure 3.12 - Analog electronics system functional diagram.

#### 3.3.1 Probe driver

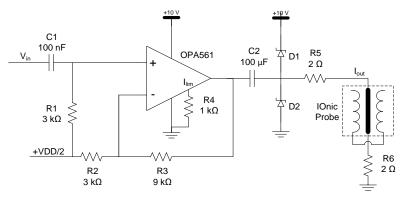

To generate an alternating current on the probe driver trace a current buffer was implemented. An OPA561 high current Operational Amplifier (OPAMP) wired in a non-inverting configuration with transconductance of 1 A/V as shown in Figure 3.13 was used. As there is no current feedback on the circuit, the load series impedance, constituted by the cabling and the probe driver trace should respect the relation

$$Z_l \ll R_5 + R_6. \tag{3.8}$$

In such conditions, the transconductance gain is given by

$$\frac{I_{out}}{V_{in}} = \left(1 + \frac{R_3}{R_2}\right) \frac{1}{R_5 + R_6} = 1 \text{ S}.$$

(3.9)

Figure 3.13 - Probe driver circuit.

In the circuit, R4 limits the output current to about 1.1 A and the output signal DC component is removed with C2. Schottky diodes D1 and D2 provide OPA561 output protection damping output voltages outside the power voltage range. When driving the probe with a 1 A amplitude sine wave, the

OPA561 dissipates about 3 W, for this reason, some precautions are necessary to avoid the damaging or performance degradation of the integrated circuit. OPA561 has a thermally enhanced package offering a very low thermal resistance path to the Printed Circuit Board (PCB) of 1.4 °C/W. The PCB region were this integrated circuit was soldered has been carefully designed to extract the heat generated directly to the system metallic enclosure box.

The manufactured circuit was able to drive the probes with a sine wave with 1 A amplitude along a frequency range from 10 kHz to 1 MHz.

#### 3.3.2 Amplitude and phase difference detector

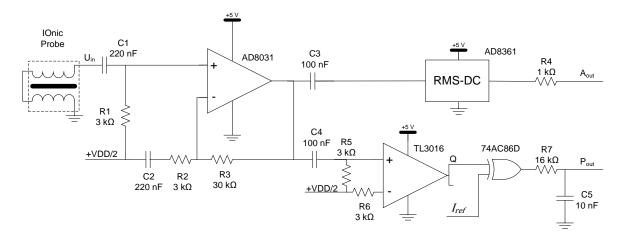

As seen in the FEM study, even when inspecting an extreme defect, IOnic probe output signal amplitude has no more than 3 mV. Because of that, the very first stage on this circuit is a 40 dB gain voltage amplifier made by a high speed AD8031 OPAMP wired on a non-inverting configuration, Figure 3.14.

Other devices are responsible for generating DC signals proportional to the amplitude of the probe  $\overline{U}_{out}$  signal and the phase difference between this signal and the current  $\overline{I}$ . The amplitude detection is realized using an AD8361 RMS-DC converter and the phase difference is computed with a XOR type phase detector. All the circuits are powered by the 5 V power supply and a voltage divider with appropriate filtering capacitors provide the mid-supply reference.

Figure 3.14 - Amplitude and phase difference detectors circuits.

The amplitude output is related with  $\overline{U}_{in}$  amplitude by

$$A_{out} \approx 7.5 \frac{100 \times A(\overline{U}_{in})}{\sqrt{2}}$$

(3.10)

Phase difference is computed by digitalizing both the signals with a comparator, execute the XOR binary operation and then extract the mean value. A TL3016 fast comparator and a 74AC86D XOR function array ensure digital conversion and processing. The low pass RC filter bandwidth was set to 1 kHz and its output is given by

$$P_{out} \approx \Delta \varphi(\overline{U}_{out}, \overline{I}_{ref}) \times 5$$

(3.11)

#### 3.3.3 Analog Electronic System Prototype

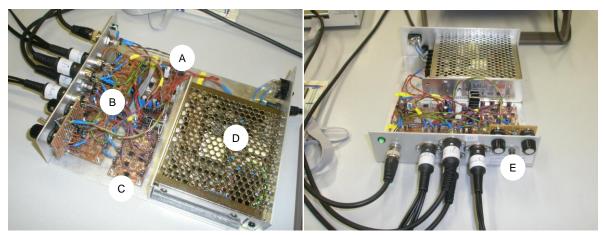

The system was manufactured and assembled in the IST Taguspark rapid prototyping facilities. Two layers PCBs were produced making use of a circuit board plotter and an electroplating processing system. After the PCB production stage, a soldering station was used to assembly the circuits which were placed together in the same metallic enclosure box shown in Figure 3.15. The development and prototyping activities needed to achieve a functional prototype took about four weeks.

Figure 3.15 - Analog electronics system prototype.

A - Probe drivers, B - Amplitude detectors, C - Phase difference detectors, D - Power supply, E -  $\Delta A$  and  $\Delta \phi$  controls.

## 3.4 IOnic probe concept validation

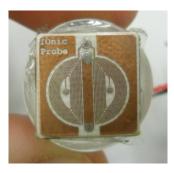

An IOnic probe was manufactured on 1.6 mm dual layer Flame Retardant 2 (FR2) PCB substrate with an external dimension of 12 mm. The two pickup coils are formed by 9 winding tracks of 100 µm width separated by same dimension gaps, Figure 3.16.

Figure 3.16 - Manufactured IOnic probe.

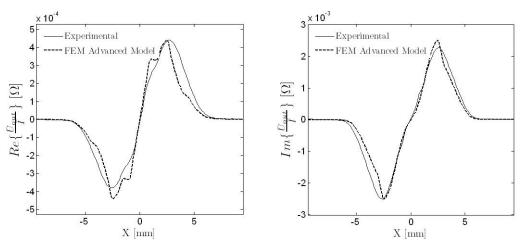

The defect used on the FEM was reproduced by electro-erosion on a piece of aluminum and an identical sweep was performed. Once again the driver trace current is a sine wave with 500 kHz frequency and 1 A amplitude. The plots for the experimental validation and the FEM are included in

Figure 3.17. Note that there is a very good similarity between the two results mainly on the imaginary part of  $\overline{U}_{out}/\overline{I}$  which is about one order of magnitude greater than the real part.

Figure 3.17 - Experimental and FEM results for the standard defect.

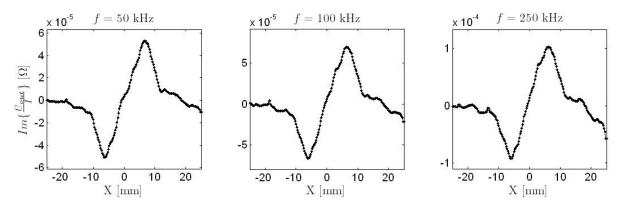

After the probe concept validation, a defect free FSW weld bead was inspected. This specimen was obtained by performing a FSW sweep in a plate of aluminum alloy AA2024-T531 of 3.8 mm thickness. By using a single piece of base material and selecting proper welding parameters it is possible to achieve almost perfect weld beads. In fact, bead on plate samples provide an excellent quality standard for FSW process. The bead on plate was inspected along a sweep on the perpendicular direction of the weld, with the driver trace parallel to it. The starting point of the test is set to 25 mm before the weld bead and 50 mm long segments are characterized with 250 µm space steps. In all the acquisitions, the real and imaginary part of  $\overline{U}_{out}/\overline{I}$  are measured at 50, 100 and 250 kHz. The imaginary part of  $\overline{U}_{out}/\overline{I}$  for the specified sweep is shown in Figure 3.18. As FSW process causes material conductivity changes, even without a defect, the weld bead is responsible for the large curve on the processed imaginary part.

Figure 3.18 - Results for the FSW bead on plate for 50, 100 and 250 kHz.

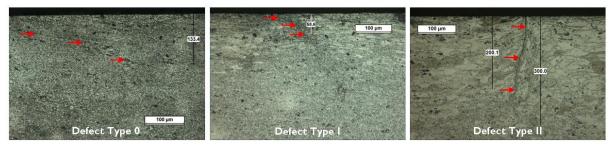

After characterizing a non-defective bead on plate, a set of friction stir welds have been realized on the same aluminum alloy. The welding parameters were chosen in order to produce three distinct types of defects as is shown in Figure 3.19.

**Figure 3.19 -** Transversal macrographs of three different FSW defective weld beads. Defect Type 0 - Oxides alignment, Defect Type I - ≈60 µm, Defect Type II - ≈200 µm.

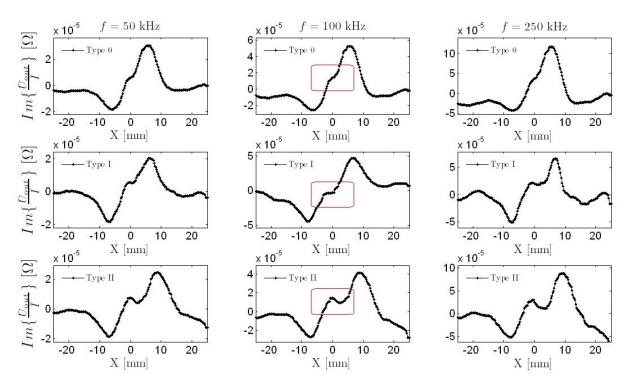

The three defects were inspected in same conditions as the bead on plate sample and for the same three frequencies. The imaginary part of  $\overline{U}_{out}/\overline{I}$  for the three types of defects and for the three selected frequencies is shown in Figure 3.20. The presence of defects creates a small perturbation observed in the middle of the sweep, highlighted in red on Figure 3.20. The different types of defects can be detected and there is a very good proportionality between the defect dimension and the observed perturbation on the imaginary part of  $\overline{U}_{out}/\overline{I}$ .

Figure 3.20 - Results for the FSW weld beads with defect types 0, I and II for 50, 100 and 250 kHz.

To compare the performance of the new probe with the conventional ones, the system was used also with a traditional planar probe. This second probe is composed by a flat spiral coil with 20 windings and 8 mm overall diameter. The results on inspecting the FSW joints when the coil current is a 1 A sine wave with frequencies 100, 250 and 750 kHz are shown in Figure 3.21. Unlike the results achieved with the IOnic probe, there is no characteristic that could be used to conclude about the

presence of defects. With this probe, the material conductivity changes inside the FSW weld bead mask the contribution of the defects making impractical the defect detection.

Figure 3.21 - Results for the FSW weld beads with a conventional planar probe.

### 3.5 IOnic concept advantages

The IOnic probe has some advantages when compared to the conventional eddy currents probes:

- Differential based operation resulting on high sensibility and superior lift-off immunity. The

probe is almost completely immune to lift-off if the probe remains perfectly parallel with the

material;

- Improved contact with test material. The planar design allows the probe to be in close contact with the material (100-300 μm) enhancing the sensibility for very small defects;

- Deeper eddy currents penetration due to the small distance between the driver trace and the test material;

- The intense eddy currents induced in the material near the driver trace can be taken as advantage to evaluate materials where the flaws tend to follow a specific orientation. Making use of the probe on such conditions may substantially increase those defects detection probability;

- Allow the inspection of the material borders as long as the symmetry axis remains

perpendicular to it. It can be also used on non-planar and complex geometry surfaces since the

probe can be manufactured on flexible substrates;

Despite the preferred operation mode is differential, the probe can also perform absolute measurements by making accessible the common terminal of the pickup coils. This will provide information on material parameters such as conductivity, magnetic permeability and thickness.

## 3.6 IOnic concept variations

Three concept variations of the IOnic probe have been studied in order to overcome some of the probe limitations or to improve their performance on some inspection applications.

#### 3.6.1 IOnic Plus

With the original probe, it is very hard to detect defects that appear transversally to the driver trace. In such conditions the defects interact with the originated eddy currents but the magnetic field symmetry along the axis defined by the driver trace remains unchanged. This concept variant was designed to overcome this limitation of the original probe. By modifying of the original morphology, new features and operation modes have been found.

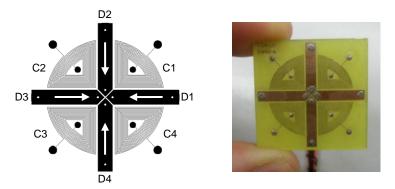

The IOnic Plus probe exhibit four driver traces outlining a cross and four pickup coils, one in each quadrant of the driver traces cross, Figure 3.22. As before, the magnetic field is sensed in the pickup coils which can be read independently or in multiple combinations. This morphology enables multiple operation modes according to the currents flowing in the driver traces and the configuration selected for the pickup coils wiring.

Figure 3.22 - IOnic Plus morphology and prototype.

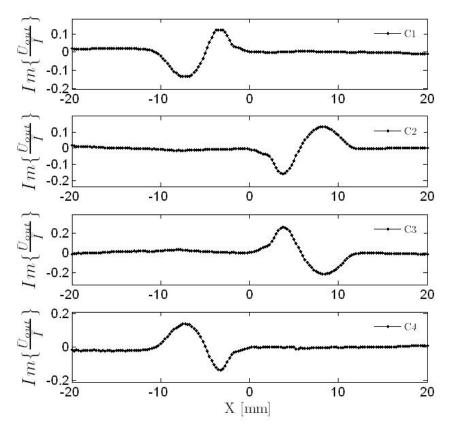

In order to validate the probe operation, it was used together with the preliminary NDT system to inspect the standard defect described in Figure 3.9. The probe is positioned so that two of the driver traces are parallel to the defect. The same 1 A amplitude, 500 kHz frequency sine wave is made to flow in the driver traces according with the arrows in Figure 3.22. The results for the output signals from the four pickup coils are shown in Figure 3.23.

Figure 3.23 - IOnic Plus standard defect inspection results.

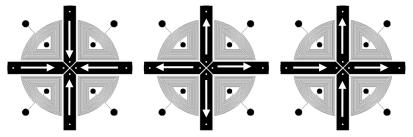

Unlike the IOnic probe where the two pickup coils are wired together, the signals on each pickup coil were independently processed. The presence of the defect can be observed in all the pickup coils output signal even if the probe is rotated by 90°. The results illustrate the static operation of the probe that can be achieved by using the same current on the driver traces. Even in the static operation mode, the driver traces can be wired in several configurations as shown in Figure 3.24 leading to multiple patterns of induced eddy currents.

Figure 3.24 - IOnic Plus static operation mode configurations.

In addiction to this basic operation mode, there is the possibility to introduce variations between the currents flowing in the driver traces. This dynamic operation mode enables to control the induced eddy currents profile by commanding the relative amplitude and phase difference between the currents in the driver traces. To operate the probe, are required two independent current generators for the D1/D3 and the D2/D4 driver traces sets, Figure 3.25. The control of the eddy currents can then be made electronically while inspecting the material.

Figure 3.25 - IOnic Plus driver trace connections for the dynamic operation mode.

The use of this new variant allows an improved defect characterization and accurate localization by introducing some advantages:

- Versatility of the probe operation, allowing creating an output signal from each pickup coil or from their combination;

- The defects localization and morphology can be reconstructed by using the correlation between the four pickup coils output signals;

- The electronic control of eddy currents disposition inside the test material, allows the detection of defects whose morphology follow any direction;

- The multiple response patterns from the several combination of driver traces currents and pickup coils arrangements originate a huge amount of data on each point of the material to inspect;

- Less complex motion and positioning systems and increased inspection speed by removing the need of rotate the probe.

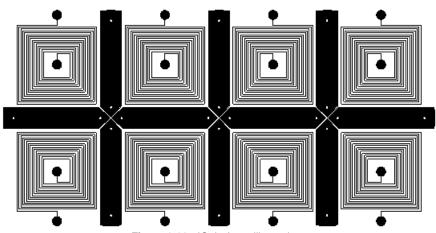

#### 3.6.2 IOnic Matrix

This concept variation is based on the matrix repetition of IOnic plus arrangements. This repetition can be made on the two directions of the substrate plane and with a reconfigurable pattern according to the inspection purposes, Figure 3.26. To maximize the sensitive area of the pickup coils, their shape is square. The main advantage resulting from this repetition is the expanded inspection area of the probe and consequently the increase of the inspection speed.

Figure 3.26 - IOnic Array illustration.

#### 3.6.3 IOnic Active

The IOnic probe can be made even more sensitive to small defects by reducing the sensitive area of the probe. However, the number of windings of the pickup coils is limited by the manufacturing capabilities leading to very low amplitude output signals. This concept variation allows overcoming electromagnetic compatibility issues that can arise from the signal transmission between the probe and the acquisition system.

In order to amplify the output signal of the probe, a differential amplifier was used and assembled on the top side of the probe substrate. The differential amplifier used was the AD8351 low noise amplifier set to 20 dB voltage gain. In this conditions, the excepted noise spectral density introduced by the AD8351 is about  $2.7~\mathrm{nV/\sqrt{Hz}}$ . Besides the good characteristics regarding noise and linearity, this device has been selected because of the single power supply operation and low power dissipation. To set the probe output common mode voltage, the common terminal of the pickup coils is wired to the GND reference of the amplifier.

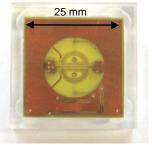

The probe is printed in the bottom layer of the substrate and the circuit is assembled on the top layer. In Figure 3.27 the bottom view of the manufactured IOnic Active probe inside a Plexiglas enclosure is shown. The six coil windings of the pickup coils have about 90  $\mu$ m and are separated by the same distance.

Figure 3.27 - IOnic Active bottom view.

## 3.7 Summary

In this chapter, the new IOnic concept for eddy currents probe has been presented. The electromagnetic phenomena related with the probe operation have been discussed using classic examples of electromagnetism literature. FEM analysis has been used to clarify and corroborate the new concept of eddy currents probe. The experimental validation and application results to FSW specimens presented demonstrate the effectiveness of the probe on the defect detection. In the end of the chapter some advantages of the new approach and concept variations have been introduced.

The potential of the new probe was highlighted by the encouraging results obtained while inspecting FSW joints. However, this preliminary system has some limitations as the narrow frequency operation range and the impossibility to explore new types of stimulus. These reasons lead to the development of a new and improved version of the non-destructive testing system.

# Chapter 4 – ECscan NDT System Hardware

### 4.1 Introduction

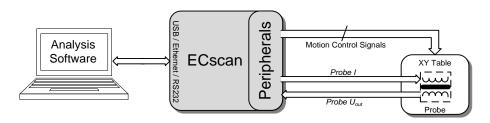

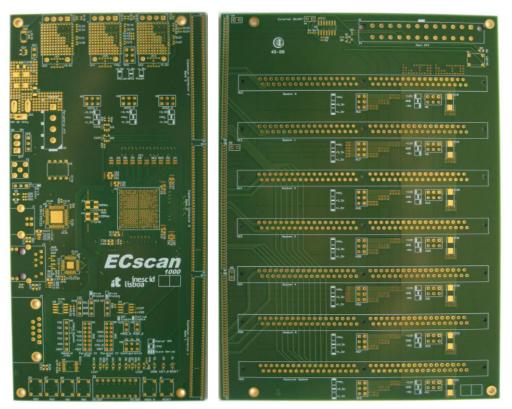

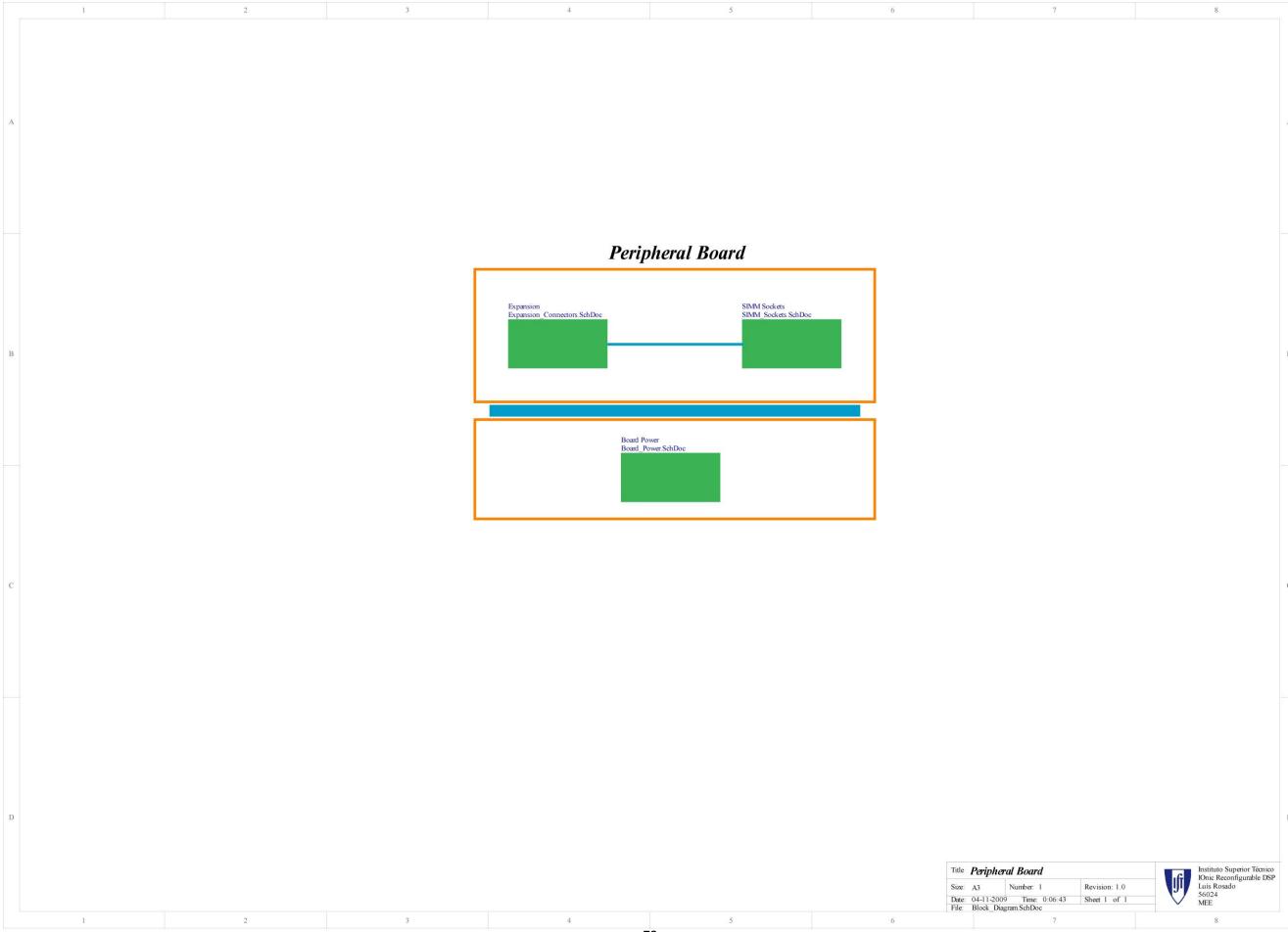

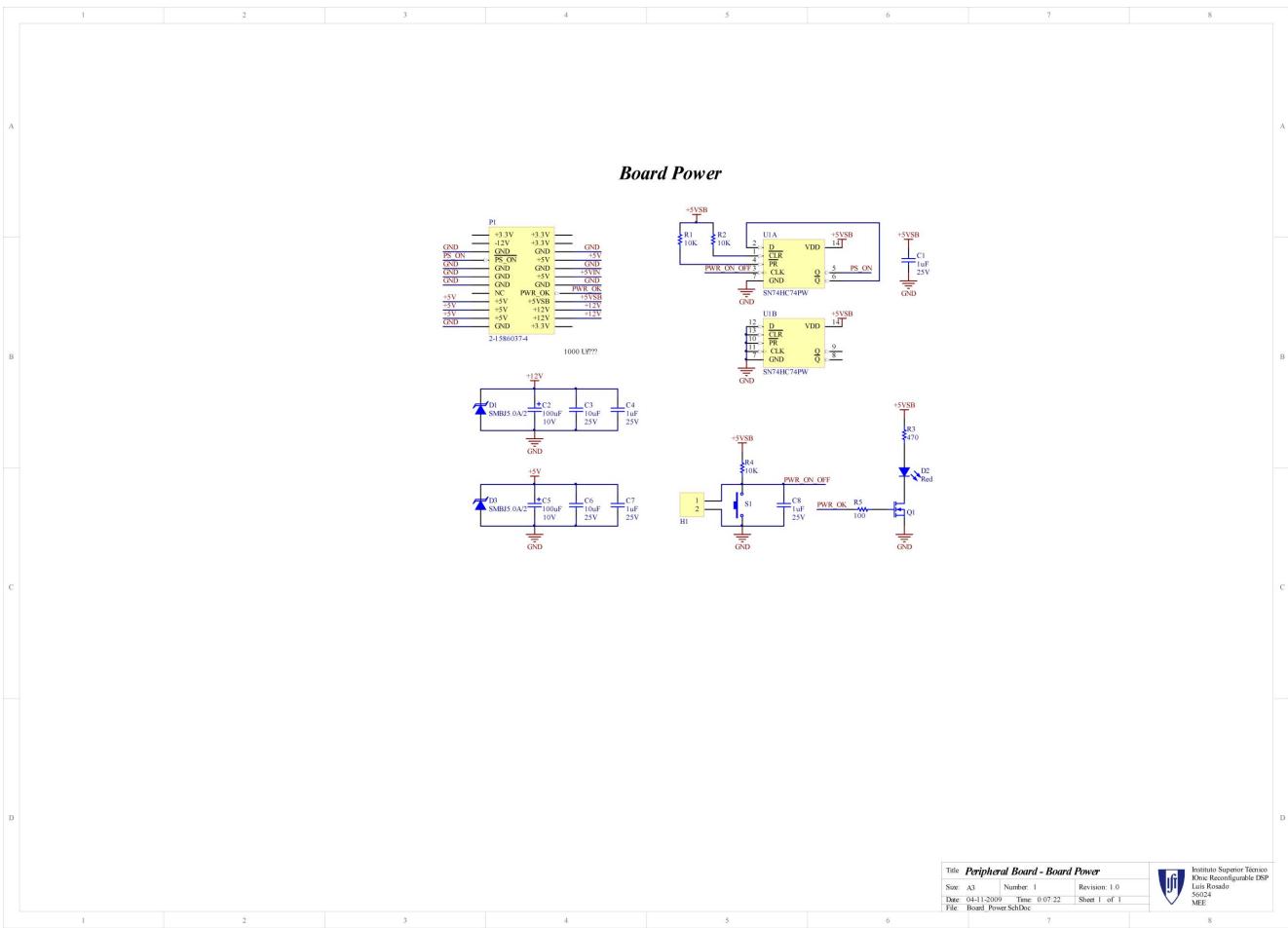

To extract the maximum advantage from the new probes, a tailor made electronic system to perform non-destructive testing tasks was developed. This second approach was designed to fully replace the electronic devices employed in the preliminary version by a single and integrated solution, Figure 4.1. ECscan is a reconfigurable solution for eddy currents NDT composed by hardware for high speed signal generation and processing, and dedicated software. The new system takes advantage from the flexibility, repeatability and reliability achieved through the probe signals digital signal processing. ECscan is highly reconfigurable through the use of programmable digital logic devices and the possibility to set several combinations of peripherals cards for signal generation or acquisition. Also, several communication interfaces have been added providing easy connectivity with personal computers and networks.

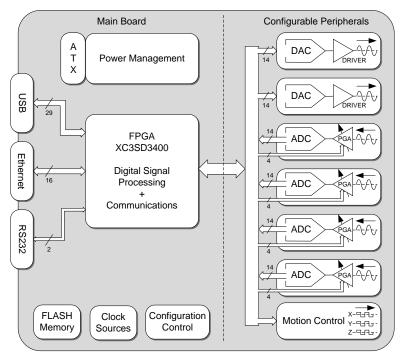

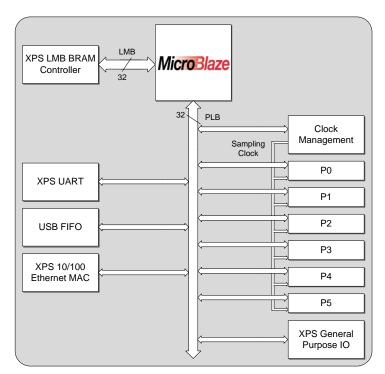

Figure 4.1 - ECscan system Overview.

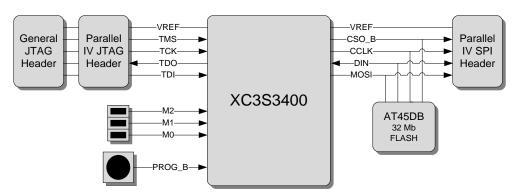

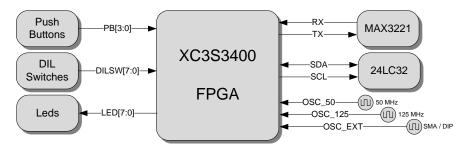

Regarding hardware, ECscan is an embedded system based on a FPGA device tailored for digital signal processing and memory intensive applications. The main board includes the processing and power management devices, and communication interfaces for Universal Serial Bus (USB) 2.0 High Speed, Ethernet 10/100 and RS232, Figure 4.2. In addition, the main board has non-volatile FLASH memory, used to store software and internal settings, several clock sources and configuration interfaces.

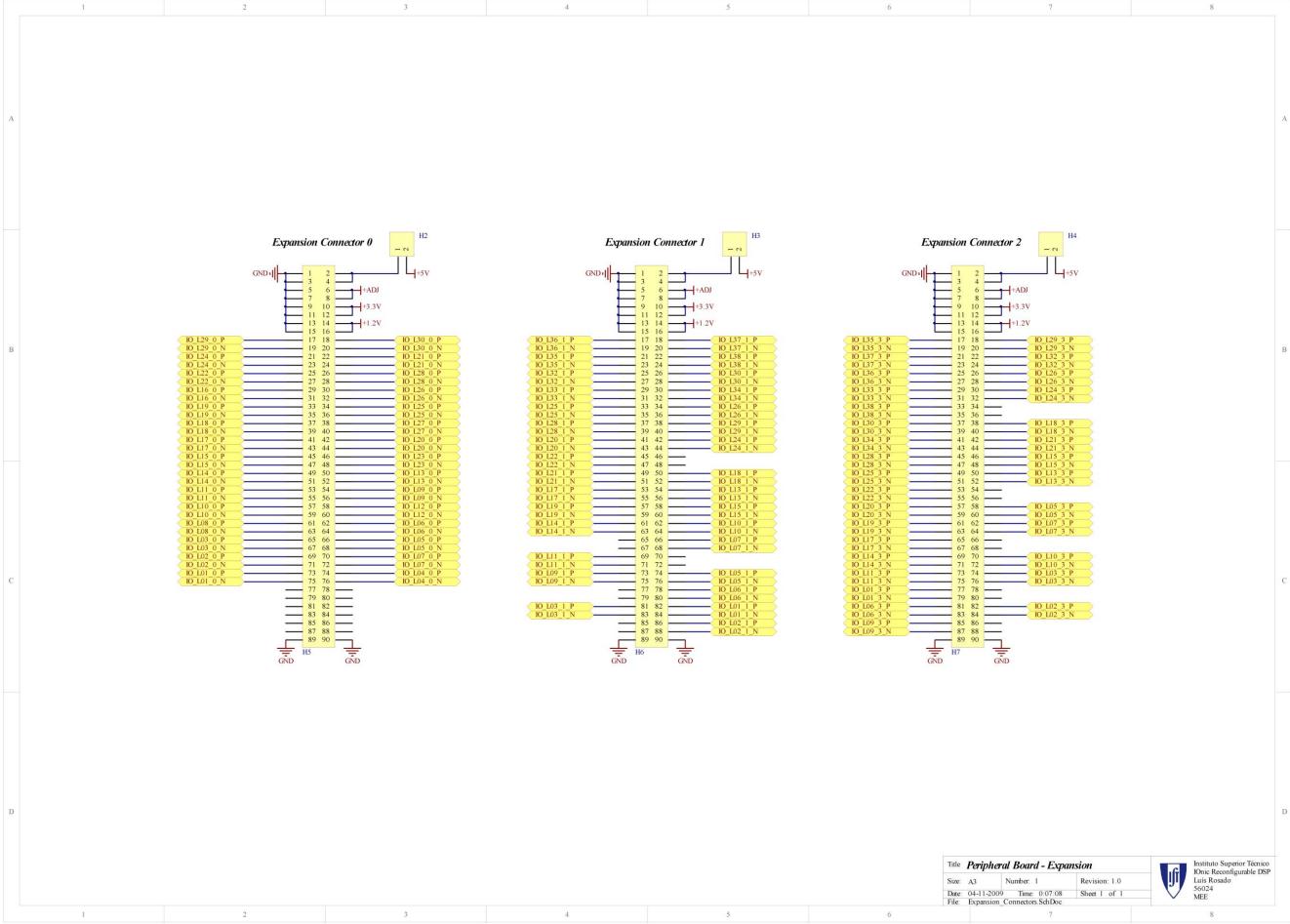

In this innovative system, digital stimulus are generated in the FPGA processing core and then converted to an analog signal that is used to drive the probe. Conversely, the probe output signals are acquired and then processed in the digital domain. Unlike the preliminary NDT system, this new approach enables the generation of numerous stimulus types and the probe output signals processing through a great variety of algorithms. Furthermore, the seven connectors available in the main board can be used to set multiple configurations of peripherals cards to generate or to acquire the signals on the several IOnic probes and concept variants. With this number of connectors and the three types of peripherals cards developed, it is possible to implement a proper combination to operate the IOnic

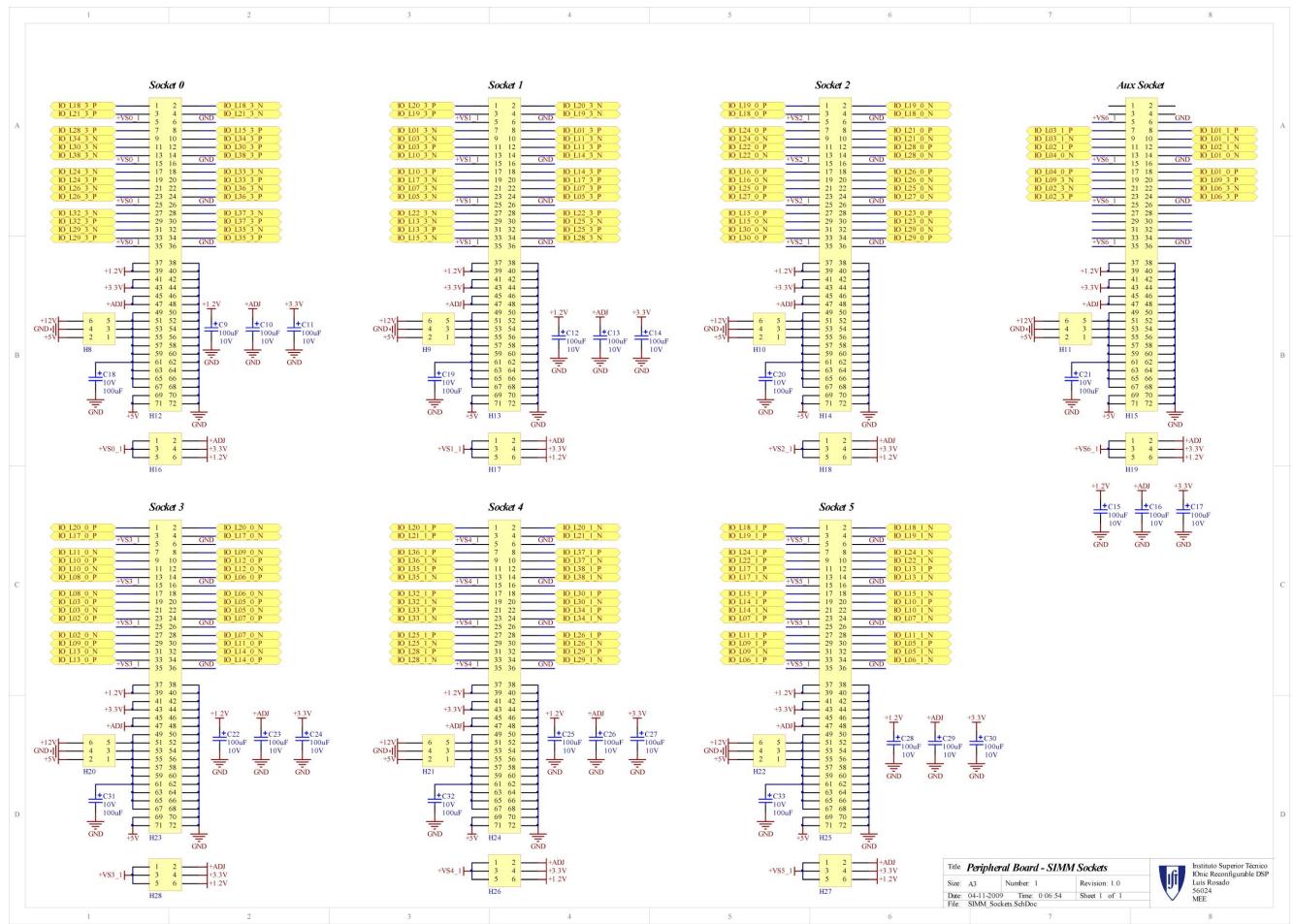

Plus probe as can be seen in Figure 4.2. In order to easily exchange the peripherals, they are connected to the main board through Single In-Line Memory Module (SIMM) 72 vertical sockets.

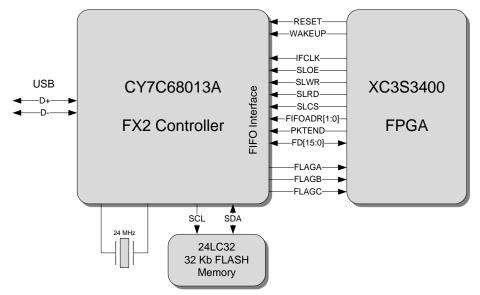

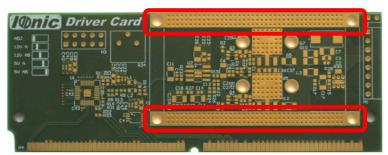

The peripheral card responsible for the probe input current generation is composed by a 14 bits Digital to Analog Converter (DAC) followed by an improved probe driver circuit featuring higher output current and an extended frequency operation range. Signal acquisition is achieved with 14 bits high speed Analog to Digital Converters (ADC) connected to Programmable Gain Amplifiers (PGA) where the input signal amplification is controlled by a four bits gain digital code. The frontend of the acquisition operates in the differential mode allowing extracting the maximum advantage from the IOnic Active probe. An additional peripheral was designed to simultaneous control up to three axis on the XY Table.

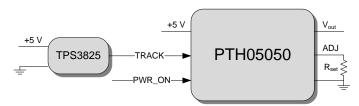

Figure 4.2 - Main board functional diagram.

Along this chapter, the design of each ECscan hardware block will be described. The hardware was developed using Altium Protel 2009, Computer Aided Design (CAD) software and the produced schematics are included in the Appendix I.

#### 4.2 ECscan Main Board

The main board of ECscan system contains the processing device, power management devices, the communication interfaces and connectors for peripherals. This board aims to provide features that are needed for almost all possible system application. It was specially designed to provide sufficient resources for the seven peripherals that can be connected.

Despite the fact that this board has been designed to be included in the ECscan system, it can be used for prototyping, evaluation and educational purposes. In fact, the board resources can be employed to develop a different system avoiding the complex and time consumer design of a FPGA processing core. Also, it can be used to implement didactical projects on digital signal processing and embedded systems.

The characteristics of the ECscan Main board are:

- XILINX XC3SD3400A FPGA processing core;

- High Speed USB 2.0 interface;

- Ethernet 10/100 interface;

- RS232 Interface;

- 2 on-board clock sources;