## Wearable IoT System for Monitoring People

## Maria Inês Costa Frutuoso

Thesis to obtain the Master of Science Degree in

## **Electrical and Computer Engineering**

Supervisors: Prof. Rui António Policarpo Duarte Prof. Horácio Cláudio De Campos Neto

#### **Examination Committee**

Chairperson: Prof. Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Prof. Rui António Policarpo Duarte Member of the Committee: Prof. António Manuel Raminhos Cordeiro Grilo

September 2021

ii

## Declaration

I declare that this document is an original work of my own authorship and that it fulfils all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

## Acknowledgments

I would like to thank my supervisors Prof. Horácio Neto and Prof. Rui Duarte for their enthusiastic guidance over the last months. I am grateful for having the opportunity to learn with their expertise and insightful contributions.

I want to thank all who I have met throughout my academic adventure and with whom I have grown both personally and professionally.

I am thankful for the unconditional support of my loved ones, family and friends, along my journey.

#### Abstract

Wearable devices used for personal monitoring applications have been improved over the last decades. However, these devices are limited in terms of size, processing capability and power consumption. This thesis proposes an efficient hardware/software embedded system for monitoring bio-signals in realtime, including a heart rate calculator using Photoplethysmography (PPG) and an emotion classifier from Electroencephalography (EEG). The system is suitable for outpatient clinic applications requiring data transfers to external medical staff. The proposed solution contributes with an effective alternative to the traditional approach of processing bio-signals offline, by proposing a SoC-FPGA based system that is able to fully process the signals locally, at the node. Two sub-systems were developed targeting a Zyng 7010 device and integrating custom hardware IP cores that accelerate the processing of the most complex tasks. The PPG sub-system implements an autocorrelation peak detection algorithm to calculate heart rate values. The EEG sub-system consists of a KNN emotion classifier of preprocessed EEG features. The hardware/software solutions were compared to the software-only implementations executing in the Zynq's ARM processor, having obtained a speedup up to 40 times. The system consumes only 36% of the Zynq's resources and thus new functionalities may be added. The proposed system constitutes the foundation of more complex biometric systems, that may benefit from the combination of different reusable IP cores. This work overcomes the limitations of microcontrollers and generalpurpose units, presenting a scalable and autonomous wearable solution with high processing capability and real-time response.

**Keywords:** Electroencephalography, Hardware/software co-design, Photoplethysmography, SoC FPGA, Wearable monitoring devices

#### Resumo

Os dispositivos wearable utilizados para monitorização da pessoa têm sido melhorados nas últimas décadas. Contudo, estes dispositivos estão limitados pelas dimensões, a capacidade de processamento e o consumo energético. Esta tese propõe um sistema hardware/software para a monitorização de bio-sinais em tempo-real, compreendendo uma calculadora de ritmo cardíaco utilizando a Fotopletismografia (PPG) e um classificador de emoções a partir da Electroencefalografia (EEG). O sistema é adequado para práticas em ambulatório que necessitem de transferir dados para equipas médicas remotas. A solução proposta é uma alternativa eficaz à abordagem tradicional de processamento de bio-sinais fora do dispositivo de aquisição, apresentando um sistema centrado numa plataforma SoC FPGA, que processa os bio-sinais localmente. Dois subsistemas foram desenvolvidos, projectados para o dispositivo Zynq 7010, integrando núcleos IP customizados em hardware para acelerar o processamento das tarefas computacionalmente mais complexas. O subsistema PPG implementa o algoritmo de detecção de picos de autocorrelação para calcular ritmos cardíacos. O subsistema EEG consiste num classificador KNN a partir de sinais EEG pré-processados. As soluções hardware/software foram comparadas com as implementações de software, executadas no processador ARM da Zyng, obtendo uma aceleração de até 40 vezes. O sistema ocupa 36% dos recursos disponíveis na Zyng, evidenciando que novas funcionalidades podem ser adicionadas. O sistema proposto constitui uma base para sistemas biométricos mais complexos, que beneficiem da combinação de diferentes núcleos IP reutilizáveis. Este trabalho supera as limitações de microcontroladores e unidades de processamento genéricas, apresentando uma solução wearable escalável, autónoma, com grande capacidade de processamento e resposta em tempo-real.

**Palavras-chave:** Co-projecto *hardware/software*, Dispositivos *wearable* de monitorização, Electroencefalografia, Fotopletismografia, SoC FPGA

# Contents

| 1 | Intro | oduction                                                      | 1  |

|---|-------|---------------------------------------------------------------|----|

|   | 1.1   | Motivation                                                    | 1  |

|   | 1.2   | Objectives and contributions                                  | 2  |

|   | 1.3   | Outline                                                       | 3  |

| 2 | Bac   | kground on biometric signals processing and HW/SW co-design   | 5  |

|   | 2.1   | Electroencephalography                                        | 5  |

|   |       | 2.1.1 Signal processing                                       | 6  |

|   |       | 2.1.2 Related work                                            | 7  |

|   | 2.2   | Photoplethysmography                                          | 10 |

|   |       | 2.2.1 Applications and characteristics                        | 12 |

|   |       | 2.2.2 Related work                                            | 13 |

|   | 2.3   | FPGA-based medical devices                                    | 18 |

| 3 | Prop  | posed biometric system                                        | 21 |

|   | 3.1   | Heart rate calculator using PPG                               | 21 |

|   |       | 3.1.1 Selection of the algorithm and reference datasets       | 21 |

|   |       | 3.1.2 Algorithm description                                   | 22 |

|   |       | 3.1.3 Software application profiling                          | 26 |

|   | 3.2   | Emotion detector from EEG                                     | 28 |

|   |       | 3.2.1 Selection of the classifier and classification datasets | 28 |

|   |       | 3.2.2 KNN classifier description                              | 29 |

|   |       | 3.2.3 Software implementation                                 | 31 |

|   |       | 3.2.4 Software application profiling                          | 32 |

|   | 3.3   | High-level HW/SW architecture                                 | 34 |

| 4 | PPG   | G and EEG IP cores                                            | 37 |

|   | 4.1   | Development process and design techniques                     | 37 |

|   | 4.2   | PPG IP core                                                   | 38 |

|   |       | 4.2.1 Design and optimization                                 | 38 |

|   |       | 4.2.2 Design evaluation                                       | 44 |

|    |       | 4.2.3   | Design validation                           | 47 |

|----|-------|---------|---------------------------------------------|----|

|    | 4.3   | EEG I   | P core                                      | 49 |

|    |       | 4.3.1   | Design concept                              | 49 |

|    |       | 4.3.2   | Implementation of distances calculator core | 50 |

|    |       | 4.3.3   | Implementation of sort distances core       | 55 |

|    |       | 4.3.4   | Design validation                           | 61 |

| 5  | HW/   | /SW im  | plementation                                | 65 |

|    | 5.1   | Develo  | ppment board                                | 65 |

|    | 5.2   | Syster  | n integration                               | 66 |

|    |       | 5.2.1   | System description                          | 67 |

|    |       | 5.2.2   | Embedded software                           | 68 |

|    |       | 5.2.3   | System performance                          | 69 |

|    |       | 5.2.4   | Hardware resources utilization              | 69 |

|    | 5.3   | Accele  | eration results                             | 70 |

|    |       | 5.3.1   | PPG sub-system                              | 70 |

|    |       | 5.3.2   | EEG sub-system                              | 71 |

|    | 5.4   | Protot  | ype concept                                 | 72 |

| 6  | Con   | clusio  | IS                                          | 75 |

|    | 6.1   | Syster  | n improvements and future work              | 76 |

| Bi | bliog | raphy   |                                             | 79 |

| A  | Dim   | ension  | ing of PPG IP core internal variables       | 87 |

| в  | Bloc  | ck diag | ram of the biometric system                 | 89 |

# **List of Tables**

| 2.1  | Comparison of existing EEG research works.                                                      | 11 |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.2  | Overview of reviewed PPG researches.                                                            | 16 |

| 3.1  | Variation of number of indexes with sampling frequency.                                         | 27 |

| 4.1  | Number of PPG IP Version 1 function calls.                                                      | 39 |

| 4.2  | Data flow of variables passed to PPG IP Version 1                                               | 40 |

| 4.3  | Number of PPG IP Version 2 function calls.                                                      | 40 |

| 4.4  | Number of PPG IP Version 3 function calls.                                                      | 41 |

| 4.5  | Data flow of variables passed to PPG IP Version 4                                               | 41 |

| 4.6  | Number of PPG IP Version 4 function calls.                                                      | 42 |

| 4.7  | Dimensioning of the PPG IP core internal variables.                                             | 44 |

| 4.8  | Summary of the number of PPG IP accesses, from Version 1 to Version 7                           | 45 |

| 4.9  | Comparison between the results obtained by SW-only and optimized cores                          | 48 |

| 4.10 | Estimated hardware resources to be used by the PPG IP core                                      | 49 |

| 4.11 | Summary of classification accuracy, errors, resource utilization and latency of four wordlength | ۱  |

|      | versions of the EEG IP core.                                                                    | 63 |

| 4.12 | Estimated hardware resources to be used by the EEG IP cores                                     | 63 |

| 5.1  | Summary of timing constraints of the complete monitoring system, reported by Vivado             | 69 |

| 5.2  | Hardware resources used by the complete monitoring system.                                      | 70 |

| 5.3  | Execution times obtained by software-only and hardware/software implementations of the          |    |

|      | PPG sub-system                                                                                  | 71 |

| 5.4  | Execution times obtained by software-only and hardware/software implementations of the          |    |

|      | EEG sub-system                                                                                  | 72 |

| A.1  | Extended table containing the dimensioning of the PPG IP core internal variables                | 88 |

# **List of Figures**

| 1.1 | Proposed system architecture.                                                               | 3  |

|-----|---------------------------------------------------------------------------------------------|----|

| 2.1 | Electrode-positioning standard by International 10/20 System [5]                            | 6  |

| 2.2 | Russell's [7] Valence-Arousal model [8]                                                     | 6  |

| 2.3 | Typical PPG waveform [24]                                                                   | 7  |

| 2.4 | Operation of PPG finger sensors by transmission and reflection [45]                         | 12 |

| 2.5 | Typical PPG waveform [49].                                                                  | 12 |

| 3.1 | Raw and AC PPG signals.                                                                     | 23 |

| 3.2 | PPG linear trend removal.                                                                   | 24 |

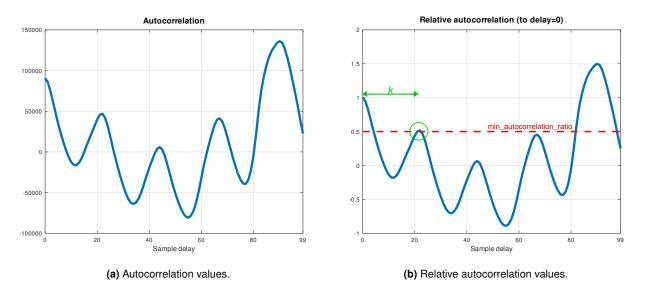

| 3.3 | Autocorrelation of PPG signal for different delays.                                         | 25 |

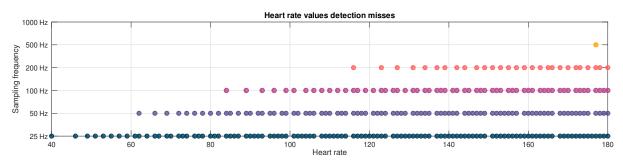

| 3.4 | Heart rate detection misses varying with sampling frequency.                                | 27 |

| 3.5 | Example of an abstract representation of KNN's training set and test instance, and com-     |    |

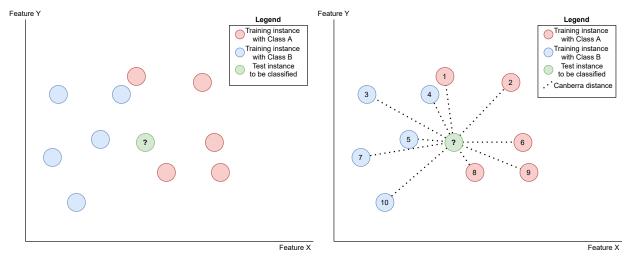

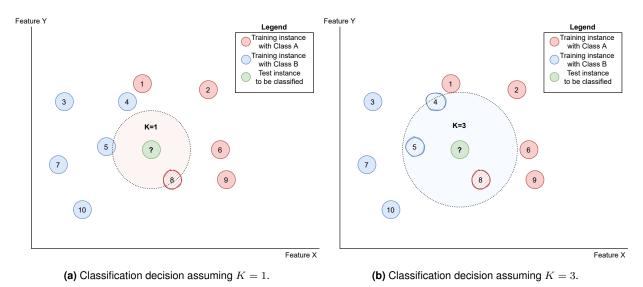

|     | putation of Canberra distances.                                                             | 31 |

| 3.6 | Classification of the test instance using different values of $K$                           | 31 |

| 3.7 | Graphical representation of the five-emotion mapping.                                       | 34 |

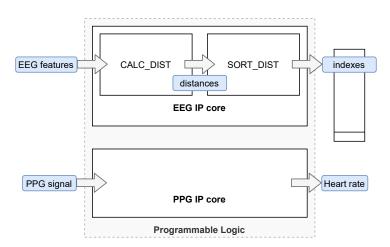

| 3.8 | Proposed system implementation.                                                             | 36 |

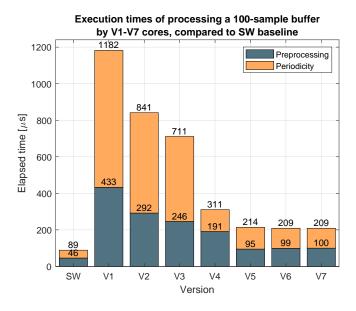

| 4.1 | Execution times of versions V1-V7, compared to the SW baseline.                             | 46 |

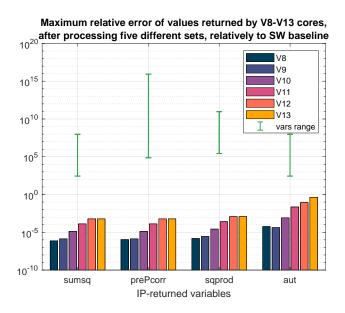

| 4.2 | Maximum relative error obtained by versions V8-V13, compared to SW baseline                 | 46 |

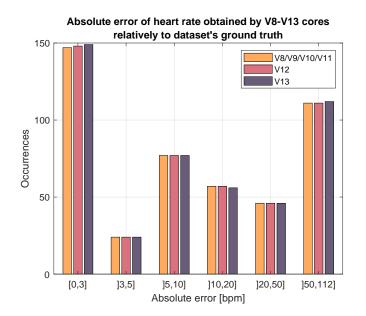

| 4.3 | Absolute errors obtained by fixed-point cores when processing real PPG database             | 48 |

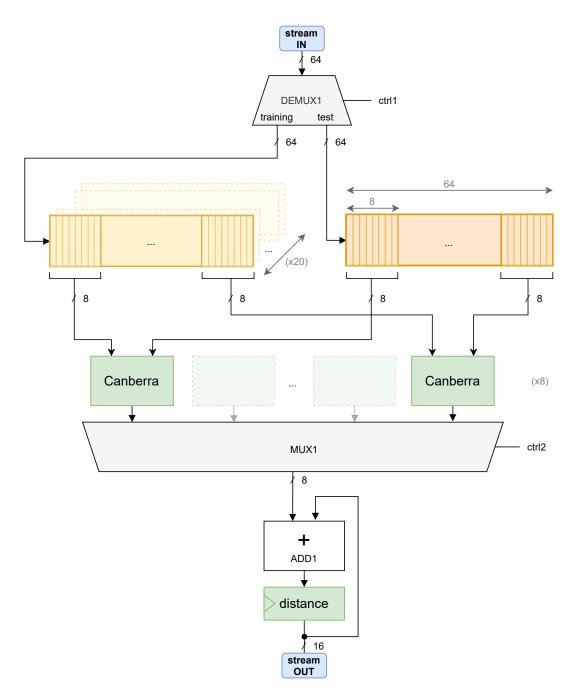

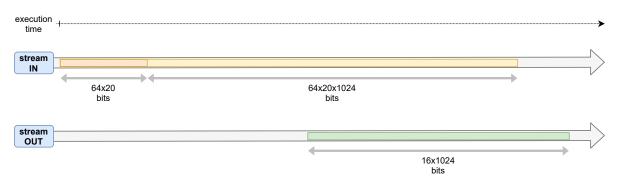

| 4.4 | Block diagram of calculate distances EEG core                                               | 52 |

| 4.5 | Data flow of calculate distances EEG core.                                                  | 53 |

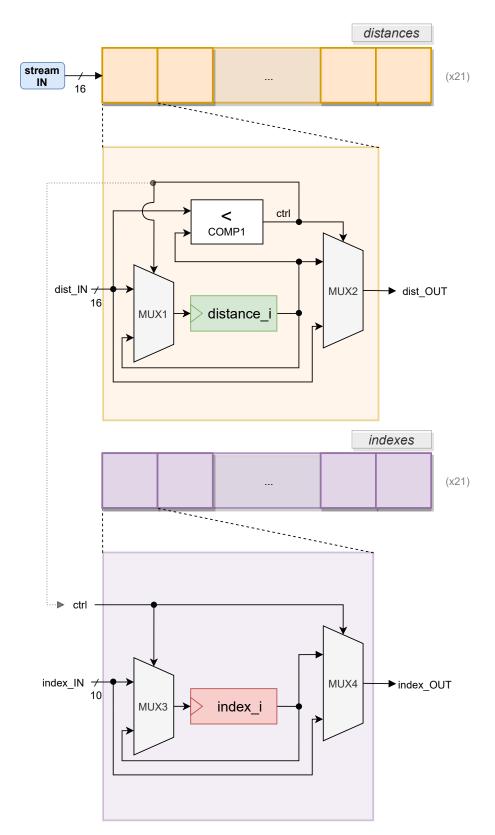

| 4.6 | Block diagram of sort distances EEG core.                                                   | 60 |

| 5.1 | ZYBO development board.                                                                     | 66 |

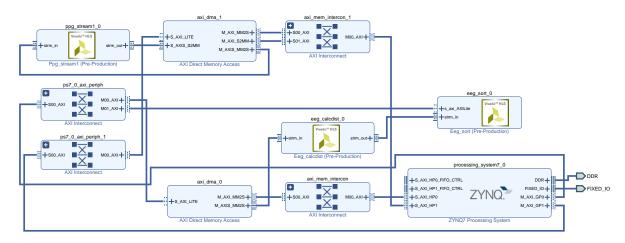

| 5.2 | Proposed system implementation.                                                             | 66 |

| 5.3 | Block diagram representing the integration of the biometric system, obtained in Vivado IDE. | 67 |

| 5.4 | Materialization of the implemented system into a prototype                                  | 72 |

| 5.5 | Biometric sensors.                                                                          | 73 |

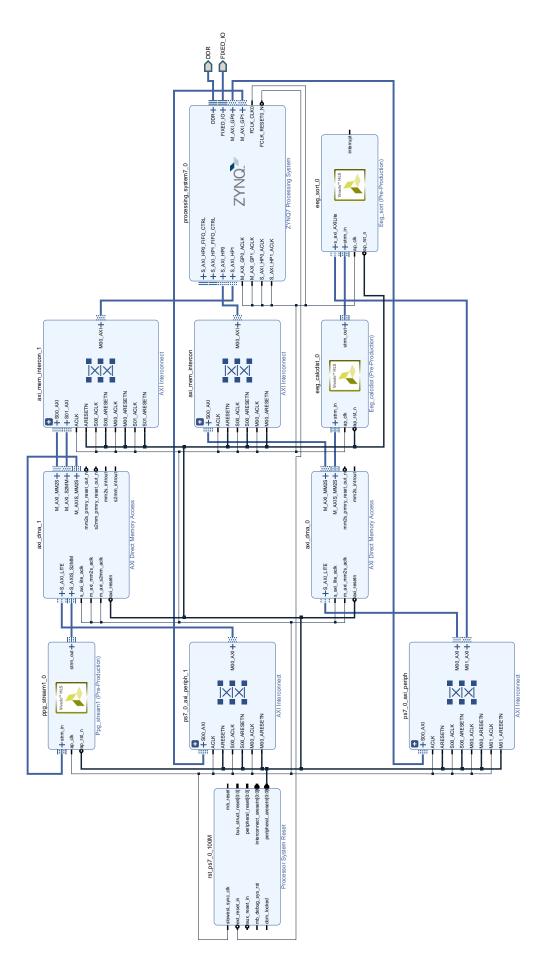

| B.1 | Block diagram of the complete biometric project.                                            | 90 |

# Listings

| 4.1 | Declaration and interfaces of PPG IP Version 1 core.              | 39 |

|-----|-------------------------------------------------------------------|----|

| 4.2 | Declaration of PPG IP Version 2 core.                             | 40 |

| 4.3 | Declaration and interfaces of PPG IP Version 14 core.             | 44 |

| 4.4 | Declaration and interfaces of EEG calculate distances core        | 51 |

| 4.5 | Pseudo-code of <i>Canberra</i> block.                             | 53 |

| 4.6 | Declaration of local memory for storing test set features         | 55 |

| 4.7 | Declaration and interfaces of EEG sort distances core             | 56 |

| 4.8 | Pseudo-code of insertion sort algorithm, based on a sorted array. | 57 |

# Acronyms

| ABP   | Arterial Blood Pressure       |

|-------|-------------------------------|

| ADC   | Analog-to-Digital Converter   |

| ALU   | Arithmetic Logic Unit         |

| avAE  | Average Absolute Error        |

| ΑΧΙ   | Advanced eXtensible Interface |

| BCI   | Brain-computer Interfaces     |

| BLE   | Bluetooth Low Energy          |

| BRAM  | Block RAM                     |

| CLB   | Configurable Logic Blocks     |

| DDR   | Double Data Rate              |

| DMA   | Direct Memory Access          |

| DSP   | Digital Signal Processor      |

| ECG   | Electrocardiogram             |

| EEG   | Electroencephalography        |

| FF    | Flip-flop                     |

| FPGA  | Field-Programmable Gate Array |

| GCC   | GNU Compiler Collections      |

| GP    | General Purpose               |

| HLS   | High-Level Synthesis          |

| HP    | High Performance              |

| HR    | Heart Rate                    |

| HW/SW | Hardware/Software             |

| IC               | Integrated Circuit                          |

|------------------|---------------------------------------------|

| IP               | Intellectual Property                       |

| IR               | Infra-red                                   |

| I <sup>2</sup> C | Inter-Integrated Circuit                    |

| KNN              | K-Nearest Neighbours                        |

| LDA              | Linear Discriminant Analysis                |

| LUT              | Look-up table                               |

| MAE              | Mean Absolute Error                         |

| РСА              | Principal Component Analysis                |

| PL               | Programmable Logic                          |

| PPG              | Photoplethysmography                        |

| PPV              | Positive Predictive Values                  |

| PS               | Processing System                           |

| PTT              | Pulse Transit Time                          |

| QDA              | Quadratic Discriminant Analysis             |

| RAM              | Random-access Memory                        |

| RMSE             | Root Mean Squared Error                     |

| RR               | Respiratory Rate                            |

| RTL              | Register Transfer Level                     |

| SCL              | Serial Clock Line                           |

| SDA              | Serial Data Line                            |

| SoC              | System-on-Chip                              |

| STA              | Static Timing Analysis                      |

| SVM              | Support Vector Machine                      |

| UART             | Universal Asynchronous Receiver/Transmitter |

| XADC             | Xilinx Analog-To-Digital Converter          |

| XSA              | Xilinx Support Archive                      |

| ZYBO             | ZYnq BOard                                  |

# **Chapter 1**

# Introduction

Over the last decades, wearable monitoring systems have been researched, developed and progressively enhanced to support healthcare needs, and fit for real-time bio-signals processing, including heart rate measurement and emotional state recognition. As a result, wearable devices are becoming more portable, user-friendly, accurate and reliable, which minimizes the disturbance to user's daily routine. Moreover, combined with access to wireless Internet, these devices are being used in remote subject monitoring. This thesis proposes a wearable solution that can assist different groups of people, as it can provide remote healthcare tracking, overcoming the state-of-the-art systems.

#### 1.1 Motivation

Medical systems monitor valuable information from biometric signals, such as cardiac activity, physical movements and brain activity. More specifically, brain-computer interfaces (BCI) are developed to allow disabled people to control an external device using electrical signals from the brain, overcoming physical or neuromuscular limitations. As such, electroencephalography (EEG), a technique for monitoring brain activity, is widely used in these applications.

Wearable EEG devices have been given prominence in the last couple decades, although most of those systems are built for operation in a laboratory environment. That is, under controlled conditions with static elements, such as simulated ambience, luminosity or background noise [1]. Therefore, these applications do not prioritize portability or hardware simplicity, but rather high efficiency on signal acquisition and processing. "Beyond wearable" EEG, as suggested in [1], are closer to real life applications, reducing wires and becoming more comfortable and usable. However, such devices face the problem of battery autonomy. The commercialized EEG products available in the market last up to 9 hours. The inclusion of multiple sensors, such as optoelectronic sensors, thermometers and accelerometers, urges power efficiency during signal processing. Larger batteries provide longer autonomy despite of being impractical, while smaller ones grant more mobility but impose frequent charging to the user. Moreover, the high complexity of a monitoring system is often linked to larger devices that do not fit the wearable needs. The thesis proposes a solution that offers the capacity of handling complex bio-signals, while

guaranteeing portability.

#### 1.2 Objectives and contributions

The novelty of this work is the usage of a System-on-Chip (SoC) Field-Programmable Gate Array (FPGA) to take advantage of high processing speed and reconfigurable logic. This kind of device is useful to create flexible and customized hardware solutions with high performance and low power consumption. It is intended to perform signal processing tasks locally and online, instead of transmitting the collected raw sensor data to be processed by an external server, as conventional systems do. By doing the computations locally, at the node, the required bandwidth and power consumption are minimized. Furthermore, this architecture offers parallel computation, which is suitable to handle multiple biometric signals at a time. Such functionalities overcome the limitations of conventional wearable solutions that use general-purpose CPU.

The proposed system intends to measure a person's heart rate using photoplethysmography (PPG) and to assess emotional state via EEG. PPG is a technique widely used in smartwatches, that uses a light source pointed to the skin to detect blood volume changes in a vascular tissue, which is captured by a sensor and translated to an electric signal. Blood variations are synchronous to heart beat, so heart rate can be computed after processing this signal. With EEG, the electric activity of the brain is recorded using electrodes placed on the head, resulting in a set of signals with multiple frequencies. Emotion recognition is achieved after processing EEG signal, extracting relevant features (or patterns) from it and building a classifier that identifies emotions accurately. The biometric system demonstrates the use of two independent sub-systems, each one dedicated to the respective bio-signal. The PPG sub-system will handle PPG samples since their acquisition by an optoelectronic sensor, with the purpose of determining instant heart rate values. The EEG sub-system will consist of a machine learning classifier that takes as input preprocessed EEG signals and returns the predicted emotion.

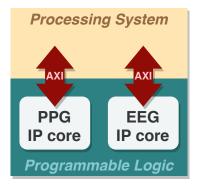

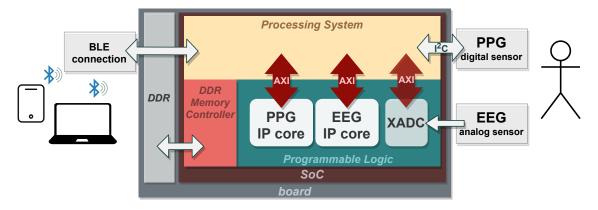

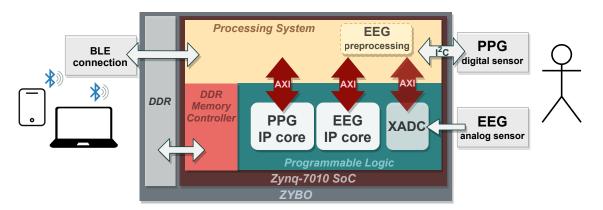

The main goal is to take advantage of SoC FPGA to conceive a real-time monitoring system for bio-signals. One contribution of this work is to develop dedicated hardware to process the bio-signals collected by the sensors. This will be achieved by designing reconfigurable logic accelerators, which contain preconfigured functions, as Intellectual Property (IP) cores. These blocks are intended to accelerate the processing of specific bio-signals. The processing tasks are distributed between software-only instructions and the custom IP cores, constituting a hybrid Hardware/Software (HW/SW) architecture. The most complex tasks are handled by the IP cores, and the remaining ones are implemented in embedded software run by the processor. An objective of the thesis is to run the processing tasks in shorter times, when compared to the software-only implementations. The concept of the zynq-7010 SoC. Two main components can be distinguished: the Processing System (PS) – corresponding to the dual-core processor – and the Programmable Logic (PL) – related to the FPGA fabric. The IP cores, included in the PL, are connected to the PS by Advanced eXtensible Interface (AXI) buses. Moreover, this work aims to find the optimal design of the system, such that the hardware components necessary for its

implementation fit the resources available in the targeted platform.

Figure 1.1: Proposed system architecture.

The system based on a SoC FPGA will be demonstrated using the ZYnq BOard (ZYBO) [2]. This board includes a Zynq-7010 All Programmable SoC<sup>1</sup>, which is composed of a dual-core ARM Cortex-A9 processor<sup>2</sup>. This dedicated hardware offers programmable logic solutions, reducing design complexity and optimizing performance-per-watt ratio, being advantageous to this application.

#### 1.3 Outline

The thesis is organized as follows. Chapter 2 provides an overview of the PPG and EEG techniques and presents the state-of-the-art algorithms for processing the bio-signals. Moreover, the chapter reviews FPGA-based medical devices similar to the proposed by this thesis. Chapter 3 introduces the biometric sub-systems. It is described the process behind the selection of the algorithm for handling PPG signals and the classifier to identify emotions from EEG. The processing steps involved in both sub-systems are detailed and analysed. The chapter closes with the high-level architecture of the biometric system. The development of the hardware modules that accelerate the processing tasks is addressed in Chapter 4. The integration of those modules with embedded software is described in Chapter 5. The acceleration results obtained by the sub-systems are provided. Chapter 6 summarizes the conclusions of this work and suggests some directions for future work.

<sup>&</sup>lt;sup>1</sup>Zynq-7000 SoC family webpage: https://www.xilinx.com/products/silicon-devices/soc/zynq-7000.html; accessed on 22<sup>nd</sup> May 2020.

<sup>&</sup>lt;sup>2</sup>Cortex-A9 webpage: https://developer.arm.com/ip-products/processors/cortex-a/cortex-a9; accessed on 22<sup>nd</sup> May 2020.

## Chapter 2

# Background on biometric signals processing and HW/SW co-design

This chapter exposes and clarifies theoretical concepts used throughout this report, including an overview of relevant related work. The underlying framework of the thesis includes the biometric techniques EEG and PPG, but also the application of FPGA in biomedical prototypes. When analysing related researches, emphasis is placed on those supported by source code written in C, a low-level language suitable for embedded design.

#### 2.1 Electroencephalography

Electroencephalography is a non-invasive technique for probing electric activity of the human brain neurons, by attaching electrodes on the scalp that detect voltage fluctuations upon ion flow [3]. Five major frequency bands can be identified in brain waves, depending on the neural activity – delta (1-3 Hz), theta (4-7 Hz), alpha (8-13 Hz), beta (14-30 Hz) and gamma (31-50 Hz) [3] –, whose frequency pattern changes may denote a response to an external stimulus, or some brain disorder [4]. Activities such as sleeping, exercising or meditation can also be detected in brain waves.

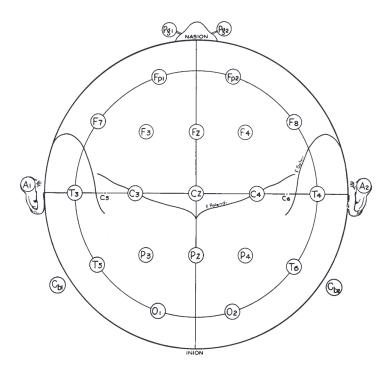

The positioning of electrodes is crucial for accurate signal acquisition, given the scope of the application. The standardization is set by the International 10/20 System [5], represented in Figure 2.1, although extended versions have been proposed [6]. There are two EEG montage types: referential and bipolar. Referential considers a common reference electrode, from which the potential difference of all electrodes is computed. In bipolar montage, each electrode is associated with a reference.

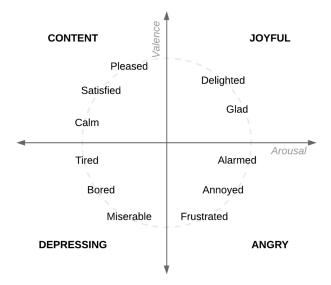

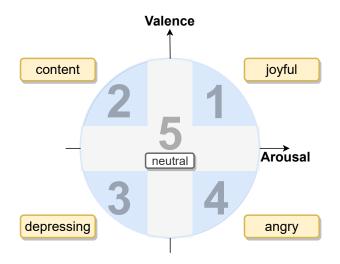

A common application of EEG is emotion classification, which maps and recognizes patterns on features of EEG signals from different known emotions. Russell [7] defined arousal as the metric for awareness or unawareness during an activity, and valence as the metric for pleasure or displeasure. Both quantities are described a 2D plane, where arousal is in the horizontal axis and valence in the vertical axis. The resulting emotion in each quartile is a combination of the two. The model is represented in Figure 2.2. According to Davidson et al. [9], positive valence activates the left side of the

**Figure 2.1:** Electrode-positioning standard by International 10/20 System [5]. 'Pg' stands for pharyngeal area, 'Fp' for fronto polar, 'F' for frontal, 'T' for temporal, 'C' for central, 'P' for parietal, 'O' for occipital and 'Cb' for cerebellar.

Figure 2.2: Russell's [7] Valence-Arousal model [8].

anterior temporal region, while negative valence stimulates the right side of frontal and anterior temporal regions. Regarding the relation between emotion dimensions and the power of major frequency bands, as per Kandel et al. [10], alpha is visible on parietal and occipital regions and associated to low arousal and high valence state; beta is prominent in frontal area during high arousal activities; delta and theta are related to low arousal.

#### 2.1.1 Signal processing

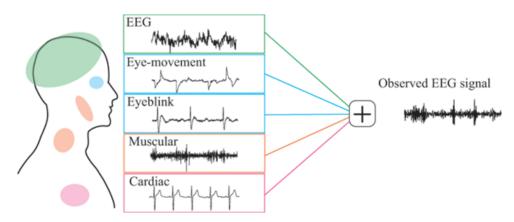

Processing the EEG signal comprises several steps, namely noise reduction, signal enhancement, feature extraction and classification. During the acquisition via the electrode, the recorded signal is attenuated by skin tissues and bones [10], but also subject to noise caused by muscular activities, eye movements, eye blinks and cardiac signals [11] [12], as represented in Figure 2.3. In fact, normal EEG signal amplitude ranges microvolts, although a single neuron promotes voltage changes of millivolts [10]. Therefore, in order to remove this noise, the EEG signal is preprocessed and its quality improved [11] [13]. Most of the possible methods that perform this use spatial or temporal filters, or both [11]. Spatial filters combine the recorded signals into a single one with higher Signal-to-Noise Ratio (SNR) [14]. Some examples, supported by references containing additional details, include Independent Component Analysis (ICA) [15], Common Average Referencing (CAR) [16], Surface Laplacian (SL) [17], Principal Component Analysis (PCA) [18] and Common Spatial Patterns (CSP) [19]. On the other hand, temporal filters attenuate specific frequencies of the signal and select those bands carrying relevant information. This can be achieved by applying discrete or fast Fourier transforms, finite impulse response (FIR) filters or infinite impulse response (IIR) filters [20]. After signal preprocessing, features are extracted, that is, patterns are identified in order to reduce dimensional space without losing essential information [21]. There are several extraction methods, such as Wavelet Transformations (WT) [21], Wavelet Packet Decomposition (WPD) [22] and Autoregressive (AR) [23], but also ICA and PCA can be applied in this step. Finally, classification is performed by, for example, Support Vector Machine (SVM), Linear Discriminant Analysis (LDA), Neural Network (NN) or k-Nearest Neighbour (KNN) [13]. Also, some of these classifiers have been extended to adaptive versions [14].

Figure 2.3: Different noise sources affecting a typical EEG waveform [24].

#### 2.1.2 Related work

EEG has been used in several academic works with different purposes, namely emotion recognition [12], seizure and traumatic brain injury detection [25], but also identification of alcoholism, depression, dementia, epilepsy, Alzheimer and Parkinson [4]. In this section, the scope of the analysis confines to emotion recognition.

Lin et al. [26] studied the emotional responses from brain activity to stimuli of different music. Brain signals from 26 subjects were recorded by 24 electrodes, namely FP1, FP2, F7, F8, F3, F4, FT7, FT8, FC3, FC4, T7, T8, P7, P8, C3, C4, TP7, TP8, CP3, CP4, P3, P4, O1 and O2. The classification was performed by a support vector machine (SVM) into four emotional states, according to 2D emotion

model: 'joy', 'pleasure', 'angry' and 'sadness'. The classification accuracy obtained was 82.37%.

Vijayan et al. [27] proposed a subject independent algorithm involving wavelet transform, Shannon entropy, cross correlation and auto-regressive modelling. Four emotions, namely 'exciting', 'happy', 'sad' and 'hate', were identified by a multi class SVM. Tested in a non-real time mode, this algorithm was applied in a dataset containing brain signals of 32 subjects, stimulated by music videos. Multiple combinations of three, six and seven electrodes were evaluated. The highest accuracy obtained was 94.097%, with seven electrodes located at P7, P3, PZ, PO3, O1, CP2 and C4. Using six electrodes on FP1, AF3, F7, P7, P3 and PZ, an accuracy of 69.767% was achieved. Dividing this combination into halves, FP1, AF3 and F7 and P7, P3 and PZ, the accuracies reached 28.447% and 78.465%, respectively.

Commercial brain sensing devices are also used. Dhindsa et al. [28] collected brain signals using a *Muse* headband<sup>1</sup>, containing four electrodes located at T9, FP1, FP2 and T10, from 40 subjects. The goal was to identify the emotional reaction to videos, from a set of 11 emotions – 'interest', 'amusement', 'happiness', 'sadness', 'fear', 'disgust', 'anger', 'hope', 'relief', 'surprise' and 'sympathy'. Two classifiers were used: SVM and logistic regression (LR). When performing leave-one-subject-out cross-validation, SVM obtained higher accuracies than LR, with 75% mean.

Another commonly used device for EEG signal extraction is *Emotiv Epoc* headset<sup>2</sup>, equipped with 14 electrodes (AF3, AF4, F3, F4, F7, F8, FC5, FC6, P7, P8, T7, T8, O1 and O2). Liu et al. [29] carried an experiment with 30 subjects in order to identify movie-induced emotions. The accuracy was evaluated differently. The distinction between positive and negative emotions obtained 86.62% accuracy. The identification of a specific positive emotion, within the set of 'joy', 'amusement' and 'tenderness', reached 86.43%; for negative emotions, 'anger', 'disgust', 'fear' and 'sadness', this value stood at 65.09%. No accuracy data is presented regarding the emotion recognition within the set containing all aforementioned emotions. This device was also used by Anh et al. [30], but only three electrodes, AF3, FC6 and F4, were used for emotion recognition. 100 subjects were stimulated by a photo database and LIBSVM [31] used as classification method. Five emotions were considered: 'happy', 'relaxed', 'neutral', 'sad' and 'angry'. An overall accuracy of 9% was obtained.

Schaaff et al. [32] developed a three-emotion recognition system with a SVM with radial basis function (SVM-RBF) classifier and leave-one-out cross validation. The classes were 'pleasant', 'unpleasant' and 'neutral'. The visualization of images aroused emotions of five subjects, recorded by four electrodes – FP1, FP2, F7 and F8. Focusing on the alpha frequency, the classification accuracy was 48.89%.

Four electrodes were also used by Ali et. al. [33] to detect one of the four emotions of the 2D emotion model – FP1, FP2, F3 and F4 –, because of "pre-frontal cortex in emotion regulation and conscious experience". Feature extraction involved wavelet energy, modified energy, wavelet entropy and statistical moments. Three classification methods were evaluated: quadratic discriminant analysis (QDA), k-nearest neighbours (KNN) and SVM-RBF. Using EEG signals from DEAP, a preprocessed dataset concerning 32 subjects [34], these experiments obtained 60.78%, 75.53% and 83.87% accuracy,

<sup>&</sup>lt;sup>1</sup>Muse website: https://www.choosemuse.com/; accessed on 19<sup>th</sup> March 2020.

<sup>&</sup>lt;sup>2</sup>Emotiv website: https://www.emotiv.com/; accessed on 19<sup>th</sup> March 2020.

respectively.

Wei et al. [35] developed their own wearable emotion detection headband containing four electrodes. The proposed algorithm combined features such as power spectral density, signal power and common spatial pattern. The classification using linear discriminant analysis (LDA) aimed the distinction of positive and negative emotions. They also tested two electrode locations: FP1, FP2, T3 and T4; A1, FP2, F7 and F8. Subject-independent accuracies of 64.73% and 66.74% were respectively achieved. The experiment was undertaken by 12 subjects stimulated by picture visualization.

Chatchinarat et al. [36] studied the effects of both number and location of electrodes and frequency bands for emotion classification, using DEAP dataset and the SVM classifier. This review addresses three out of ten tested combinations of electrodes: FP1 and FP2; T3 and T4; O1 and O2. When using five bands as feature per electrode channel, the classification of four emotions following the 2D emotion model reached accuracies of 30.73%, 30.73% and 28.65%, respectively. The authors also computed the classification accuracy using only the frequency bands alpha and beta as features, comparing it to the five-band case. These results were presented considering two-emotion classification, where arousal and valence axis are separated. Considering only the arousal, the accuracy using two bands was 57.81% for all three electrode combinations; using five bands the accuracy using two bands reached 53.65%, 57.29% and 47.40%, respectively; using five bands the accuracy achieved 47.40%, 56.25% and 56.25%. This demonstrates that using two bands is almost similar to using five bands.

A similar study was conducted by Li et al. [37], where the classification of valence and arousal dimensions was tested varying the amount of EEG channels. The preprocessed signals of the DEAP dataset were decomposed by wavelet transform, to obtain entropy and energy as EEG features of a KNN classifier. In the experiment, it was confirmed that classification accuracy increases with the number of channels. Using 32 channels, the valence and arousal classifications were 95.7% accurate. Using 10 channels, the accuracies dropped to 89.54% and 89.81%, respectively. The article mentions a MATLAB program, however no implementation is provided.

The KNN and SVM classifiers were compared in terms of accuracy of assessing the levels of valence and arousal by Mohammadi et al. [38]. Features were obtained by discrete wavelet transform (DWT) to decompose the EEG signal into the main frequency bands. The input data corresponded to DEAP dataset, however a subset of 10 EEG channels was considered. The results showed that KNN outperformed SVM, and the maximum classification accuracies obtained by KNN for valence and arousal were, respectively, 86.75% and 84.05%. Moreover, this work studied the effects of the temporal window and the combinations of EEG electrodes on classification accuracy, besides the classifier. Wider temporal windows led to more accurate results. The electrode pair FP1-FP2 was regarded as the most reliable for identifying emotions.

Hatamikia et al. [39] analysed the performance of different feature selection methods which were tested using three emotion classifiers – LDA, QDA and KNN. The preprocessed version of the DEAP dataset was consumed. The target application was to distinguish three intensity levels (classes) of valence and arousal. Using each feature selection method, the KNN classifier obtained the highest

9

classification accuracy results. The best accuracy results regarding the valence class were 51.20% for LDA, 57.42% for QDA and 61.10% for KNN. The best results for the arousal class were, respectively, 52.36%, 57.18% and 65.16%. The KNN obtained the highest accuracy.

Table 2.1 summarizes the characteristics of the aforementioned EEG researches. It includes the classification method, the number of the electrodes, the rounded values for the classification accuracies followed by the classification scope. The source code and the dataset used are also referred, if reported by the authors. The researches did not provide complete open-source implementations of the emotion detection systems, although some refer the tools used during the development. For instance, [27], [28] and [32] referred a MATLAB implementation, without providing its source code publicly. [33] developed an accurate and portable emotion classification system, but no implementation references were provided. [35] pointed a public available tool, which is supported in C language, however no software specification of the algorithm could be extracted.

Most of the available open-source repositories implemented an emotion detector using high-level languages, such as Python and MATLAB. This kind of languages is relevant to bioinformatics, being practical to translate the developed algorithms into preliminary software instructions. Such implementations are not convertible into an embedded system design, since lower level languages are required. Therefore, it is necessary to select the best classifier that may be specified in a low-level language, namely C. According to [12], the SVM and KNN classifiers are the most used in emotion recognition applications. Their classification accuracy results varied among the reviewed researches listed on Table 2.1. Both classifiers are suitable candidates to integrate the biometric system. Analysing the working principle of these methods, and privileging the feasibility of mapping a classifier into a low-level language implementation, the KNN will be considered in the final solution, to distinguish emotions of Russell's 2D model. In fact, at the time this work was carried out, no software implementations were found, facilitating the process of translating its algorithm into low-level instructions.

#### 2.2 Photoplethysmography

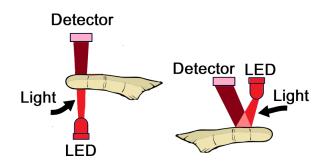

Photoplethysmography (PPG) is an optical technique that detects blood volume changes in a microvascular tissue [43]. PPG uses a light source for emitting light to the tissue and a photodetector for measuring the consequent received light, by transmission or reflection as seen in Figure 2.4, from which the blood volume variation is estimated. The principle of PPG is as follows. During the cardiac cycle, arteries suffer blood volume reduction when transiting from the systolic phase to the diastolic phase [44]. The PPG sensor detects this change optically and its photodetector converts the received light energy into an electrical current [43]. A waveform can be acquired and some physiological parameters extracted; for instance, the variability of the time between heartbeats [45].

Typically, red LEDs are used for light emission, since red and near infrared light pass more easily through water, the main constituent of tissues [43]. Green LEDs are also commonly chosen in several experiments [46]. Some studies suggested that, comparing to red light, green is more suitable for pulse

| Research | Classifier        | Electrodes                               | Accuracy                                                                                                                      | Classes                     | Source code               | Dataset |

|----------|-------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|---------|

| [26]     | SVM               | 24                                       | 82.4%                                                                                                                         | 2D model                    | 🖌 BSVM [40]               | uwo     |

| [27]     | SVM               | 3 (FP1 AF3 F7)<br>3 (P7 P3 PZ)<br>6<br>7 | 28.4%<br>78.5%<br>69.8%<br>94.1%                                                                                              | 2D model                    | X MATLAB                  | DEAP    |

| [28]     | SVM               | 4 (T9 FP1 FP2 T10)                       | 75.0%                                                                                                                         | 11 emotions                 | X MATLAB<br>V FBAR [41]   | имо     |

| [29]     | SVM               | 14                                       | 86.6% <sup>b</sup>                                                                                                            | 0 <del>1</del>              | X EEGLAB [42]<br>✓ LIBSVM | имо     |

| [30]     | SVM               | 3 (AF3 FC6 F4)                           | 9.0%                                                                                                                          | 2D model + 'N' <sup>a</sup> | V LIBSVM                  | uwo     |

| [32]     | SVM               | 4 (FP1 FP2 F7 F8)                        | 48.9% <sup>b</sup>                                                                                                            | 1D + 'N' <sup>a</sup>       | X MATLAB<br>V LIBSVM      | UMO     |

| [33]     | QDA<br>KNN<br>SVM | 4 (FP1 FP2 F3 F4)                        | 60.8%<br>75.5%<br>83.9%                                                                                                       | 2D model                    | ×                         | DEAP    |

| [35]     | LDA               | 4 (A1 FP2 F7 F8)                         | 66.7% <sup>b</sup>                                                                                                            | 1D                          | X OpenViBE                | uwo     |

| [37]     | KNN               | 32                                       | 95.7% <sup>b c</sup>                                                                                                          | 2D model                    | <b>X</b> MATLAB           | DEAP    |

| [38]     | KNN               | 10                                       | 86.7% <sup>b</sup><br>84.0% <sup>c</sup>                                                                                      | 2D model                    | ×                         | DEAP    |

| [39]     | LDA<br>QDA<br>KNN | 32                                       | 51.2% <sup>b</sup> , 52.4% <sup>c</sup><br>57.4% <sup>b</sup> , 57.2% <sup>c</sup><br>61.1% <sup>b</sup> , 65.2% <sup>c</sup> | 2D model                    | ×                         | DEAP    |

| [36]     | SVM               | 2 (FP1 FP2)                              | 30.7%                                                                                                                         | 2D model                    | ✓ LIBSVM                  | DEAP    |

|          |                   |                                          |                                                                                                                               |                             |                           |         |

Table 2.1: Comparison of existing EEG research works.

<sup>a</sup> 'N' stands for 'neutral' emotion.

<sup>b</sup> Classification accuracy referred to class 'valence'.

<sup>c</sup> Classification accuracy referred to class 'arousal'.

Figure 2.4: Operation of PPG finger sensors by transmission (left) and reflection (right) [45].

rate monitoring [47] and under motion artifact conditions [48].

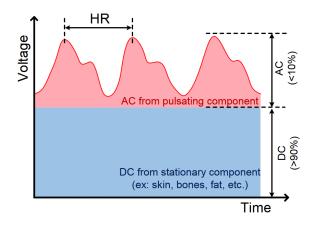

A PPG signal comprises two components: a pulsatile (AC), given by cardiac variations in blood volume caused by heartbearts, and a superimposed (DC), variable with some anatomic factors, such as respiration, thermoregulation, vasomotor and sympathetic nervous system activities [46] [43]. These components can be seen in Figure 2.5, where a typical PPG waveform is represented.

Figure 2.5: Typical PPG waveform [49].

#### 2.2.1 Applications and characteristics

The monitoring and analysis of PPG signal unveils a wide set of clinical applications, namely measurement of heart rate, blood pressure, respiratory rate, blood oxygen saturation and several vascular assessments. It can also be incorporated into detection tools of some cardiovascular diseases, such as vascular ageing [43].

An alternative method is electrocardiogram (ECG), a representation of the electrical activity of the heart, measured by multiple leads attached on body surfaces [50]. Several practical works in the literature that include PPG technologies use ECG for reference values. PPG does not have a complex hardware implementation nor the need of a reference signal, unlike ECG [45]. PPG is also regarded as a non-invasive and low-cost method [43]. Therefore, it is a portable, ready-to-use and convenient device from the user point of view. PPG sensors can be placed on different anatomical positions – forehead, earlobe, torso, wrist, fingertip and ankle –, but PPG signal has higher quality at earlobes or fingertips [46].

PPG also faces some disadvantages, such as sensibility to subject motion, probe-tissue movement and ambient light interference [43]. Also, PPG recordings vary with subject anatomy and the magnitude is controlled by the pressure applied by the wearable device on the skin [46].

#### 2.2.2 Related work

There are several techniques of processing PPG signal that vary with the different kinds of applications. For this application, it is intended to use an algorithm with an implementation associated and preferably supported by both source code and dataset for test and validation purposes. This review addresses research works and publicly available repositories.

#### **Research works**

A simple and low complexity algorithm for detecting pulse peak has been presented by Jang et al. [51]. The method used a slope sum function (SSF) with an adaptive thresholding scheme, but also cascaded recursive digital filters, for the initial noise removal. Testing was performed using the health improvement and management system (HIMS) database, containing pulse peaks manually annotated. Two rules were applied for true detection: the index-based and the interval-based. The first one declares 'true' if "the difference between manual and algorithm generated annotations is less than three samples (approximately 5 ms) intervals". The latter considers a similar variance regarding the QRS interval. These evaluation metrics obtained positive predictive values (PPV) of 60.57% and 80.29%, respectively. The authors have concluded that the proposed algorithm was suitable for real-time applications, such as pulse rate monitoring, identification of other characteristic points of the PPG signal referred to the pulse peak, but also investigation of both pulse transit time and pulse rate variability. However, no source code on the developed algorithm is provided.

Zong et al. [52] also developed an algorithm using SSF and adaptive thresholding, for detecting arterial blood pressure (ABP) pulses. The MIT-BIH Polysomnographic Database<sup>3</sup> – containing 368,364 beats annotated in ECG signals – was used for evaluating the accuracy, obtaining 99.31% of correlation. A second evaluation approach compared the ABP pulse detections to a newly created reference database comprising 39,848 ABP annotations, where the accuracy stood at 96.41%. The source code in C language is freely available on PhysioNet [53] website, included in PhysioToolkit.

A heart rate detection system using an Arduino board was developed by Das et al. [54]. The simple algorithm based on short term autocorrelation technique over the time shifted PPG signal, acquired from ten healthy volunteers in real-time. The distance between peaks originated by the autocorrelation function is used to compute heart rate. The system validation consisted on the comparison to BIOPAC MP150 system, while testing was performed using PhysioNet's MIMIC database [55]. Results have shown no difference between the HR measurements given by both systems, whether the signal presented clean or noisy waveforms. Despite the algorithm's simplicity and implementation in Arduino, no code was referred.

<sup>&</sup>lt;sup>3</sup>PhysioNet website: https://www.physionet.org/content/slpdb/1.0.0/; accessed on 17<sup>th</sup> April 2020.

Similarly, another system for heart rate analysis containing an Arduino was conceived by van Gent et al. [56]. The authors developed HeartPy, a Python toolkit, but also its implementation in embedded C, in order to be deployed in Arduino. The algorithm comprised three steps: preprocessing involved peak enhancement, FIR filtering, and outlier detection; peak detection consisted of the adaptive peak detection threshold method; error detection is corrected by thresholding the sequence of RR-intervals, that is, elapsed time between peaks. This package was validated on a PPG dataset collected in previous work – Physionet's BIDMC PPG and Respiration Dataset [57]. The heart rate estimation presented a root mean squared error (RMSE) of 4.18 bpm. Also, comparing to two "popular available open source algorithms", Pan-Tompkins QRS and HRVAS ECGViewer, the developed toolkit obtained the lowest error rates. However, these algorithms were designed and intended to be computationally efficient on ECG data, rather than PPG. GitHub repositories are available online<sup>4 5</sup>.

More complex algorithms have also been investigated. In order to estimate HR during physical activities, Temko [58] studied the WFPV algorithm. The method comprised "a Wiener filter to attenuate the motion artifacts, a phase vocoder to refine the HR estimate and user-adaptive post-processing to track the subject physiology". The public database from IEEE SP Cup 2015 [59] allowed to test the model, containing data of three activity types with different intensities. Performance results showed an average absolute error (avAE) of 1.97 bpm. Also, regarding the lightest activity and comparing its avAE results to other real-time algorithms – TROIKA [59], JOSS [60], SpaMa [61], EEMD [62], IMAT [63] and MC-SMD [64] –, tge WFPV algorithm outperformed those alternatives, excepting SpaMa. When considering all activity types, WFPV obtained the lowest error. The author shared a GitHub repository containing the MATLAB implementation<sup>6</sup>.

Sharma [65] proposed the variational mode decomposition (VMD), a new technique for heart rate estimation from PPG. The concept consists of decomposing the PPG signal into a number of modes, or sub-signals, of different center frequency, energy, and bandwidth. The ones where the heart rate information influences more dominantly are then selected by Fast Fourier Transform (FFT) and processed using principal component analysis (PCA), and the heart rate is extracted applying short-time Fourier transform (STFT). The algorithm is validated over three databases: Capnobase, MIMIC, and University of Queens Vital Sign (UQVS). The root mean square error is assessed, obtaining 0.23 bpm, 0.41 bpm and 1.1 bpm, respectively. Also, this approach outperformed existing algorithms such as PSD [66], EMD [67] and EEMD-PCA [68]. There are no references to any implementation source codes.

Besides heart rate detection, respiratory rate (RR) estimation methods were investigated by Charlton et al. [69]. Generically, the first step of a RR algorithm consisted of extracting respiratory signal(s) using a feature-based technique. Three features were measured: baseline wander (BW), amplitude modulation (AM) and frequency modulation (FM). Then, RR is estimated whether by computing power spectral density of the signals using Fourier Analysis or detecting individual breathing cycles using "count-orig" methodology [70]. A final RR estimate can be computed as the average of the three aforementioned

<sup>&</sup>lt;sup>4</sup>Python Heart Rate Analysis Toolkit repository: https://www.github.com/paulvangentcom/heartrate\_analysis\_python; accessed on 18<sup>th</sup> April 2020.

<sup>&</sup>lt;sup>5</sup>Arduino Heart Rate Analysis Toolkit repository: https://www.github.com/paulvangentcom/heartrate\_analysis\_Arduino; accessed on 18<sup>th</sup> April 2020.

<sup>&</sup>lt;sup>6</sup>PPG repository: https://www.github.com/andtem2000/PPG; accessed on 18<sup>th</sup> April 2020.

features if all are within 4 bpm of each other. Performance of multiple methodologies was evaluated using PhysioNet's MIMIC II database (Version 3) [71]. The results showed that, applying the first estimation approach, using individually BW, AM and FM respiratory signals, the mean absolute error (MAE) stood at 8.18 bpm, 11.14 bpm and 12.11 bpm, respectively. However, considering the second estimation approach, the MAE values dropped to 4.28 bpm, 5.58 bpm and 7.95 bpm, respectively. Additionally, applying quality assessment and fusion step over the three respiratory signals, MAE reached 10.52 bpm and 3.36 bpm, when estimating by Fourier analysis and breath detection, respectively. A GitHub repository<sup>7</sup> containing the developed MATLAB code was provided.

Kong et al. [72] developed an heart rate tracking algorithm, TVSMART, standing for "time-varying spectral motion artifact removal technique". Besides handling PPG data acquired from wristbands or forehead devices, the method also uses accelerometer signals and comprises: a preprocessing phase using normalization and bandpass filter; time-frequency spectrum (TFS) estimation and motion artifact removal using variable-frequency complex demodulation (VFCDM); cubic spline regression for HR estimation. The algorithm was further compared to WFPV [58], because of, according to the authors, its public availability and better performance compared to most of the published algorithms. Two databases were used for validation: one from IEEE SP Cup [59] and one own dataset, Chon Lab. For slow walking data, and considering both databases, WFPV obtained an average absolute error (avAE) 4.46 bpm, while TVSMART obtained 3.53 bpm. Regarding only the IEEE SP Cup dataset, avAE values stood at 4.00 bpm and 3.68 bpm, respectively. There are no evidences on how the authors implemented in practice this algorithm.

Table 2.2 summarizes the main characteristics of the reviewed articles: the application scope, main results and supporting source code and datasets. It can be seen that every reviewed work referred a public available dataset. The most accurate results were registered by [54], obtaining a 100% correlation with a complex monitoring system. However, only [56] provided a C code for heart rate measurement, being a suitable option to the implementation.

#### Publicly available repositories

Open-source implementations have also been investigated. In the next paragraphs, GitHub repositories associated to the "PPG" keyword, and filtered by C/C++ language, are discussed. Several sensors are used, although few are provided a proper documentation.

ProtoCentral<sup>8</sup> supplies an oxygen saturation and heart rate monitoring system<sup>9</sup>, implemented in a custom device containing the Texas Instruments's AFE4490 integrated circuit<sup>10</sup> (IC). The supporting documentation addresses the Arduino connections, rather than the PPG extraction and processing algorithms. A similar IC, the AFE4404<sup>11</sup>, has been integrated with a STM32L443xx<sup>12</sup> microcontroller. The

<sup>&</sup>lt;sup>7</sup>Critical Data Book repository: https://www.github.com/MIT-LCP/critical-data-book; accessed on 18<sup>th</sup> April 2020. <sup>8</sup>ProtoCentral homepage: https://www.protocentral.com/; accessed on 30<sup>th</sup> April 2020.

<sup>&</sup>lt;sup>9</sup>AFE4490 repository: https://www.github.com/Protocentral/AFE4490\_Oximeter; accessed on 30<sup>th</sup> April 2020.

<sup>&</sup>lt;sup>10</sup>AFE4490 datasheet: https://www.ti.com/lit/ds/symlink/afe4490.pdf; accessed on 30<sup>th</sup> April 2020.

<sup>&</sup>lt;sup>11</sup>AFE4404 datasheet: https://www.ti.com/lit/ds/symlink/afe4404.pdf; accessed on 30<sup>th</sup> April 2020.

<sup>&</sup>lt;sup>12</sup>STM32L443xx datasheet: https://www.st.com/resource/en/datasheet/stm321443vc.pdf; accessed on 30<sup>th</sup> April 2020.

| Research | Purpose    | Technique                        | Results                                              | Source code     |

|----------|------------|----------------------------------|------------------------------------------------------|-----------------|

| [51]     | Pulse peak | SSF                              | PPV = 80.29%                                         | ×               |

| [52]     | ABP pulses | SSF                              | 99.31% ECG correlation                               | <b>~</b> C      |

| [54]     | HR         | Autocorrelation                  | 100% BIOPAC correlation                              | <b>X</b> C/C++  |

| [56]     | HR         | Adaptive peak detection          | RMSE = 4.18 bpm                                      | ✓ Python<br>✓ C |

| [58]     | HR         | WEPV                             | avAE = 1.97 bpm                                      | ✓ MATLAB        |

| [65]     | HR         | VMD                              | RMSE = 0.23 bpm<br>RMSE = 0.41 bpm<br>RMSE = 1.1 bpm | ×               |

| [69]     | RR         | Fourier analysis<br>"count-orig" | MAE = 10.52 bpm<br>MAE = 3.36 bpm                    | ✓ MATLAB        |

| [72]     | HR         | VFCDM                            | avAE = 3.68 bpm                                      | ×               |

| Table 2.2:      |

|-----------------|

| Overview        |

| of reviewed     |

| PPG researches. |

repository<sup>13</sup> is not paired to any documentation.

The intended sensor to be used in the implementation is the Maxim Integrated's MAX3010x, a pulse oximeter and heart-rate sensor integrated circuit series. The pulse oximeter allows the measurement of oxygen saturation in the blood. Regarded as portable, stable and reliable [73] [74], multiple documented implementations were found.

A MAX30100<sup>14</sup> version driver<sup>15</sup>, for Arduino deployment, is well documented by a tutorial available online<sup>16</sup>. The algorithm consists of a DC signal removal filter to only keep the AC component, a mean median filter to improve peak detection and a Butterworth filter to remove the higher level harmonies. Heart rate is then determined by the delay between two beats. The author performed a single measurement test and compared it with the value obtained by a blood pressure measuring device. The error obtained was 0.81 bpm. This driver has been implemented by two further open-source projects.

The first one<sup>17</sup> cites the previous tutorial, despite its implementation being targeted to the STM32F4 board<sup>18</sup>. It monitors both oxygen saturation and heart rate in real-time. Secondly, a wearable health monitor<sup>19</sup> has been developed including several sensors, namely the MAX30100 in order to perform similar measurements. This module has been programmed by the aforementioned driver. The documentation consists of a paper report.

An Arduino project featuring identical monitoring, using the MAX30102<sup>20</sup> module, is also available online<sup>21</sup>, along with a step-by-step guide<sup>22</sup>. The algorithm's source code is also extensively commented.

The previous sensor is also supported by two relevant drivers for Arduino with similar purposes. One<sup>23</sup> offers documentation on hardware and troubleshooting, but also commented examples. The latter<sup>24</sup>, dedicated to MAXREFDES117#<sup>25</sup>, a board embedding the sensor, has been developed by the same manufacturer. Support documentation regarding hardware is available on board's website.

SparkFun has also developed an Arduino library<sup>26</sup> for the MAX3010x sensor family, including example sketches. Besides monitoring presence sensing, temperature and oxygen levels, heart rate measurement is implemented by Penpheral Beat Amplitude (PBA) algorithm. The developed code is widely commented.

A wide range of C libraries dedicated to MAX3010x sensor is available. This grants multiple solutions

<sup>&</sup>lt;sup>13</sup>AFE4404 repository: https://www.github.com/opetany93/PPG-Dev2; accessed on 30<sup>th</sup> April 2020.

<sup>&</sup>lt;sup>14</sup>MAX30100 datasheet: https://www.datasheets.maximintegrated.com/en/ds/MAX30100.pdf; accessed on 7<sup>th</sup> May 2020. <sup>15</sup>MAX30100 repository: https://www.github.com/xcoder123/MAX30100; accessed on 2<sup>nd</sup> May 2020.

<sup>&</sup>lt;sup>16</sup> Implementing pulse oximeter using MAX30100: https://www.morf.lv/implementing-pulse-oximeter-using-max30100; accessed on 7<sup>th</sup> May 2020.

<sup>&</sup>lt;sup>17</sup>Pulse-Oximeter-with-MAX3010X repository: https://www.github.com/GCY/Pulse-Oximeter-with-MAX3010X; accessed on 2<sup>nd</sup> May 2020.

<sup>&</sup>lt;sup>18</sup>STM32F4 series webpage: https://www.st.com/en/microcontrollers-microprocessors/stm32f4-series.html; accessed on 7<sup>th</sup> May 2020.

<sup>&</sup>lt;sup>19</sup>MAX30100 repository (2): https://www.github.com/Joe-Story/GM2-Wearable-Healthcare; accessed on 2<sup>nd</sup> May 2020.

<sup>&</sup>lt;sup>20</sup>MAX30102 datasheet: https://www.datasheets.maximintegrated.com/en/ds/MAX30102.pdf; accessed on 2<sup>nd</sup> May 2020.

<sup>21</sup>MAX30102 repository: https://www.github.com/aromring/MAX30102\_by\_RF; accessed on 2<sup>nd</sup> May 2020.

<sup>&</sup>lt;sup>22</sup>Pulse Oximeter With Much Improved Precision: https://www.instructables.com/id/ Pulse-Oximeter-With-Much-Improved-Precision/; accessed on 2<sup>nd</sup> May 2020.

<sup>&</sup>lt;sup>23</sup>MAX30102 repository (2): https://www.github.com/catnull/Max30102Driver-For-Arduino; accessed on 12<sup>th</sup> May 2020.

<sup>24</sup>MAXREFDES117# repository: https://www.github.com/MaximIntegratedRefDesTeam/RD117\_ARDUINO; accessed on 2<sup>nd</sup> May 2020.

<sup>&</sup>lt;sup>25</sup>MAXREFDES117# website: https://www.maximintegrated.com/en/design/reference-design-center/system-board/ 6300.html/; accessed on 12<sup>th</sup> May 2020.

<sup>&</sup>lt;sup>26</sup>MAX3010x repository: https://www.github.com/sparkfun/SparkFun\_MAX3010x\_Sensor\_Library; accessed on 2<sup>nd</sup> May 2020.

to program the FPGA and to be run by accelerators. However, the reviewed repositories did not evaluate exhaustively the measurement accuracy achieved by the implemented algorithm. The repository referred in footnote 21 provides a clearer support documentation. The applied algorithm is consistent with the one presented in [54], not supported by an open-source implementation, as both base on autocorrelation peak detection. Therefore, this implementation is the most appropriate to be executed.

# 2.3 FPGA-based medical devices

Considering the targeted platform of this work, the following paragraphs review existing medical prototypes also based on FPGA logic.

Joaquinito [75] developed a wireless biosignal measurement system, using a SoC FPGA, for monitoring heart rate from ECG signal analysis, and temperature in real-time. The system included a Bluetooth Low Energy (BLE) device to transfer processed data with low-power consumption and low data rate connection, paired to a smartphone. The approach consisted of connecting both analog and digital sensors to the SoC, accelerating the processing of ECG signals recorded by three electrodes and sending short but relevant data via BLE to the user interface (the smartphone). ECG processing based on Pan–Tompkins algorithm, where the preprocessing phase composed by amplification and filtering shares some similarities with EEG. Using this method, ECG signal peaks were detected and a hardware module performed further operations to obtain heart rate. The testing results showed 100% sensitivity – that is, the system detected all ECG signal peaks – and an average of 99.7% positive predictability – meaning that 0.3% of the predictions were incorrectly classified as ECG peaks, corresponding to noise signals. The methodology of using custom hardware and accelerating signal processing improved the system performance. The goals of this work are very similar to the proposed ones in this report. Both systems aim to monitor vital signs in real-time and to process them using SoC FPGA, differing in the biometric techniques.

Knežević et al. [76] presented a methodology to detect ECG peaks and the points of maximum slope of PPG. The delay between them is also computed, and is known as pulse transit time (PPT). The system was demonstrated in a FPGA. Both signals passed through a DWT module. Then, resulting ECG signal was processed by modulus maxima, and PPG signal by derivative filtering. The hardware design comprised an Analog-Digital Converter (ADC), two processing cores for ECG and PPG, a PPT calculation circuit followed by an Universal Asynchronous Receiver/Transmitter (UART) controller. All digital modules were specified in VHSIC Hardware Description Language (VHDL) code. The processing cores were tested using two public databases, containing recorded pulses. ECG peaks were detected with an average accuracy of 97.5%. Regarding the PPG, the detection of points of maximum slope had an average accuracy of 97.1%. The contribution of this work is the development of dedicated hardware to process biometric signals. This was achieved by two parallel processing cores with reconfigurable logic. There were no mentions of software modules, so this work is a reference to bio-signal processing by custom logic accelerators.

FPGA-based works aiming at emotion identification from EEG signals are emerging in the literature.

Fang et al. [77] implemented a Convolutional Neural Network (CNN) in a Virtex-7 FPGA for emotion detection from EEG signals from 6 channels. The classifier was integrated in a complete system containing an acquisition headset and a MATLAB program for feature extraction. Two experiments were conducted, one in real-time and a second one offline using the DEAP dataset. During the real-time experiment, the system took 450 ms to detect an emotion, from the acquisition node. The offline processing of DEAP dataset resulted in a valence-arousal classification accuracy of 76.67%.

The system proposed in [77] contributes with a complete execution of the classification process. However, the system is oriented to operate in a laboratory environment, rather than targeting a wearable device for daily use. Actually, this is a gap in the literature of emotion recognition, and represents an opportunity to develop a novel FPGA-based system with this scope.

# **Chapter 3**

# Proposed biometric system

This chapter provides a complete description of the algorithms for processing PPG and EEG data, to be implemented on the proposed system. The analysis includes a profiling of those algorithms, to be used when dimensioning the final system. The selection of reference datasets containing samples of bio-signals is also addressed. Sections 3.1 and 3.2 introduce, respectively, the heart rate calculator and the emotion classifier. A high-level architecture of the proposed system is presented in Section 3.3.

# 3.1 Heart rate calculator using PPG

The sub-system for computing instant heart rates using the PPG technique is proposed in this section. It is intended to acquire the raw PPG signals and to process them in the node. The selection of the algorithm for handling PPG signals is described in Section 3.1.1. The working principle of the selected algorithm to calculate heart rate is detailed in Section 3.1.2, step by step. Section 3.1.3 analyses the effects of sampling frequency and sampling time on the computational cost of the algorithm.

# 3.1.1 Selection of the algorithm and reference datasets

The main purpose of the algorithm for processing PPG data is to compute instant heart rate values in real-time. A common approach is peak detection, from which the signal periodicity, and thus the pulse, can be retrieved. From literature analysis of Table 2.2 in Section 2.2.2 was selected the proposal by [56]. This proposal provided an open-source software implementation. From the analysis of the publicly available repositories, the footnote 21 was pointed as a good candidate to be implemented in this system. In fact, this repository provided a C implementation of the algorithm, a file containing samples of raw PPG signals and a complete supporting documentation. The proposal [56], by the time of analysis, required code modifications to return instant heart rate as desired, although being written in C language. The footnote 21 alternative turned to be a more practical implementation to be divided into blocks and adapted into a hybrid HW/SW design. Moreover, the code was exhaustively commented. Thus, this ready-to-use solution was the most preferable. Next section describes the operating principle of the selected algorithm.

The provision of datasets was an exclusion factor on algorithm selection. In fact, few solutions provided data to test their implementations. The repository of Footnote 21 included a single file containing 100 samples of red and infra-red channels data, sampled at 25 Hz. Given this scenario, it is reasonable to select external datasets to validate the final design solution of heart rate module. The search for data obtained by MAX30100 sensor did not return meaningful results. Then, some PPG datasets were found, regardless the sensor used. However, none of them consisted of raw data, but preprocessed. For instance, the 2015 IEEE SP Cup dataset provided recorded PPG data of eight subjects performing different activities, such as walking and running. This database can be used to validate the design of the core responsible for handling PPG signals, described in Chapter 4. Due to the lack of raw PPG data, custom signals were recorded using a MAX30100 sensor connected to an Arduino. Additional datasets were synthesized from the real ones applying multiple transformations on a specific segment, such as multiplication by a scalar and upsampling or downsampling. Analysing signals with different amplitudes and frequencies is necessary to define the variable's size in software and the signal's wordlength in hardware.

# 3.1.2 Algorithm description

The heart rate calculator algorithm operates over two channels of PPG signal, the red (RED) and the infra-red (IR), probed by distinct LEDs. The algorithm comprises two main stages: preprocessing and periodicity search. The computational operations included in the first one are the following:

- 1. DC mean calculation: a loop over a buffer containing *N* signal samples computes the sum of their values, and then the average by dividing the accumulated sum by *N*;

- 2. DC mean subtraction: the computed average is subtracted from each channel sample, by an iterative loop;

- 3. linear regression calculation: a dot product between the sample set and corresponding shifted sample indexes is computed, then divided by a constant;

- 4. linear regression subtraction: the computed value is multiplied by each shifted sample indexes and subtracted from each channel sample;

- 5. mean square calculation: the sum square of all sample values is calculated and divided by N;

- 6. Pearson correlation calculation: a dot product between both channels' samples is determined and then divided by *N*.

Once these tasks are concluded, the periodicity search over the preprocessed signal begins. This stage is mainly performed by a function called autocorrelation.

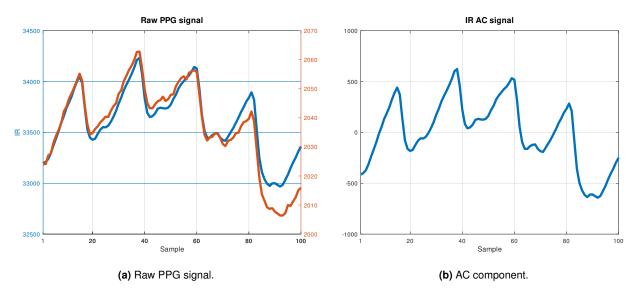

For a clearer explanation and better understanding, the steps involved in the heart rate calculation algorithm are next detailed and supported by an example. The example is a 100-sample buffer, provided by the author of the implementation, that corresponds to a good quality signal. Two-channel data, RED and IR, was sampled with 25 Hz using MAX30102 sensor, and is illustrated in Figure 3.1a. Next, the processing tasks that modify the raw input data are explained, focusing on the IR channel, from which the heart rate is computed.

The first step is to remove the DC component from the signal, keeping only the AC, because this method concentrates on the signal fluctuations, rather than its amplitude. As shown in Section 2.2, heart rate can be identified analysing AC component. The result depicts on Figure 3.1b.

Figure 3.1: Step 1 – AC component of the PPG signal.

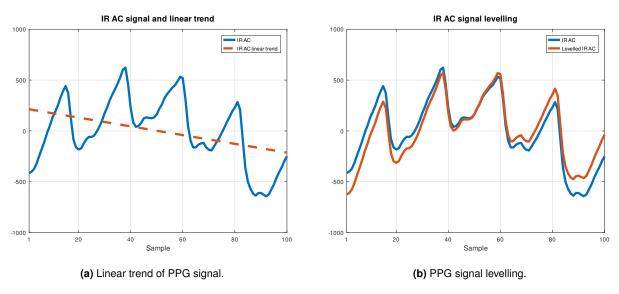

The second step consists of subtracting the first-order component, that is, the linear trend of the signal. The value of the slope  $\beta$  is obtained using Equation 3.1,

$$\beta = \frac{\sum_{t=-t_{mean}}^{t_{mean}} t \cdot y_t}{\sum_{t=-t_{mean}}^{t_{mean}} t^2}$$

(3.1)

where t is the sample index and  $y_t$  the sample value. It is worth to notice that indexes start at  $t = -t_{mean}$ , rather than at origin t = 0. This left shift by  $t_{mean}$ , defined by Equation 3.2, allows to center and equidistantly display all N samples, so that, in this example, their indexes range  $\{-49.5, -48.5, ..., 49.5\}$ , instead of  $\{0, 1, ..., 99\}$ .

$$t_{mean} = \frac{N-1}{2} \tag{3.2}$$

Figure 3.2a clarifies this centring procedure, plotting the linear trend with the computed slope of the sample set, over the AC signal. Figure 3.2b includes the levelled signal – after removing first-order component – and the original one for comparison. This levelling process is useful in further steps to detect peaks correctly.