## Unum Type-IV: A Floating-Point Unit with Dynamically Varying Exponent and Mantissa Sizes

### Micaela Moraes Serôdio

Thesis to obtain the Master of Science Degree in

### **Electrical and Computer Engineering**

Supervisor: Prof. José João Henriques Teixeira de Sousa Supervisor: Prof. Horácio Cláudio de Campos Neto

### **Examination Committee**

Chairperson: Prof. Francisco André Corrêa Alegria Supervisor: Prof. José João Henriques Teixeira de Sousa Member of the Committee: Prof. Mário Pereira Véstias

September 2021

ii

### Declaration

I declare that this document is an original work of my own authorship and that it fulfils all the requirements of the Code od Conduct and Good Practices of the Universidade de Lisboa.

#### Acknowledgments

This document marks the end of my 5-year journey as a university student and, I would like to start by thanking the Instituto Superior Técnico and the Federal University of Santa Catarina. These two universities gave me the necessary knowledge, material and conditions to develop this project, allowing me to conclude my academic career with success. I would also like to thank all my colleagues and teachers who made this whole journey stimulating and with a lot of personal, academic and social learning. In particular, I would like to thank Professor José Teixeira de Sousa for his knowledge, advice, for reviewing my thesis and also for creating in me a great interest in computer electronics and hardware, to Professor Horácio Neto for the valuable insights and, also, to João Dias Lopes for all the help in the development of this dissertation.

Finally, I would like to give special thanks to my family and friends for all the support and help they gave me throughout this process. This achievement would not be possible without their support.

#### Abstract

The main objective of this dissertation is to create a new floating-point format, called Unum-IV, that replaces the unary numeral system used in the Regime bits of the Unum Type-III format, aka *Posit* numbers, with a regular binary system. The Unum formats (types I, II and III) introduced the concept of tapered precision: numbers having an absolute value close to 1 are given more significand bits and fewer exponent bits. This way, it is possible to extraordinarily increase the dynamic range or accuracy, depending on the application.

The new format recovers and extends Unum Type-I ideas but, like Unum-III, it is meant to be hardware fiendly, is hence named Unum Type-IV. The main ideas of the new Unum-IV format are to use a dynamically variably-sized significand and exponent with a 1's complement representation of the exponent, and a 2's complement representation of the significand. The Unum-IV format uses one hidden bit both in the exponent and significand representations to prevent redundancy. However, unlike other formats, including Posits, that use a fixed hidden 1 bit only in the significand, Unum-IV uses dynamic but simply computed hidden bits for both the significand and the exponent.

This proposal intends to be a suitable drop-in replacement for the IEEE 754 Floating-Point Standard, using a dynamically sized significand and exponent, which allows the new format to fulfil the precision or dynamic range needs of applications, using fewer hardware resources. This format is aimed at small memory footprint and low energy consumption applications, such as those that can be found in the Internet of Things (IoT). In fact, in most practical cases, Unum-IV can replace IEEE 754 double precision numbers, which means half the memory footprint and 30% less hardware resources.

In this dissertation work, a Unum-IV Floating-Point Unit (FPU) with addition, subtraction, multiplication and division operations is implemented in software and hardware, in the C and Verilog languages, respectively. To study it, the FPU is attached as a peripheral to an open-source RISC-V processor, and the K-Nearest Neighbours (KNN) algorithm, a non-parametric machine learning algorithm, is used as a proof of concept for comparing the Unum-IV and the IEEE Standard 754 Floating-Point formats. The metrics used to compare the different number systems are the precision, dynamic range, resolution, Units of Least Precision (ULP), and integrated circuit implementation results: silicon area, power consumption, operation clock frequency. The percentage of accurate classifications in the KNN application, using the IEEE-754 64-bit double precision floats as reference, is also studied.

**Keywords:** Computer Arithmetic, Unum Number, Posits, Floating-Point Unit, High Precision Arithmetic, Approximate Computing

#### Resumo

O objetivo principal desta dissertação é a criação de um novo formato de vírgula flutuante, o Unum-IV, que substitui o sistema numérico unário utilizado nos bits de regime do formato Unum Type-III, também conhecido como Posits, com um sistema binário regular. Os formatos Unum (tipos I, II e III) introduziram o conceito de precisão cónica, isto é, números com um valor absoluto próximo de 1 recebem mais bits de mantissa e menos bits de expoente. Desta forma, é possível aumentar extraordinariamente a gama dinâmica e/ou precisão, dependendo do contexto em que é usado.

O novo formato recupera e estende ideias do formato Unum-I. No entanto, tal como o formato Unum-III, este novo formato Unum-IV é voltado para versão otimizada de termos da utilização de hardware. As principais ideias deste novo formato são a utilização de um significand e expoente de tamanho dinamicamente varíavel com uma representação de complemento para 1 do expoente, e uma representação de complemento para 1 do significando. O formato Unum-IV contém um bit "escondido" nas representações de expoente e significando para não existir redundância nas representações. No entanto, contrariamente aos restantes formatos, incluindo os Posits, que usam um bit implícito fixo a 1 apenas no significando, o Unum-IV utiliza bits implícitos de forma dinâmica mas simples de calcular tanto para o expoente como para o significando.

Esta proposta pretende ser um substítuto adequado para o Padrão de Vírugla Flutuante IEEE 754, através de um significando e exponente de tamanho dinâmico, o que permite que o novo formato cumora as necessidades de gama dinâmica ou precisão das aplicações, utilzando menos recursos de hardware. O Unum-IV é um formato voltado para aplicações de baixo consumo energético e baixa utilização de memória, como IoT. Na verdade, na maioria dos casos práticos, o Unum-IV pode substituir os números IEEE 754 de precisão dupla, o que se traduz numa redução de memória utilizada, bem como uma redução 30% dos recursos de hardware.

Nesta dissertação, foi implementada em software e hardware uma Unidade de Ponto Flutuante (UPF) com adição, subtração, multiplicação e divisão de números no formato Unum-IV em C e Verilog, respectivamente. Esta UPF foi anexada como periférico a um processador RISC-V de código aberto e um algoritmo de classificação não paramétrico (KNN) foi utilizado como prova de conceito para comparar os resultados das operações com Unum-IV e com IEEE 754 Standard. As métricas usadas para comparar os diferentes sistemas numéricos são a precisão, gama dinâmica, resolução, ULP ("Units of Least Precision"), resultados de implementação ASIC, como a área ocupada, consumo energético e frequência do relógio. Os resultados obtidos com os dois modelos na aplicação KNN são comparados em termos da percentagem de classificações corretas, sendo que a referência é dada pelo formato de 64 bits IEEE 754.

**Palavras-chave:** Aritmética Computacional, Computação Unum, Unidade de Ponto Flutuante, Aritmética de Alta Precisão

## Contents

|   | Ackr  | nowledgments                                                | v    |

|---|-------|-------------------------------------------------------------|------|

|   | Abst  | tract                                                       | vii  |

|   | Res   | umo                                                         | ix   |

|   | List  | of Tables                                                   | xiii |

|   | Listi | ngs                                                         | xiv  |

|   | List  | of Figures                                                  | xv   |

|   | List  | of Acronyms                                                 | xix  |

|   |       |                                                             |      |

| 1 |       | oduction                                                    | 1    |

|   | 1.1   |                                                             | 1    |

|   | 1.2   |                                                             |      |

|   | 1.3   | Objectives                                                  | 3    |

|   | 1.4   | Dissertation Outline                                        | 3    |

| 2 | Вас   | kground                                                     | 5    |

|   |       | EEE Standard 754 Floating-Point                             | 5    |

|   |       | 2.1.1 Single-Precision                                      | 5    |

|   |       | 2.1.2 Other IEEE 754 Standard Formats and "Bfloat16" Format | 7    |

|   | 2.2   | Unum                                                        | 8    |

|   |       | 2.2.1 Unum Type-I                                           | 8    |

|   |       | 2.2.2 Unum Type-II                                          | 9    |

|   |       | 2.2.3 Unum Type-III: Posits                                 | 9    |

|   |       |                                                             |      |

| 3 | Unu   | ım Type-IV                                                  | 13   |

|   | 3.1   | Unum Type-IV Generic Format                                 | 13   |

|   | 3.2   | Field Extractions                                           | 16   |

|   |       | 3.2.1 Exponent Extraction                                   | 16   |

|   |       | 3.2.2 Significand Extraction                                | 17   |

|   |       | 3.2.3 Examples                                              | 17   |

|   | 3.3   | Features                                                    | 18   |

|   |       | 3.3.1 Special Cases                                         | 18   |

|   |       | 3.3.2 Exceptions                                            | 18   |

|   |      | 3.3.3    | Rounding                                                 | 18 |  |

|---|------|----------|----------------------------------------------------------|----|--|

|   |      | 3.3.4    | Dynamic Range and Precision                              | 19 |  |

|   | 3.4  | Examples |                                                          |    |  |

|   |      | 3.4.1    | Unum-IV to Decimal Conversion                            | 22 |  |

|   |      | 3.4.2    | Unum-IV<4,1> Enconding $\ldots$                          | 24 |  |

| 4 | Hare | dware I  | mplementation                                            | 25 |  |

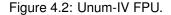

|   | 4.1  | Unum     | Type-IV Floating-Point Unit                              | 26 |  |

|   | 4.2  | Functi   | onal Units                                               | 28 |  |

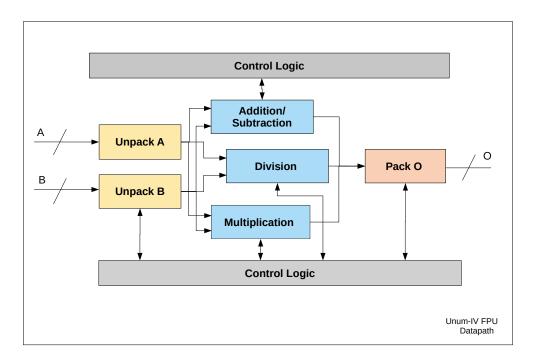

|   |      | 4.2.1    | Unpack Unit                                              | 28 |  |

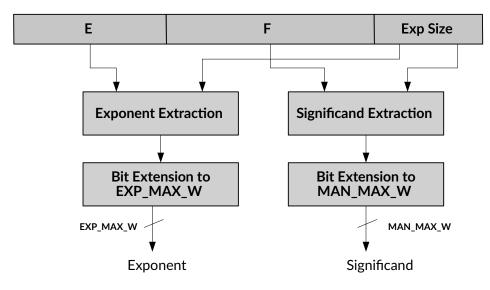

|   |      | 4.2.2    | Processing Units                                         | 30 |  |

|   |      | 4.2.3    | Pack Unit                                                | 35 |  |

|   |      | 4.2.4    | Auxiliary Components                                     | 38 |  |

|   |      | 4.2.5    | Functional Units Pipeline Stages                         | 40 |  |

| 5 | Eva  | luating  | and Comparing Unum Type-IV to Other Formats              | 41 |  |

|   | 5.1  | Comp     | arison Metrics                                           | 41 |  |

|   |      | 5.1.1    | Precision Bits                                           | 41 |  |

|   |      | 5.1.2    | Dynamic Range                                            | 42 |  |

|   |      | 5.1.3    | Hardware Resources                                       | 42 |  |

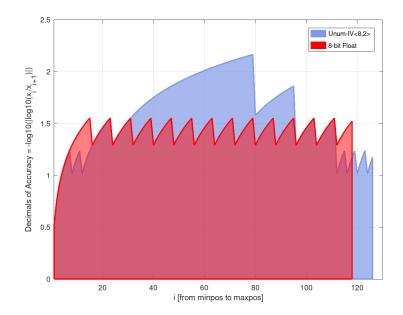

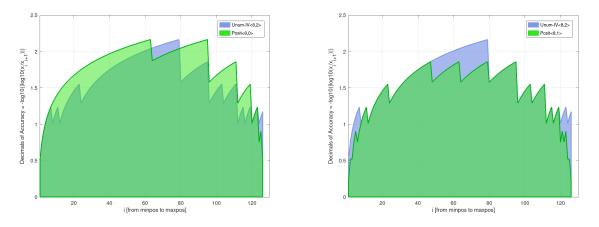

|   |      | 5.1.4    | Decimals of Accuracy                                     | 42 |  |

|   |      | 5.1.5    | Units of Least Precision                                 | 42 |  |

|   | 5.2  | Comp     | aring Unum Type-IV Features with Other Formats           | 43 |  |

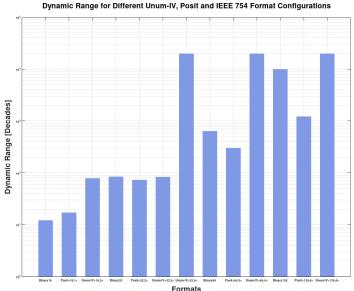

|   | 5.3  | Comp     | aring Unum Type-IV Dynamic Range with Other Formats      | 45 |  |

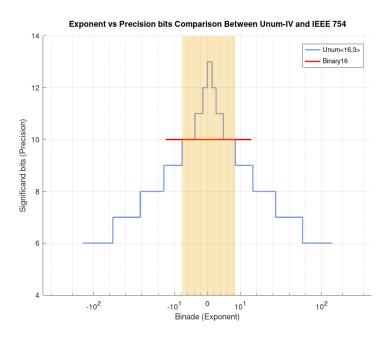

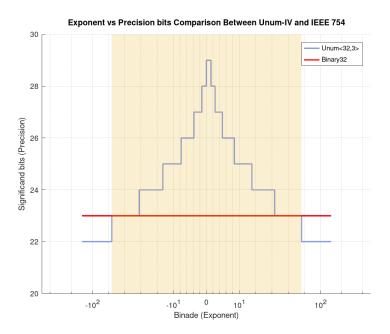

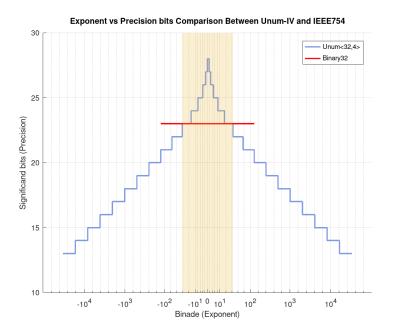

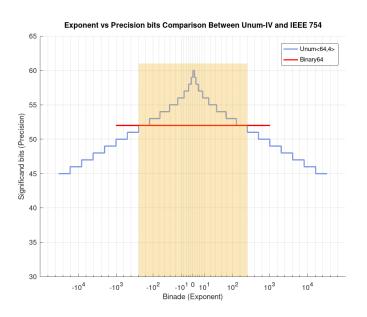

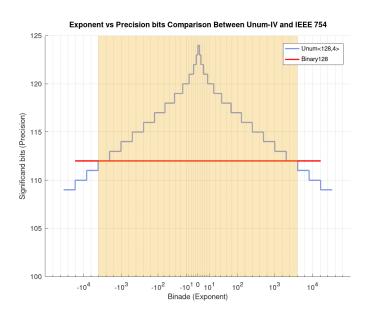

|   | 5.4  | Comp     | aring Unum Type-IV Precision with Other Formats          | 46 |  |

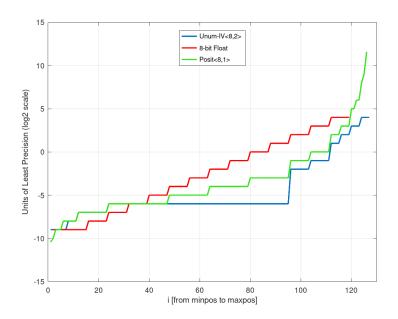

|   |      | 5.4.1    | Unum-IV<8,2> vs. Quarter-Precision IEEE-Style floats     | 49 |  |

|   |      | 5.4.2    | Unum-IV<8,2> vs. Posit<8,1> vs. Posit<8,0>               | 51 |  |

|   | 5.5  | Comp     | aring Unum Type-IV Hardware Resources with Other Formats | 52 |  |

|   |      | 5.5.1    | IEEE 754 and Unum Type-IV Comparison                     | 52 |  |

|   |      | 5.5.2    | Posits and Unum Type-IV Comparison                       | 55 |  |

|   | 5.6  | Comp     | arison Summary                                           | 56 |  |

| 6 | Pro  | of of Co | oncept: KNN Application                                  | 58 |  |

|   | 6.1  | Algorit  | thm                                                      | 59 |  |

|   | 6.2  | Impler   | nentation                                                | 60 |  |

|   | 6.3  | Exper    | imental Results                                          | 64 |  |

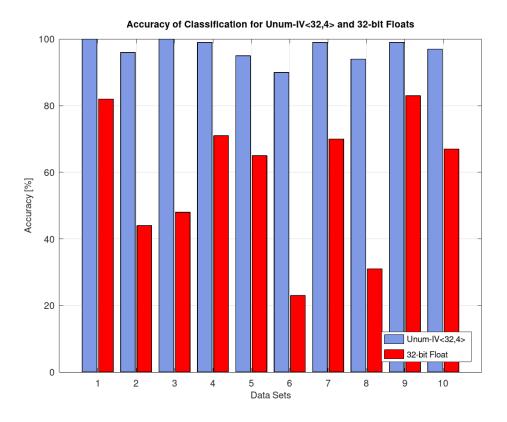

|   |      | 6.3.1    | Experiment 1                                             | 64 |  |

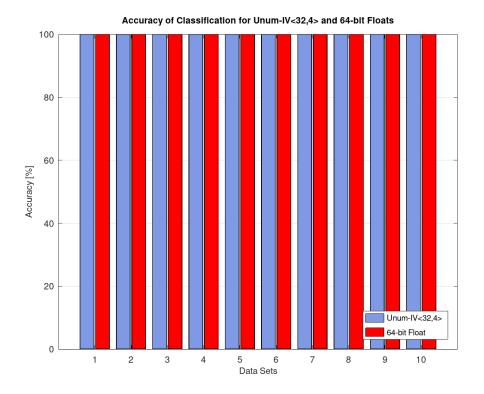

|   |      | 6.3.2    | Experiment 2                                             | 65 |  |

| 7  | Con   | clusions     | 67 |

|----|-------|--------------|----|

|    | 7.1   | Achievements | 68 |

|    | 7.2   | Future Work  | 69 |

| Bi | bliog | raphy        | 71 |

# **List of Tables**

| 2.1 | IEEE 754 Standard and "Bfloat16" Format Features.                            | 8  |

|-----|------------------------------------------------------------------------------|----|

| 3.1 | Exponent and Significand Extraction for DATA_W=32 and EXP_SZ_W=4             | 18 |

| 3.2 | "Round to the nearest, ties even" Mode                                       | 19 |

| 3.3 | Unum Type-IV Dynamic Ranges                                                  | 20 |

| 3.4 | Unum Type IV Precision                                                       | 21 |

| 3.5 | Unum-IV<4,1>                                                                 | 24 |

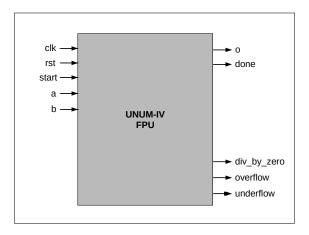

| 4.1 | FPU Interface.                                                               | 27 |

| 4.2 | Specification for the Operation Selection.                                   | 30 |

| 4.3 | Functional Units Pipeline Stages                                             | 40 |

| 5.1 | Qualitative Comparison Between IEEE 754 Standard and Unum Type-IV.           | 43 |

| 5.2 | Resolution for Different Unum-IV, Posits and IEEE754 Format Configurations   | 49 |

| 5.3 | ASIC Implementation Results.                                                 | 53 |

| 5.4 | Silicon Area of the Different Modules using Unum-IV<32,4>                    | 54 |

| 5.5 | FPGA Results Comparison Between Different Unum-IV and Posits Configurations  | 55 |

| 5.6 | Silicon Area Comparisons Between Different Unum-IV and Posits Configurations | 55 |

| 5.7 | Binary32, Bfloat16, Posit<16,3> and Unum-IV<16,3> Comparisons.               | 56 |

| 6.1 | Parameters used in the KNN Clustering Application.                           | 64 |

# Listings

| 3.1 | Pseudo-code of the Exponent Extraction Algorithm.                           | 17 |

|-----|-----------------------------------------------------------------------------|----|

| 3.2 | Pseudo-code of the Significand Extraction Algorithm.                        | 17 |

| 4.1 | Verilog Code to Instantiate the Parameterizable Unum-IV Floating Point Unit | 27 |

| 4.2 | Rounding Bits Assignment.                                                   | 37 |

| 6.1 | Unum-IV and KNN Header File                                                 | 60 |

| 6.2 | Double Random Generator.                                                    | 62 |

| 6.3 | Data Structures.                                                            | 62 |

| 6.4 | Square Distance Functions.                                                  | 63 |

| 6.5 | Insertion in Ordered List.                                                  | 63 |

| 6.6 | Classification step code.                                                   | 64 |

# **List of Figures**

| 2.1 | IEEE 754 Single-Precision Representation Format.                                        | 5  |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.2 | Unum Type-I Representation Format                                                       | 8  |

| 2.3 | Visual Representation of the Unum Type-II Projective Real Number Line [15]              | 10 |

| 2.4 | Unum Type-III Representation Format.                                                    | 10 |

| 2.5 | Unum Type-I,II and III Advantages and Disadvantages                                     | 11 |

| 3.1 | Generic Unum-IV Representation Format.                                                  | 14 |

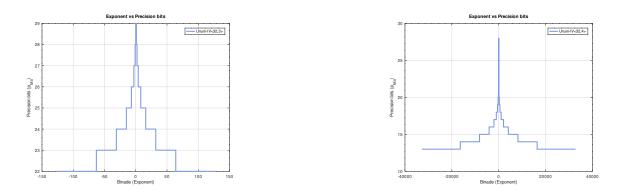

| 3.2 | Unum-IV<16,2> and Unum-IV<16,3> Precision Bits vs Binade (Exponent). $\ldots$           | 21 |

| 3.3 | Unum-IV<32,3> and Unum-IV<32,4> Precision Bits vs Binade (Exponent). $\ldots$           | 21 |

| 3.4 | Example 1 of an Unum-IV<32,4> Bit String.                                               | 23 |

| 3.5 | Example 2 of an Unum-IV<32,4> Bit String.                                               | 23 |

| 3.6 | Example 3 of an Unum-IV<32,4> Bit String                                                | 23 |

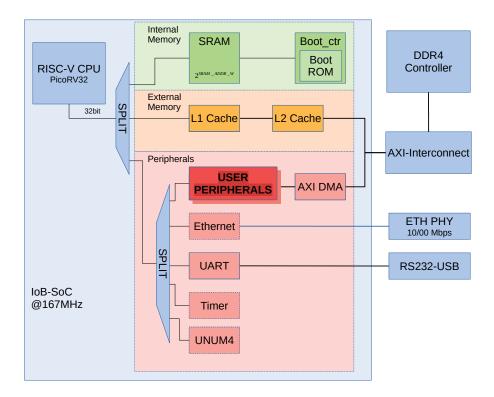

| 4.1 | IoB-SoC Block Diagram with the Unum-IV Module Attached as a Peripheral                  | 25 |

| 4.2 | Unum-IV FPU.                                                                            | 26 |

| 4.3 | Unum-IV FPU Datapath                                                                    | 28 |

| 4.4 | Unum-IV Unpack Stage Block Diagram.                                                     | 29 |

| 4.5 | Unum-IV Addition/Subtraction Unit                                                       | 31 |

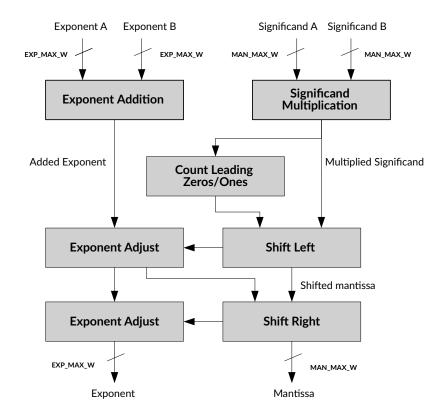

| 4.6 | Unum-IV Multiplication Unit                                                             | 33 |

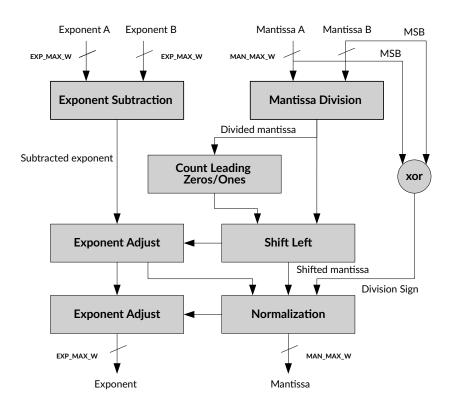

| 4.7 | Unum-IV Division Unit                                                                   | 34 |

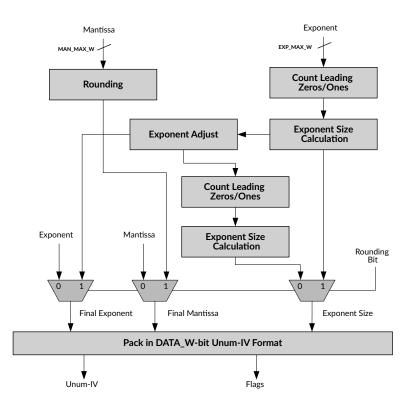

| 4.8 | Unum-IV Pack Unit.                                                                      | 36 |

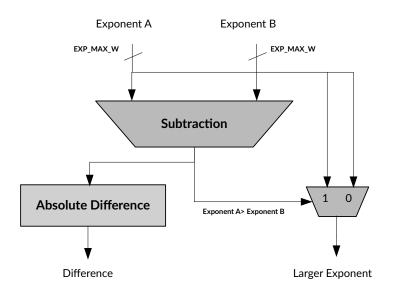

| 4.9 | Unum-IV Exponent Difference Flow Diagram.                                               | 38 |

| 5.1 | Dynamic Range for Different Unum-IV and IEEE754 Format Configurations                   | 45 |

| 5.2 | Exponent vs Significand Bits Comparison Between Unum-IV<16,3> & 16-bit IEEE 754         |    |

|     | Format.                                                                                 | 46 |

| 5.3 | Exponent vs Significand Bits Comparison Between Unum-IV<32,3> & 32-bit IEEE 754         |    |

|     | Format.                                                                                 | 47 |

| 5.4 | Exponent vs Significand Bits Comparison Between Unum-IV $<32,4>$ & 32-bit IEEE 754      |    |

|     | Format.                                                                                 | 47 |

| 5.5 | Exponent vs Significand Bits Comparison Between Unum-IV $< 64, 4 > \& 64$ -bit IEEE 754 |    |

|     | Format.                                                                                 | 48 |

| 5.6 | Exponent vs Significand Bits Comparison Between Unum-IV<128,4> & 128-bit IEEE 754 |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | Format.                                                                           | 48 |

| 5.7 | Decimals of Accuracy Comparison Between Unum-IV < 8,2 > & 8-bit Floats            | 50 |

| 5.8 | Decimals of Accuracy Comparison Between Unum-IV<8,2> & Posit<8,0> (LEFT).Decimals |    |

|     | of Accuracy Comparison Between Unum-IV<8,2> & Posit<8,1> (RIGHT). $\ldots$        | 51 |

| 5.9 | ULP Comparison Between Unum-IV<8,2> & 8-bit Floats                                | 52 |

| 6.1 | KNN Application.                                                                  | 59 |

| 6.2 | Accuracy of Classification for Unum-IV<32,4> and 32-bit Floats                    | 65 |

| 6.3 | Accuracy of Classification for Unum-IV < 32,4 > and 64-bit Floats                 | 66 |

|     |                                                                                   |    |

# **List of Acronyms**

| FPU Floating-Point Unit                                       |

|---------------------------------------------------------------|

| FPGA Filed Programmable Gate Array                            |

| <b>RISC</b> Reduced Instruction Set Computer                  |

| SoC System on Chip                                            |

| FU Functional Unit                                            |

| ALU Arithmetic and Logic Unit                                 |

| FP Floating Point                                             |

| SP Single Precision                                           |

| <b>DP</b> Double Precision                                    |

| NaN Not a Number                                              |

| AI Artificial Intelligence                                    |

| ML Machine Lerning                                            |

| IoT Internet of Things                                        |

| qNaN Quiet Not a Number                                       |

| sNaN signaling Not a Number                                   |

| HPC High Performace Computing                                 |

| BD Big Data                                                   |

| MSB Most Significant Bit                                      |

| <b>IEEE</b> Institute of Electrical and Electronics Engineers |

| DL Deep Learning                                              |

| ASIC Application-Specific Integrated Circuit                  |

| ULP Units of Least Precision                                  |

## **Chapter 1**

## Introduction

#### 1.1 Topic Overview

We live in an era where the trade-off between performance, cost, resources, and power consumption significantly impacts the computer science area. The increase in the complexity of the algorithms due to Big Data (BD) analysis, the need for High-Performance Computing (HPC) and the never-ending need for energy-efficient computing in fields of Machine Learning (ML), Artificial Intelligence (AI) and the Internet of Things (IoT) are creating a new computing paradigm. The majority of numerical computation algorithms require the capacity to perform arithmetic operations and manipulation of real numbers. In digital electronics, the most extensively adopted approximation of the real numbers is given by the floating-point formats.

Throughout our history, some disasters happened due to floating-point issues, usually because of rounding errors [1], such as the Patriot Missile Failure on February 25, 1991, where an Americal Patriot Missile battery in Dharan, Suadi Arabia failed to intercept an incoming Iraqi Scud missile. That happened due to a rounding error in the time calculation, which costed the life of 38 people.

Another disaster was the explosion of the Ariana-5 rocket launched by the European Space Agency in 1996. The rocket exploded just forty seconds after the lift-off due to a software error in the inertial reference system. One more example of a floating-point error disaster was the Sleipner Oil Platform that collapsed to the ocean floor due to a floating-point error in the structural analysis, costing a nearly 1 billion dollar loss. There were other famous disasters in different areas caused by issues of the floatingpoint format design, like the overflow, underflow and rounding error problems [2].

During the 1960s and the 1970s, there was no ubiquity in the floating-point format, so each computer manufacture developed its floating-point system, resulting in floating-point inconsistency across platforms. In 1985, the IEEE Standard for Floating-point Arithmetic (IEEE 754) [3] was established by the Institute of Electrical and Electronics Engineers (IEEE), and it is, nowadays, the most common representation of real numbers on computers, including Intel-based PC's, Macs and most Unix platforms. This format has been reviewed and replaced two times, in 2008 [4] and 2019 [5] but there were only minor changes between them to maintain compatibility in existing implementations. However, some drawbacks have been identified in the IEEE 754 Standard [6, 7, 8], such as:

- Overflow and Underflow: overflowing to  $-\infty$  or  $+\infty$  and underflowing to 0, increases the relative error by an infinite factor and leads to sign information loss, respectively.

- No Gradual Overflow and Fixed-Accuracy: accuracy is flat across a vast range, then "falls off a cliff".

- Wasted bit-patterns: there are too many NaN representations and two bit-patterns to represent 0, the "negative zero" (0<sup>-</sup>) and the "positive zero" (0<sup>+</sup>).

- There is no guarantee of identical results across systems.

- · Exponents usually take too many bits.

- Equality verification test between two floating-point is complex due to the presence of redundant representations.

Throughout the years, different number systems and techniques have been proposed to overcome these challenges. In [9], Morris suggested a "tapered" system to solve the fixed accuracy problem of the floating-points [10].

In 2013, John L. Gustafson introduced a new binary and arithmetic way of representing real numbers, a number system called "Universal Numbers" [6, 11, 12, 13]. They have so far three different types of representation. Type-I is a super-set of the IEEE 754 Standard floating-point format, and it was introduced in [6]. This format uses a variable-length storage format for the exponent and fraction fields and a "u-bit" at the end of the fraction that indicates if a "real" number (u=0) is an exact float or lies in the open interval between two consecutive exact (u=1). The Type -II [14] enables a clean mathematical design based on the *projective reals* and relies on lookup tables. It is a direct map of signed integers to the projective real number line. The last version introduced in 2017 is the Type-III format, also known as Posits [15, 16]. Posits are a hardware-friendly version of Unums [17, 18], with all the advantages from the previous types, but where the problems found in Type-I due to the variable sizes are solved. Posits have a different format than IEEE 754 floats, consisting of 4 fields: the sign, regime, exponent, and fraction field.

Recent studies on Posits suggest it solves many of the drawbacks of the IEEE 754 Standard for floating-point arithmetic [8, 19, 20, 21], and are especially useful for Deep Learning (DL) applications [22, 23, 24].

Over the years, other notable formats have been introduced for DL algorithms [25, 26], for example, the "Bfloat16" format [27, 28, 29, 30] introduced by a Google research group to replace the 32-bit IEEE 754 floating-point format in energy-efficient applications.

#### 1.2 Motivation

Nowadays, even though many shortcomings have been pointed out upon the IEEE 754 Standard, it is still the most commonly implemented in microcontrollers and general-purpose microprocessors to

perform floating-point arithmetic. However, the trade-off between the dynamic range and the precision of the floating-point formats can be explored to create a new number system that avoids those short-comings. The Unum system introduced the concept of tapered precision, which means that numbers having an absolute value close to 1 are given more mantissa bits and fewer exponent bits, whereas the other numbers trade-off mantissa bits with exponent bits. This way is possible to extraordinarily increase the dynamic range and accuracy at the said ranges.

The Unum-III number system (Posits) looks very promising as an IEEE 754 replacement, but, in this thesis, we show that it can still be improved to provide more accuracy and dynamic range for the same number of bits to represent the numbers. More specifically, the unary representation of the "regime" bits of the Posits limits its accuracy or dynamic range and beg for optimisation.

Hence, the principal motivation of this dissertation is to design a new floating-point format suitable for replacing Posits, improving its accuracy and dynamic range without requiring more hardware resources.

#### 1.3 Objectives

The main objective of this dissertation is to come up with a number system that can overcome the shortcomings in accuracy and dynamic range identified in the Unum Type-III format.

This proposal intends to be a suitable replacement for the IEEE 754 Standard for floating-point arithmetic in low energy consumption applications by using an exponent and mantissa of dynamic size.

In order to achieve this objective, the state-of-the-art of the IEEE 754 Standard and the different Unum floating-point formats and arithmetic is studied in detail, a new format, Unum-IV, is proposed, and software and hardware models are developed.

The hardware model is a parameterisable Unum-IV Floating-Point Unit (FPU) with four basic operations (addition, subtraction, division and multiplication) is implemented.

To verify the new FPU, the FPU is attached as a peripheral to a RISC-V System on Chip produced by IOBundle, Lda, a Lisbon-based computer architecture company, and simulated. Additionally, the new FPU and an IEEE 754 FPU has been synthesised in an Integrated Circuit flow using the UMC 130nm silicon technology. The synthesis results in terms of the clock frequency, silicon area and power consumption are compared to the IEEE 754 FPU and the published results of a Posits FPU.

To verify the advantages in terms of accuracy and dynamic range, the Unum-IV FPU software model is and tested against the IEEE 754, already implemented in the C Standard library, using a K-Nearest Neighbours (KNN) application [31] as proof of the concept.

#### 1.4 Dissertation Outline

This dissertation is composed of seven chapters, including the present one. In the second chapter, the IEEE 754 Standard formats and the Unum formats are presented. In the third chapter, the new Unum Type-IV format is introduced and detailed. In the fourth chapter, the hardware implementation of a parameterised floating-point unit using the Unum Type-IV number system is fully described. In the fifth

chapter, the IEEE 754 Standard is compared against the Unum Type-IV format. In the sixth chapter, a KNN application is implemented and tested using different number systems, and the experimental results are discussed. Finally, in the seventh chapter, the conclusions are presented, the achievements are pointed out, and the directions of the future work are outlined.

## Chapter 2

## Background

This chapter describes the existing Floating-Point (FP) Unum formats (Unum Type-I, Unum Type-II and Unum Type-III), the IEEE 754 Standard and the "Bfloat16" format.

#### 2.1 IEEE Standard 754 Floating-Point

The IEEE 754 Standard, established in 1985 by the IEEE [3, 4, 5], is a standard that specifies formats and methods for floating-point arithmetic in computer programming environments. The format comprises three fields, sign, exponent and significand, exception conditions, rounding modes and their default handling. The implementation of the FP system may be performed in software, hardware or a combination of both. The IEEE 754 standard allows for FP computations to have the same results. It means that the standard defines a family of commercially feasible ways for systems to perform floating-point arithmetics.

The standard specifies formats for binary and decimal FP data, operations, conversions between FP formats and integer formats, exceptions and how to handle them. The formats approached in more detail in this chapter are the Single-Precision (SP) and the Double-Precision (DP) formats, because they are compared and tested against the new number system proposed in this dissertation, using a KNN application.

#### 2.1.1 Single-Precision

The single-precision floating-point is one of the formats belonging to the IEEE 754 family. It has a width of 32 bits and is encoded as shown in Figure 2.1.

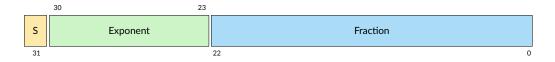

Figure 2.1: IEEE 754 Single-Precision Representation Format.

As represented in Figure 2.1, this format has three representation fields:

- S: the sign bit that indicates the sign of the significand of the signed number representation.

- Exponent: a biased 8-bit unsigned integer with a range between 0 and 255. The bias is 127, meaning that the actual 0 of the exponent is represented by an exponent biased value of 127. The 0 and 255 values of the biased exponent are reserved for "special" numbers explained in detail in Section 2.1.1. The actual exponent range is [-126:127].

- Fraction: the 23 explicit bits of the significand. The significand has a 23-bit fraction on the right side of the binary point plus an implicit leading bit on the left side. That hidden bit is always 1, unless the biased exponent is 0. As a result, the significand is in the format *0.fraction* if the exponent is equal to -126 and in the *1.fraction* format, otherwise.

The formula to convert the single-precision IEEE 754 FP format into the decimal representation is given by the following equation

$$X = \begin{cases} (-1)^{\mathsf{S}} \times 2^{\mathsf{Exponent}-127} \times 1. \text{fraction}, & \text{if Exponent} \neq 0\\ (-1)^{\mathsf{S}} \times 2^{-126} \times 0. \text{fraction}, & \text{otherwise} \end{cases}$$

(2.1)

#### **Special Cases**

There are four types of "special" representation patterns: the "subnormal" numbers, the "Not a Number" patterns (NaNs), the  $+\infty$  and the  $-\infty$ .

The 32-bit combinations where the biased exponent field is encoded with all zeros are the "subnormal" numbers. These numbers fill the underflow gap around zero. In those cases, the implicit leading bit is 0 instead of 1, and even though the biased exponent is 0, the actual exponent is -126 as shown in Equation 2.1; it is interpreted with the value of the smallest allowed exponent. These denormalized numbers are used to create a gradual underflow.

The other special representations are bit patterns where the exponent is encoded with all ones. If fraction=0, there are 2 possible combinations: S=0, which is used to represent  $+\infty$ , and S=1 which represents  $-\infty$ . The other possible combinations with fraction $\neq 0$  are used to represent the NaNs, interpreted as an undefined value. For example, dividing zero by zero results in an "undefined real" number and, therefore, computed as a NaN in computing systems.

The NaNs are separated into two types: the quiet NaN (qNaN) and the signalling (sNaN). The difference between them is that the qNaNs are used to propagate errors resulting from invalid operations, and the sNaNs signal an invalid operation exception. NaNs are a symbolic entity encoded in FP format, produced by the following operations:  $\infty - \infty$ ,  $-\infty + \infty$ ,  $0 \times \infty$ , 0/0 and  $\infty/\infty$ . The sNaNs correspond to a bit pattern of the fraction where the most significant bit is set to zero, and at least one of the remaining bits set to one. For the qNaNs, the fraction needs to have the most significant bit set to 1.

#### Rounding

The IEEE 754 provides four rounding modes: the round to nearest or ties to even; round toward  $+\infty$ ; round towards  $-\infty$ ; round towards 0. The default rounding mode provided by the standard is the first one, round to nearest.

#### Operations

The operations required by the IEEE 754 standard are the addition, subtraction, division, square root, fused multiply-add, remainder calculation, conversions between the IEEE 754 supported formats, comparisons, sign manipulation, scaling and quantizing, miscellaneous operations and total-ordering operations.

#### Exceptions

In the IEEE 754 standard, there are five types of exceptions: invalid operations, divide by zero, overflow, underflow and inexact results. When any exception occurs, it must be signalled by a status flag and issue a trap. The invalid operation occurs when the operation result is a qNaN, for example, an operation that has a NaN as an input. The divide by zero operation must return a signed  $\infty$  if the number to be divided is different from 0. Overflow occurs when the number is larger than the maximum possible value of the representation format. On the other hand, underflow occurs when the result of an operation is a number that has a smaller absolute value than the smallest representable value of the format used. Finally, the inexact exception happens when the rounded result of an operation is not exact and, in that case, no trap occurs.

#### 2.1.2 Other IEEE 754 Standard Formats and "Bfloat16" Format

The IEEE 754 Standard [5] includes four formats: half-precision (16 bits), single-precision (32 bits), double-precision (64 bits) and quadruple-precision (128 bits). The different formats features and be-haviour is similar, with a difference in the number of bits of the format, fields size and bias.

The exponent field has 5 bits for the 16-bit, 8 bits for the 32-bit, 11 bits for the 64-bit and 15 for the 128-bit formats. The fraction field has 10, 23, 53 and 112 bits, and the bias is equal to 15, 127, 1023, 16383, respectively.

Table 2.1 summarises all the IEEE 754 Standard Floating-Point Formats plus the "Bfloat16" format. "Bfloat16" [30] is a 16-bit format, with one sign bit, eight exponent bits and seven fraction bits. The 8-bit exponent allows this format to have an identical dynamic range compared with the 32-bit float, so it is a truncated version of the IEEE 754 single-precision format. The main idea was to replace the 32-bit IEEE-754 with a format that occupies half of the computer memory, making it faster, simpler, and cheaper, with the downside of losing precision. However, as stated before, research show [32, 33, 34, 27] that many ML models tolerate this trade-off between speed and precision, as they increase the performance using less memory and reach the same results without degradation.

| Format                       | Width [Bits] | Exponent [Bits] | Exponent Bias | Significand [Bits]        | Dynamic Range [Decades] |

|------------------------------|--------------|-----------------|---------------|---------------------------|-------------------------|

| IEEE 754 Half-Precision      | 16           | 5               | 15            | 10 explicit + 1 implicit  | 12.04                   |

| Google Bfloat16              | 16           | 8               | 127           | 7 explicit + 1 implicit   | 83.47                   |

| IEEE 754 Single-Precision    | 32           | 8               | 127           | 23 explicit + 1 implicit  | 83.39                   |

| IEEE 754 Double-Precision    | 64           | 11              | 1023          | 52 explicit + 1 implicit  | 631.56                  |

| IEEE 754 Quadruple-Precision | 128          | 15              | 16383         | 112 explicit + 1 implicit | 9882.51                 |

Table 2.1: IEEE 754 Standard and "Bfloat16" Format Features.

#### 2.2 Unum

The "Universal Numbers", or Unums, introduced by John L. Gustafson in 2013 are a binary and arithmetic representation format for real numbers. Unums have so far three different types of representation. Type-I is a superset of the IEEE 754 Standard floating-point format, introduced in [6]. Type-II enables a clean mathematical design based on the *projective reals* and relies on lookup tables. This format was explained and detailed by Gustafson in an 2016 interview [14]. It is a direct map of signed integers to the projective "real" number line. The last version, introduced in 2017 is the Type-III, aka, Posits [15]. Type III is a hardware-friendly version with all the advantages from the previous types, and where the problems found in Type I due to the variable sizes are solved.

The main idea of John L. Gustafson was to create a new number system for computers that could be a suitable replacement to the IEEE 754 format. This implies a system that could give more accurate results using fewer or the same number of bits, respects all the algebraic laws that IEEE 754 breaks, and saves memory resources, energy and power consumption.

#### 2.2.1 Unum Type-I

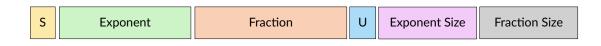

As described in [15], Unum Type-I is a superset of IEEE 754. The representation format is as shown in Figure 2.2. This format uses a "u-bit" (U) to indicate if the number is an exact float (U=0) or if the number lies in the open interval between two consecutive floats (U=1).

Figure 2.2: Unum Type-I Representation Format.

The sign (S) bit indicates if the number is a negative or a positive value. If the sign bit is 1 the number is negative, otherwise it is positive or zero. The exponent and fraction fields also have a similar definition as in the IEEE 754 format.

However, in the IEEE 754 format, the fields have a fixed size, whereas in Unum Type I, they have variable size, depending on the exponent size and significand size fields. They can go from 1 bit to the maximum set by the user, meaning that they can vary in size to save storage and bandwidth.

This format is a compact way to express interval arithmetic. However, it requires extra management

at the hardware implementation due to the variable width of the exponent and significand field. It also can avoid rounding errors, underflow and overflow because of the interval arithmetic approach.

However, there are disadvantages of the Unum Type-I format inherited from the IEEE 754, in particular, the existence of redundant representations, later solved by Unum Type-III as will be shown below. The Unum Type-I format is explained in more detail in [6].

#### 2.2.2 Unum Type-II

Unum Type-II, introduced in 2016, intended to solve some of the drawbacks of Unum Type-I, such as the existence of redundant representations. While Unum Type-I is a superset of IEEE 754, Unum Type-II is a complete redesign, losing compatibility with IEEE 754.

Unum Type-II format enables a clean mathematical design based on projective reals. They are a direct-map of signed integers onto the "real" projective line, relying on look-up tables. This format has many ideal mathematical properties based on the projective reals. As John L. Gustafson explained in an interview [14], Unum Type-II shares about 80 % of the mathematical advantages of Unum Type-I, such as the ability to avoid overflows, underflows and rounding errors. Unum Type-II is a configurable accuracy, fast and simple format, which allows the user to design a custom number system for a particular workload, particularly interesting for the deep learning community.

Figure 2.3 shows the visual representation of a 5-bit Unum-II projective "real" number line. The upper right quadrant has an ordered set of real numbers  $(x_i)$ , whereas the upper left quadrant has the symmetric of those values  $(-x_i)$ . As for the lower quadrants, they hold the reciprocal values of the upper quadrants. This geometry of the projective reals is what gives the format many ideal mathematical properties.

The last bit of the 5-bit representation format is the "u-bit"; if U=0 the representation is exact, otherwise (U=1), the number represents the open interval between consecutive exact numbers. The most significant bit is the sign bit.

One of the main disadvantages of this format is that they rely on look-up tables, which are limited to 20 bits or less to be hardware efficient, which results in low precision for certain operations. This format is explained in more detail in [6] and [14].

#### 2.2.3 Unum Type-III: Posits

Unum Type-III, or Posits as they are also known, were introduced by John L. Gustafson in 2017 [15]. They are determined by the format size (n) and by the number of bits necessary to represent the exponent size (es). Therefore, the notation used in this dissertation to express the configuration is Posit<n,es>. Figure 2.4 shows the generic representation format of Posits with four fields.

- S: follows the same definition as Unum Type-I: S=0 if the number is positive and S=1 if the number is negative.

- Regime: used to calculate a scale factor of useed Regime. The number of regime bits is variable and

Figure 2.3: Visual Representation of the Unum Type-II Projective Real Number Line [15].

can land between 1 and n-1 bits. It is determined by a run of identical bits, ending either because there are no more bits in the n-bit word or because it runs into an opposite bit. The *useed* value is a described as a "batched" form of powers of two, which depends on *m* the number of bits of the exponent, and is given by  $useed = 2^{2^m}$ .

- Exponent: represents the scaling factor of 2<sup>Exponent</sup>. Unlike the floats, there is no bias in the exponent representation. This field has a variable length depending on the Regime field, after which it follows.

- Fraction: represents the significant digits on the right side of the significand's binary point. It follows the same logic as the IEEE 754 floats, but the main difference is that the implicit leading bit is always 1, as there is no sub-normal mode.

| S | Regime | Exponent | Fraction |

|---|--------|----------|----------|

|---|--------|----------|----------|

Figure 2.4: Unum Type-III Representation Format.

The formula to convert a Type-III value into its decimal representation is given by the following equation

$$X = (-1)^{\mathsf{S}} \times \mathsf{useed}^{\mathsf{Regime}} \times 2^{\mathsf{Exponent}} \times 1.\mathsf{fraction}$$

(2.2)

Type-III has no NaN bit representation. Instead interrupts are advocated for this and other special cases. The interrupts are handled by an interruption handler that can be set to either report the error or

work around it to continue computing. That means that Posits can use more bit patterns to represent real numbers and that fewer hardware resources are used. In terms of the bit patterns available, the Posits architecture has only one representation for 0 compared with the two zero representations in IEEE floats, the  $0^+$  and  $0^-$ . This is an advantage because it follows the mathematical logic of the concept of 0. On the other hand, the Type-III format does not have signed  $\infty$  representations. There are no subnormal numbers in Posits, since the hidden bit is always 1. It means that there is no "gradual underflow".

With Posits, the numbers close to 1 are given more significand bits (more precision bits) and fewer exponent bits. This is an important concept called *tapered precision*.

The dynamic range can be larger than the IEEE 754 dynamic range because of the variably-sized exponent. Gustafson intended to have a drop-in replacement for the IEEE floats, with a faster, more accurate, more hardware-friendly and lower cost number system. Figure 2.5 is extracted from [16] and sums up the advantages and disadvantages of all Unum types.

| Unum     | Date<br>Intro-<br>duced | IEEE 754<br>Compati-<br>bility     | Advantages                                                                                                                                                                                                         | Disadvantages                                                                                                             |

|----------|-------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Type I   | March<br>2015           | Yes;<br>perfect<br>superset        | Most bit–efficient<br>rigorous–bound<br>representation                                                                                                                                                             | Variable width<br>management needed;<br>inherits IEEE 754 dis-<br>advantages, such as<br>redundant representations        |

| Type II  | January<br>2016         | No;<br>complete<br>redesign        | Maximum infor-<br>mation per bit<br>(can customize to a<br>particular workload);<br>perfect reciprocals<br>(+ - × ÷ equally easy);<br>extremely fast via<br>ROM table lookup;<br>allows decimal<br>representations | Table look–up<br>limits precision to<br>~20 bits or less;<br>exact dot product<br>is usually expensive<br>and impractical |

| Type III | February<br>2017        | Similar;<br>conversion<br>possible | Hardware-friendly;<br><i>posit</i> form is a drop-<br>in replacement<br>for IEEE floats (less<br>radical change);<br>Faster, more accurate,<br>lower cost than float                                               | Too new to have<br>vendor support<br>from vendors yet;<br>perfect reciprocals<br>only for 2 <sup>n</sup> , 0, and ±∞      |

Figure 2.5: Unum Type-I,II and III Advantages and Disadvantages.

From the figure, it is possible to conclude that Unum Type-III is the most promising Unum format for replacing IEEE 754, and some studies show that Posits can have better behaviour in DL applications compared to floats [8, 23, 22, 21, 29, 19].

Even though this format is the most promising, there are features of Unum Type-I that might be interesting to keep exploring, such as the exponent size field, the level of compatibility with IEEE 754, the use of variably-sized significand and exponent, and its bit-efficiency.

The Regime field in Type-III field behaves as a "super exponent", which does not appear to be the best approach to increase the dynamic range or the precision. In fact, those bits can be more useful if used to extend the significand or exponent width. This is the weakest aspect of the Type-III system.

There are other minor weaknesses of this format, such as the fact that there is no difference between the  $-\infty$  and  $+\infty$  representations, 64-bit Posits can not represent the maximum corresponding float [35], and the level of compatibility with IEEE 754 is lower than Unum Type-I.

In the following chapters, a new Unum format, called Unum-IV, is proposed and explained in detail. This new format explores and combines ideas from both Unum Type-I and the Unum Type-III formats, specifically, the use of an exponent size field, the use of variably-sized significand and exponent. Unum-IV also dispenses with NaN,  $-\infty$  and  $+\infty$ , and does not have two different patterns to represent 0. However, the new format solves the main problem of Posits: the space wasting of the Regime bits as explained above.

The new Unum-IV format uses regular exponent and significand fields, but resorts to an elaborate scheme to avoid redundant representations by introducing a dynamic hidden bit not only in the significand but also in the exponent. The significand's hidden bit also serves as the sign, which needs no specific field.

## **Chapter 3**

## **Unum Type-IV**

This chapter introduces a new floating-point representation format developed during this thesis, called Unum Type-IV. The new Unum Type-IV, shortly Unum-IV, replaces the unary numeral system used in the type-III format, aka Posit numbers, with a regular binary system. The Unum formats (types I, II, and III) introduced the concept of tapered precision: numbers having an absolute value close to 1 are given more significand bits and fewer exponent bits, and the very large or very small numbers give up significand bits and use more exponent bits. This way, it is possible to extraordinarily increase the dynamic range and accuracy at the said ranges. The main idea in this new representation is to use a hidden bit in the exponent and a hidden bit in the significand to prevent redundant representations. This new format recovers and extends Unum Type-I ideas while being hardware friendly like the Unum Type-III format. Hence, it is named Unum type-IV.

This new format, like Posits, uses the balance between two aesthetics for calculation involving real numbers: (1) the non-rigorous but cheap, fast and "good enough" approach, and (2) the mathematically rigorous and expensive approach, both in execution time and storage.

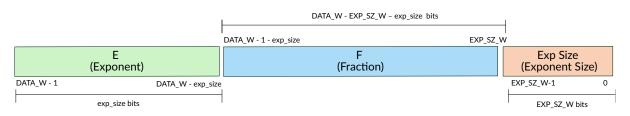

#### 3.1 Unum Type-IV Generic Format

The Unum-IV generic format has three fields: the exponent, the fraction and the exponent size. In order to avoid redundant representations, a hidden bit is added to the exponent as well as to the significand. These hidden bits optimise the use of all bit patterns as representable real numbers. In both cases, exponent and significand, the hidden bit is the Most Significant Bit (MSB) and the extraction of exponent and significand is explained in Section 3.2. The significand and exponent in this format are both signed, with the hidden bits providing the sign information. The exponent is in 1's complement format, so there is no need for a bias as in IEEE 754 and the significand is in 2's complement format, which dispenses with the sign bit field used in other formats such as the IEEE-754 format.

The Unum-IV configuration and enconding is determined by the format size (DATA\_W) and by the number of bits necessary to represent the exponent size (EXP\_SZ\_W). Therefore, the notation

Unum-IV<DATA\_W,EXP\_SZ\_W>

is used here to denote a DATA\_W-bit Unum-IV with EXP\_SZ\_W bits for the exponent size field. The generic Unum-IV floating-point format is encoded as shown in Figure 3.1, and the next subsections explain each of the fields.

Figure 3.1: Generic Unum-IV Representation Format.

Using this encoding, and processing the fields as explained below, one can obtain the significand s and the exponent e of the real number r represented in the Unum-IV<DATA\_W,EXP\_SZ\_W> format and given by

$$r = s \times 2^e \tag{3.1}$$

#### Exponent Size (Exp Size)

The Exponent Size (Exp Size) is a small unsigned integer, which has a width defined by the parameter EXP\_SZ\_W, and can assume a value in the range from 0 to  $2^{\text{EXP}_{\text{SZ}_{\text{W}}}} - 1$ . The Exp Size field allows for tapered accuracy since it represents the number of explicit bits necessary to represent the exponent of the number in the 1's complement format. It establishes a higher accuracy for numbers that are close to 1, and a lower accuracy for very large or very small numbers.

Denoting the Exp Size bits by  $ExpSize_i$ , the explicit exponent size in bits ExpSz is given by

$$ExpSz = \sum_{i=0}^{\mathsf{EXP}_{-}\mathsf{SZ}_{-}\mathsf{W}_{-1}} \mathsf{ExpSize}_{i} 2^{i}$$

(3.2)

#### Exponent (E)

The Exponent (E) field holds the explicit exponent, as indicated by its name. Unlike the IEEE 754, the exponent is not biased and is represented as a signed integer in the 1's complement format with a hidden (implicit) most significant bit. The exponent hidden bit is always the negation of the most significant bit of the E field. Moreover, the 1's complement representation breaks for the widest exponent and most negative 1's complement exponent: (1)00...00, where the hidden bit is shown in brackets followed by EXP\_SZ\_W zeros. This combination is reserved for subnormal representations to allow for a graceful underflow. Subnormal representations are also used in the the IEEE 754 standard, though with a different implementation.

The E field width is ExpSz, therefore it is variably-sized. If ExpSz = 0, the E field is not present. Following the logic of the 1's complement signed integers, if the hidden bit is zero the exponent is positive and negative otherwise. When E is filled with zeros and Exp Size is filled with ones, indicating the widest possible exponent, the subnormal representation applies, as explained above. In this mode, the exponent is valued  $-2^{ExpSz} + 2$ , which is one unit more than the normal 1's complement valuation of  $-2^{ExpSz} + 1$ . Hence, the exponent's magnitude falls in the following range of values:  $[-2^{ExpSz} + 2 : 2^{ExpSz} - 1]$ .

Without the subnormal representation, there would be a noticeable gap between 0 and smallest negative and positive numbers. By filling this gap around 0, the logarithmic distance between the numbers when approaching zero increases but not as abruptly as with a simple flush to zero approach. This allows computation results to lose precision slowly when very small. Hence, in the new Unum-IV format, the exponent value is given by

$$e = \begin{cases} 0, & \text{if } ExpSz = 0\\ -2^{ExpSz} + 2, & \text{if } ExpSz = 2^{\mathsf{EXP}.\mathsf{SZ}.\mathsf{W}} - 1 \land E = 0\\ \overline{E_{ExpSz-1}}(-2^{ExpSz} + 1) + \sum_{i=0}^{ExpSz-1} E_i 2^i, & \text{otherwise} \end{cases}$$

(3.3)

The exponent hidden bit  $E_{HB}$  is introduced to avoid redundant representations. It does not need to be stored in memory, and is given by

$$E_{HB} = \begin{cases} absent, & \text{if } ExpSz = 0\\ \hline E_{ExpSz-1}, & \text{otherwise} \end{cases}$$

(3.4)

#### Fraction (F)

The Fraction (F) field represents the significant digits on the right side of the significand binary point. Like in the IEEE 754 format, in the Unum-IV format, the significand has an implicit leading bit. However, unike in the IEEE 754 format, this hidden bit is not always 1.

In the Unum-IV case, the significand is represented by a signed 2's complement number, and the hidden bit is always the complement of the fraction's MSB, except for the subnormal representation (see previous section), where the hidden bit equals the fraction's MSB. Thus, if the hidden bit is 0, the represented number is positive or zero; if the hidden bit is one, the number is negative. The F field bit-width *FracSize* depends of course on the format width and exponent size and is given by

$$FracSize = \mathsf{DATA}_W - ExpSz - \mathsf{EXP}_SZ_W$$

(3.5)

Hence, in the new Unum-IV format, the significand is given by

$$s = \begin{cases} -F_{-1} + \sum_{i=1}^{FracSize} F_{-i}2^{-i}, & \text{if } ExpSz = 2^{\mathsf{EXP\_SZ\_W}} - 1 \land E = 0\\ -\overline{F_{-1}} + \sum_{i=1}^{FracSize} F_{-i}2^{-i}, & \text{otherwise} \end{cases}$$

(3.6)

The significand's hidden bit  $F_{HB}$  in the new Unum-IV format dispenses with the sign bit as in the IEEE-754 format and is given by

$$F_{HB} = \begin{cases} F_{MSB}, & \text{if } ExpSz = 2^{\mathsf{EXP}_{-}\mathsf{SZ}_{-}\mathsf{W}} - 1 \land E = 0\\ \hline F_{MSB}, & \text{otherwise} \end{cases}$$

(3.7)

#### **Tapered Precision**

The tapered precision is easily verified after having explained the format's fields in the previous sections. The sum of the exponent and fraction sizes is constant and given by

$$ExpSz + FracSize = DATA_W - EXP_SZ_W$$

(3.8)

On the one hand, the very large or very small numbers require more exponent bits to represent, get fewer fraction bits and therefore less precision. On the other hand, the numbers closer to magnitude 1 require less exponent bits, get more fraction bits and therefore more precision. The numbers whose exponent equals 0 do not require any exponent bits and get all the available DATA\_W - EXP\_SZ\_W bits for precision.

#### 3.2 Field Extractions

In this section, the exponent and significand binary format extraction is explained and exemplified. As mentioned before, the exponent and significand of the Unum-IV format are both variably-sized, so the field extractions can't be performed in parallel. In these conditions, the extractions are sequenced.

Firstly, the exponent size is extracted because it only depends on the second parameter in the Unum-IV<DATA\_W, EXP\_SZ\_W> notation, that is, EXP\_SZ\_W.

The *ExpSize* field is extracted by taking the EXP\_SZ\_W least significant bits of the Unum-IV number. Using the Unum-IV<32,4> configuration as an example, the *ExpSize* field is given by the four least significant bits of the 32-bit Unum-IV word, and it is interpreted as an unsigned 4-bit integer.

After extracting the ExpSize value, the exponent and significand can be both extracted in parallel.

#### 3.2.1 Exponent Extraction

The exponent extraction follows the algorithm shown in the Listing 3.1. The hidden bits are shown in brackets and the exclamation mark expresses the bit inversion. For example, (1) means that the implicit hidden bit is 1.

There are three different scenarios in the exponent extraction. The first scenario is when *ExpSize*=0, which implies that the exponent is also zero. These are the numbers close to 1 and do not require an exponent. The second scenario is when the  $ExpSize = 2^{EXP\_SZ\_W} - 1$ , the maximum exponent size allowed by the Unum-IV<DATA\_W, EXP\_SZ\_W> configuration, and the exponent E field is all zeros. This is the subnormal representation, where the significand's hidden bit is flipped compared to the normal

representations, and the exponent is incremented by 1 to fill the gap around zero of the Unum-IV normal representation.

For example, in the Unum-IV<32,4> case, this scenario corresponds to ExpSize = 15 and the E field with 15 zeros. The third and normal scenario is when the exponent is extracted by left-concatenating the exponent and significant hidden bits to the E and fraction bits.

Listing 3.1: Pseudo-code of the Exponent Extraction Algorithm.

```

if (ExpSize == 0)

Exponent = 0

else if (ExpSize == 2^EXP_SZ_W-1 && E == 0) // Exception

Exponent = (!E[ExpSize-1])E[ExpSize-1:0] + 1

else

Exponent = (!E[ExpSize-1])E[ExpSize-1:0]

```

#### 3.2.2 Significand Extraction

The significand extraction follows the algorithm shown in the Listing 3.2. As in the exponent extraction, the hidden bit is shown in brackets, the exclamation mark expresses the bit inversion, and the dot represents the binary point of the significand.

There are two different extraction scenarios for the significand, In both scenarios, the significand is extracted by concatenating the implicit hidden bit to the left of the binary point, and the fraction bits to the right of the binary point. The first scenario corresponds to the subnormal numbers when the E field is all zeros and ExpSize filed all ones. In this scenario, the hidden bit is the same as the fraction's MSB. The second scenario is for the normal representation and the hidden bit is the complement of the fraction's MSB.

For example, in the Unum-IV<8,2> case, the first scenario corresponds to ExpSize = 3 and the E field with 3 zeros. If the F is field with 3 zeros, then the significand is given by (0).000. An example for the second scenario is when F is equal to 10000, the significand is (0).10000.

Listing 3.2: Pseudo-code of the Significand Extraction Algorithm.

```

if (ExpSize == 2^EXP_SZ_W-1 && E ==0) // Exception

Significand = (F[DATA_W-ExpSize-EXP_SZ_W-1]).F[DATA_W-ExpSize-EXP_SZ_W-1:0]

else

Significand = (!F[DATA_W-ExpSize-EXP_SZ_W-1]).F[DATA_W-ExpSize-EXP_SZ_W-1:0]

```

#### 3.2.3 Examples

Table 3.1 exemplifies the significand and exponent extraction for a 32-bit Unum-IV format with a 4-bit exponent size field. From Table 3.1 it is possible to conclude that the exponent minimum width is 0, and the maximum is 16, including the implicit leading hidden bit. The significand has a width between 14 and 29 bits, also with the hidden bit.

| Exponent Size        | Exponent                                | Significand                            |

|----------------------|-----------------------------------------|----------------------------------------|

| 0(min)               | 0                                       | $(\overline{F_{27}}).F_{27}F_1F_0$     |

| 1                    | $(\overline{E_0})E_0$                   | $(\overline{F_{26}}).F_{26}F_1F_0$     |

| 2                    | $(\overline{E_1})E_1E_0$                | $(\overline{F_{25}}).F_{25}F_1F_0$     |

| 3                    | $(\overline{E_2})E_2E_1E_0$             | $(\overline{F_{24}}).F_{24}F_1F_0$     |

|                      |                                         |                                        |

| i                    | $(\overline{E_{i-1}})E_{i-1}E_1E_0$     | $(\overline{F_{27-i}}).F_{27-i}F_1F_0$ |

|                      |                                         |                                        |

| 8                    | $(\overline{E_7})E_7E_1E_0$             | $(\overline{F_{19}}).F_{19}F_1F_0$     |

|                      |                                         |                                        |

| $15 \wedge E \neq 0$ | $(\overline{E_{14}})E_{14}E_{1}E_{0}$   | $(\overline{F_{12}}).F_{12}F_1F_0$     |

| $15 \wedge E = 0$    | $(\overline{E_{14}})E_{14}E_{1}E_{0}+1$ | $(F_{12}).F_{12}F_1F_0$                |

Table 3.1: Exponent and Significand Extraction for DATA\_W=32 and EXP\_SZ\_W=4.

### 3.3 Features

#### 3.3.1 Special Cases

The Unum Type-4 format does not have any special numbers such as "NaN",  $-\infty$ ,  $+\infty$ ,  $\infty$ ,  $0^+$  or  $0^-$ . Instead of having a range of representations locked for those special cases (losing space for real representable numbers), every combination of bits is used to represent a real number. Hardware exceptions may be implemented when interesting conditions occur. That simplifies the hardware and also extends the dynamic range.

#### 3.3.2 Exceptions

There are three different types of exceptions in the present Unum-IV implementation: the *divide by zero*, *overflow* and *underflow* exceptions. The divide by zero exception occurs when in a division operation the divisor is zero. The overflow exception happens when some operation results in a number that would require a larger exponent than allowed by the Unum-IV format used. The underflow exception occurs when some operation produces a result that would require an exponent more negative than allowed by the format.

The exceptions are handled using flags that monitor the various stages for producing the results. If particular conditions happen, the respective flags are activated, simplifying the hardware used. The exception can then be tread by special hardware circuits or software routines.

#### 3.3.3 Rounding

There are two rounding modes in the present Unum-IV implementation: "the round to the nearest", ties even" and the "truncation mode". The rounding or truncation is necessary since operations with

floating-point numbers can often result in non-representable numbers in terms of precision. Thence, the result needs to be rounded to the nearest representable Unum-IV value or truncated to the last representable digit. The default mode is the "round to the nearest, ties even".

As in IEEE754, the "round to the nearest, ties even" mode uses three extra bits of less significance than the significand bits, a *guard* bit, a *round* bit and a *sticky* bit. The most significant bit is the *guard* bit, and the least significant bit is the *sticky* bit.

In this mode, if the exact result can not be represented by an Unum-IV number, the result is rounded to the nearest of two possible values. If there is a tie between the two possibilities, then the even alternative is chosen. The action to be taken according to those three bits is shown in Table 3.2.

| Guard Bit | Round Bit | Sticky Bit | Action                                |

|-----------|-----------|------------|---------------------------------------|

| 0         | Х         | Х          | Round Down                            |

| 1         | 0         | 0          | If the significand LSB is 1: Round Up |

|           |           |            | Otherwise: Round Down                 |

| 1         | 0         | 1          | Round Up                              |

| 1         | 1         | 0          | Round Up                              |

| 1         | 1         | 1          | Round Up                              |

Table 3.2: "Round to the nearest, ties even" Mode.

The X ("Don't Care") means that the bit can either be 0 or 1. In either case, it will have no impact on the action to be taken. In terms of the rounding action: rounding up implies adding 1 bit to the significand, and rounding down does not require any action.

#### 3.3.4 Dynamic Range and Precision

The length of the significand determines the precision of the representable floating-point number. The ratio between the smallest and the largest positive number determines the dynamic range of the number system in evaluation. Since the Unum-IV number system has a variably-sized significand and exponent, the Unum-IV dynamic range and precision depend on the value of the parameter EXP\_SZ\_W. The larger this parameter is, the greater the exponent contribution in the format, and therefore the dynamic range will increase.

The relation between the exponent size field and the dynamic range is: increasing the number of bits available to represent the exponent increases the dynamic range, and vice-versa. However, increasing the EXP\_SZ\_W means decreasing the maximum number of bits available to the fraction field since they are the remaining bits of the format. Therefore, if the maximum number of fraction bits decreases, so does the precision.

The principal advantage of the Unum-IV format is the ability to choose the parameters, DATA\_W and EXP\_SZ\_W, to adjust the trade-off between the dynamic range and precision to meet the performance

needs of an application. If the application needs more accurate answers with numbers of small magnitude, it will need more fraction bits and fewer exponent bits. On the other hand, if the application works within a range of extremely small or large values, it will need more exponent bits with less fraction bits available, increasing the dynamic range. This trade-off can make a huge difference in applications that process large amounts of data.

In the Unum-IV generic format, the smallest and largest positive representable number, *minpos* and *maxpos* respectively, are given by

$$\begin{cases} \min pos = 2^{\left[-2^{\left[2^{\mathsf{EXP.SZ.W}}-1\right]}+2\right]} \times 2^{-\left[\mathsf{DATA_W}-\left(2^{\mathsf{EXP.SZ.W}}-1\right)-\mathsf{EXP.SZ.W}\right]} \\ \max pos = 2^{\left[2^{\left[2^{\mathsf{EXP.SZ.W}}-1\right]}-1\right]} \times \left(1-2^{-\left[\mathsf{DATA_W}-\left(2^{\mathsf{EXP.SZ.W}}-1\right)-\mathsf{EXP.SZ.W}\right]}\right) \end{cases}$$

(3.9)

Hence, the dynamic range, measured in decades, is given by the following formula

**Dynamic Range** =

$$log_{10}\left(\frac{maxpos}{minpos}\right)$$

(3.10)

Table 3.3, summarises and exemplifies the relation between the generic parameters of the Unum Type-IV number system and the dynamic ranges.

| Unum-IV< n, k > | minpos ( $pprox$ )       | maxpos ( $pprox$ )      | Dynamic Range [Decades] |

|-----------------|--------------------------|-------------------------|-------------------------|

| n=8, k=2        | $1.95\times 10^{-3}$     | $1.12 \times 10^2$      | $4.76 \times 10^0$      |

| n=16, k=2       | $7.63\times 10^{-6}$     | $1.28 \times 10^2$      | $7.22 \times 10^0$      |

| n=16, k=3       | $1.84\times10^{-40}$     | $1.67\times 10^{38}$    | $7.80 	imes 10^1$       |

| n=32, k=3       | $2.80\times10^{-45}$     | $1.70\times10^{38}$     | $8.28 \times 10^1$      |

| n=32, k=4       | $3.45 \times 10^{-9868}$ | $7.08 \times 10^{9863}$ | $1.97 \times 10^4$      |

| n=64, k=4       | $8.03 \times 10^{-9878}$ | $7.08 \times 10^{9863}$ | $1.97 \times 10^4$      |

| n=128, k=4      | $3.06\times10^{-9883}$   | $7.08 \times 10^{9863}$ | $1.97 \times 10^4$      |

Table 3.3: Unum Type-IV Dynamic Ranges.

The number of precision bits (number of fraction bits) for each representable Unum-IV value  $p_{-}$  bits is given by

$$\boldsymbol{p}_{-}\boldsymbol{bits} = \mathsf{DATA}_{-}\mathsf{W} - ExpSz - \mathsf{EXP}_{-}\mathsf{SZ}_{-}\mathsf{W}$$

(3.11)

where

• *ExpSz*: number of exponent bits, excluding the implicit leading bit.

Therefore, the number of precision bits can go from DATA\_W- $2^{EXP_SZ_W}$ +1-EXP\_SZ\_W to DATA\_W-EXP\_SZ\_W bits.

Table 3.4 shows some examples of the relationship between the Unum-IV parameters and the number of precision bits.

| Unum-IV <n,k></n,k> | p_bits          |  |

|---------------------|-----------------|--|

| n=8, k=2            | from 3 to 6     |  |

| n=16, k=2           | from 11 to 14   |  |

| n=16, k=3           | from 6 to 13    |  |

| n=32, k=3           | from 22 to 29   |  |

| n=32, k=4           | from 13 to 28   |  |

| n=64, k=4           | from 55 to 60   |  |

| n=128, k=4          | from 109 to 124 |  |

Table 3.4: Unum Type IV Precision.

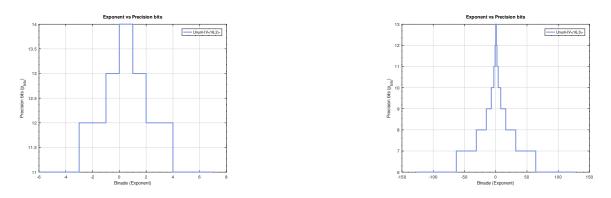

Figs. 3.2 and 3.3 help visualize the tapered precision of the Unum-IV format with different parameters, where the  $p\_bits$  are plotted in function of the binades. A *binade*, in software engineering, is the set of numbers of a format with the same base 2 exponent, i.e., the group of bit patterns that have the same exponent bits. Note that the word *decade* denotes the set of numbers with the same base 10 exponent.

Figure 3.2: Unum-IV<16,2> and Unum-IV<16,3> Precision Bits vs Binade (Exponent).

Figure 3.3: Unum-IV<32,3> and Unum-IV<32,4> Precision Bits vs Binade (Exponent).

When the numbers have exponents near 0, they have a higher resolution because the Unum-IV system has more space for fraction bits. As they run far from 0, either to the positive or negative side, the precision decreases symmetrically because the number of bits used to represent the exponent increases. The gradual underflow achieved by the denormalized numbers also enables a gradual loss

of precision.

## 3.4 Examples

#### 3.4.1 Unum-IV to Decimal Conversion

Three examples of the decoding of the Unum-IV format are presented in Figs. 3.4, 3.5, 3.6 and their mathematical meaning and field extraction are explained in detail. Each example is a 32-bit string Unum-IV, DATA\_W=32, with a 4-bit exponent size field, EXP\_SZ\_W=4.

These examples were selected to give a more concrete way of understanding how the encoding of Unum-IV takes place and express the tapered precision, the wide dynamic range and the gradual underflow attached to this format. The first example is the smallest positive number, and the second is the largest positive number representable by the Unum-IV<32,4> format. In both examples, the exponents use the maximum number of exponent bits allowed, 15 exponent explicit bits, and the significand has the minimum number of precision bits (13 fraction bits). The last and third example represents the closest number to 1, which has the maximum number of precision bits (28 fraction bits) since there is no exponent bit in the format, meaning that the exponent is equal to 0.

Following the tapered precision concept, where the numbers with a magnitude near 1 have more precision bits than the numbers extremely small or large numbers and analysing the exponent magnitude of the examples, it is possible to conclude that the last example (near 1) has more precision bits than the previous examples.

The first example is an extremely small number with the minimum fraction width allowed by the chosen parameters and falls on the exponent range lower bound (the exception expressed in the extraction algorithm). This exception case uses the fraction most significant as the implicit leading bit and increments by one the exponent to ensure the closure around 0 of the Unum Type IV numerical system (gradual underflow).

The smallest and largest positive number clearly show the wide dynamic range achieved with the variably-sized exponent and significand compared with the IEEE 754 floats. As can be seen in Table 3.3, Unum-IV<32,4> has a dynamic range in order of 20 thousand  $(1.97 \times 10^4)$  of decades, while the IEEE 754 floats have a dynamic range of 83 decades, approximately. The difference can be explained by the fact that IEEE 754 floats have a biased exponent of 11 bits, whereas the exponent of the Unum-IV<32,4> format can be up to 16 bits, counting with the implicit leading bit.

#### **Smallest Positive Number**

####

Figure 3.4: Example 1 of an Unum-IV<32,4> Bit String.

00001. The exponent represents -32766 in 1's complement format. The remaining 32 - 4 - 15 = 13 bits represent the explicit fraction bits. In the exceptional case, the hidden bit is given by the fraction MSB resulting in a (0).000000000001 significand (colour-coded blue). The significand is given by  $2^{-13}$  and the decimal value of this example is  $2^{-13} \times 2^{-32766} \approx -3.45 \times 10^{-9868}$ .

#### Largest Positive Number

Figure 3.5: Example 2 of an Unum-IV<32,4> Bit String.

#### Largest Number Smaller Than One

Figure 3.6: Example 3 of an Unum-IV<32,4> Bit String.

the significand is evaluated as  $\sum_{i=1}^{28} 2^{-i}$  and the decimal representation of the last example is  $2^0 \times \sum_{i=1}^{28} 2^{-i} = 0.999999962747097015380859375$ .

#### 3.4.2 Unum-IV<4,1> Enconding