## **Asynchronous Audio Sample Rate Converter**

### Pedro Miguel Portela Teixeira

Thesis to obtain the Master of Science Degree in

### **Electrical and Computer Engineering**

Supervisor(s): Prof. José João Henriques Teixeira de Sousa

### **Examination Committee**

Chairperson: Prof. Francisco André Corrêa Alegria Supervisor: Prof. José João Henriques Teixeira de Sousa Member of the Committee: Prof. Gonçalo Nuno Gomes Tavares

September 2021

ii

### Declaration

I declare that this document is an original work of my own authorship and that it fullfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

#### Acknowledgments

This thesis is the result of two years of work and five years of studies in Instituto Superior Técnico. As such, I would like to thank those who helped me in this journey.

From the two years of development of the thesis, I thank Pedro Miranda and João Lopes for helping me testing the work performed. I also thank Valter Mario for helping me with the initial development of the core during my internship at IObundle. Special thanks to my advisor, Professor José Teixeira de Sousa, for proposing the subject of the thesis to me, reviewing it, and keeping me productive, even while stressing due to the pandemic.

From the five years of studies in Instituto Superior Técnico, I want to acknowledge my colleagues who helped me with my studies and ensured my success, as well as lifting my spirits with engineering jokes: Daniel Pestana, Renato Dias, José Gomes, Gil Serrano, João Pinto, Miguel Cardoso, Afonso Luis, Simão Eusébio and Thomas Berry.

Lastly, I want to give special thanks to my parents, Carlos Teixeira and Sónia Teixeira, as well as my brother, João Teixeira, for giving me support, allowing me to achieve my objectives.

#### Resumo

Esta dissertação propõe o projeto de um novo conversor de frequências de amostragem assíncrono multi-canal de 24 bits ou menos, com os seguintes objetivos: (1) taxa de distorção harmónica e ruído total (THD+N) de -130 dB ou menos, (2) razões de conversão suportadas entre 1:24 e 24:1; centenas de canais de audio; (3) tempo de sincronização inferior a 200 ms, (4) variação da fase entre entrada e saída inferior a uma amostra de saída após o reset, e (5) consumo de recursos por canal semelhante ao CWda52, ou menor.

Todos os objetivos foram cumpridos, e centenas de testes foram aplicados ao novo projeto, que obtém uma THD+N de um mínimo de –143 dB até um máximo de –136 dB para um total de 121 testes, com uma média de aproximadamente –140 dB. O novo projeto suporta razões de conversão de 1:24 até 24:1. A melhor solução alternativa é o chip SRC4194 da Texas Instruments, que suporta entre 1:16 e 16:1. O projeto também suporta dezenas ou centenas de canais, utilizando multiplexagem por divisão de tempo; as outras soluções tipicamente suportam oito canais, e o CWda52 precisa de replicar a sua unidade stereo para suportar mais canais. Consequentemente, a utilização de recursos por canal é extremamente competitiva. O tempo de sincronização é 20 ms, que é uma ordem de grandeza inferior a qualquer outra alternativa. A variação da fase após reset, uma característica importante omitida em soluções alternativas, é inferior a uma amostra de saída.

**Palavras-chave:** Conversor de Frequências de Amostragem, Processamento Digital de Sinal, FPGA, Filtro Digital

#### Abstract

This thesis proposes a new design of a new 24-bit or less multi-channel Asynchronous Sample Rate Converter, with the following specification: (1) total harmonic distortion plus noise ratio (THD+N) of -130 dB or less; (2) supported conversion ratios from 1:24 to 24:1; hundreds of audio channels; (3) synchronisation time of less than 200 ms; (4) variation of the phase between input and output of less than one output sample after a reset; (5) resource consumption per channel similar to the CWda52, or less.

All objectives have been met, and hundreds of tests have been applied to the new design, which achieves a THD+N from a minimum of  $-143 \, dB$  to a maximum of  $-136 \, dB$  for a total of 121 tests, with an average of approximately  $-140 \, dB$ . The new design supports conversion ratios range from 1:24 to 24:1. The best alternative solution is the Texas Instruments SRC4194 chip, which supports a range from to 1:16 to 16:1. It can support tens or hundreds of channels using time division multiplexing; the other solutions typically support eight channels, and the CWda52, the main competitor to this approach, needs to replicate its stereo unit to handle more channels. Consequently, the resource usage per channel of this approach is extremely competitive. The synchronisation time is  $20 \, \text{ms}$ , which is one order of magnitude lower than any other alternative. The variation of the phase after reset, an important characteristic omitted in the alternative solutions, is less than one output sample.

### Keywords:Asynchronous Sample Rate Converter, Digital Signal Processing, FPGA, Digital Filter

# Contents

|   | Ackr  | nowledą  | gments                                                   | v    |  |  |  |

|---|-------|----------|----------------------------------------------------------|------|--|--|--|

|   | Res   | umo .    |                                                          | vii  |  |  |  |

|   | Abst  | tract .  |                                                          | ix   |  |  |  |

|   | List  | of Table | es                                                       | xv   |  |  |  |

|   | List  | of Figu  | res                                                      | xvii |  |  |  |

|   | List  | of Acro  | nyms                                                     | xix  |  |  |  |

| 1 | Intro | oductio  | on                                                       | 1    |  |  |  |

|   | 1.1   | Topic    | Overview                                                 | 1    |  |  |  |

|   | 1.2   | Motiva   | ation                                                    | 2    |  |  |  |

|   | 1.3   | Object   | tives                                                    | 2    |  |  |  |

|   | 1.4   | Thesis   | s Outline                                                | 3    |  |  |  |

| 2 | Asy   | nchron   | nous Sample Rate Converter Theory                        | 5    |  |  |  |

|   | 2.1   | Samp     | le Rate Converter's Structure                            | 5    |  |  |  |

|   | 2.2   | Interp   | olation/Decimation Filter As A Fractional Delay Filter   | 7    |  |  |  |

| 3 | Prev  | /ious V  | Vork                                                     | 11   |  |  |  |

|   | 3.1   | Impler   | mentation of the Interpolation/Decimation Filter         | 11   |  |  |  |

|   |       | 3.1.1    | Direct Filtering Using a Multiply-Accumulate Unit (MACC) | 11   |  |  |  |

|   |       | 3.1.2    | Cascaded Integrator Comb Filters (CIC)                   | 12   |  |  |  |

|   |       | 3.1.3    | Approximation By Piece-wise Quadratic Function           | 13   |  |  |  |

|   |       | 3.1.4    | Farrow Structure                                         | 15   |  |  |  |

|   | 3.2   | Impler   | mentation Of The Sample Rate Conversion Ratio Estimator  | 16   |  |  |  |

|   |       | 3.2.1    | Period Measurement And Averaging                         | 17   |  |  |  |

|   |       | 3.2.2    | Digital Phase Locked Loop As Frequency Tracker           | 18   |  |  |  |

| 4 | Prop  | oosed    | Design                                                   | 21   |  |  |  |

|   | 4.1   | Data N   | Memory                                                   | 23   |  |  |  |

|   | 4.2   | Ratio    | -                                                        |      |  |  |  |

|   |       |          |                                                          |      |  |  |  |

|   |       | 4.2.1    | Initial Approximation - Period Measurement and Averaging | 25   |  |  |  |

|    |       | 4.2.3       | Ratio Est   | imator Contr   | ol Unit . |         |        |        | <br> | <br> |     |  |     | 28              |

|----|-------|-------------|-------------|----------------|-----------|---------|--------|--------|------|------|-----|--|-----|-----------------|

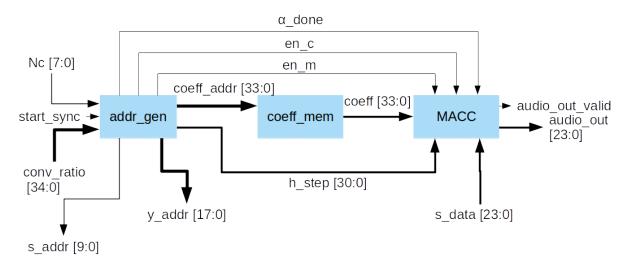

|    | 4.3   | 3 Resampler |             |                |           |         |        |        | 32   |      |     |  |     |                 |

|    |       | 4.3.1       | Address     | Generator .    |           |         |        |        | <br> | <br> |     |  |     | 32              |

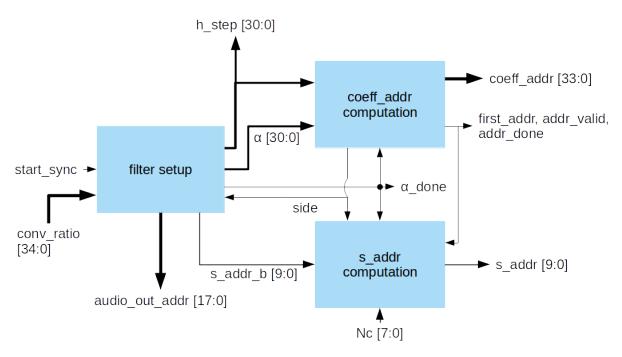

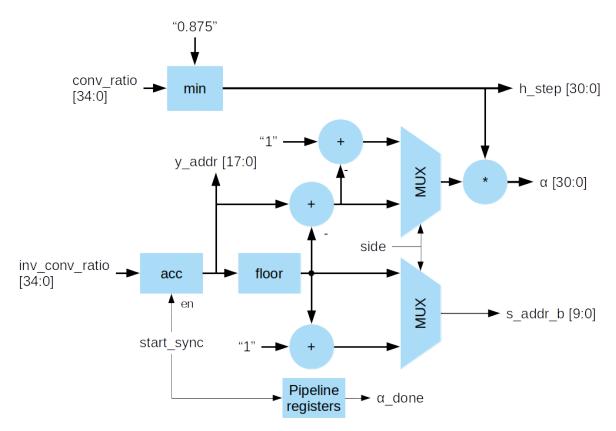

|    |       |             | 4.3.1.1     | Filter Setup   |           |         |        |        | <br> | <br> |     |  |     | 33              |

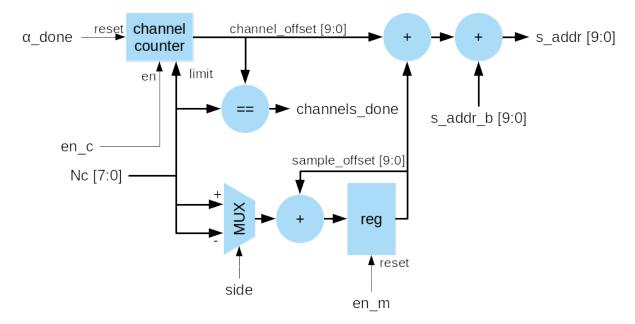

|    |       |             | 4.3.1.2     | Input Sample   | e Addres  | s Gene  | erator |        | <br> | <br> |     |  |     | 34              |

|    |       |             | 4.3.1.3     | Filter Coeffic | cients Ad | dress ( | Genera | ator . | <br> | <br> |     |  |     | 35              |

|    |       | 4.3.2       | Coefficier  | nt Memory      |           |         |        |        | <br> | <br> |     |  |     | 36              |

|    |       | 4.3.3       | Multiply-A  | Accumulator    |           |         |        |        | <br> | <br> |     |  |     | 37              |

|    | 4.4   | Pipelir     | ne Registe  | rs             |           |         |        |        | <br> | <br> |     |  |     | 37              |

| 5  | Test  | ing Sy      | stem        |                |           |         |        |        |      |      |     |  |     | 39              |

| •  | 5.1   |             |             | on and Analy   | sis       |         |        |        | <br> | <br> |     |  |     | 39              |

|    | ••••  | 5.1.1       |             | er Adjustmen   |           |         |        |        |      |      |     |  |     | 39              |

|    |       | 5.1.2       |             | efficients Ger |           |         |        |        |      |      |     |  |     | 41              |

|    |       | 5.1.3       |             | nal Generatio  |           |         |        |        |      |      |     |  |     | 42              |

|    |       | 5.1.4       |             | ignal Analysi  |           |         |        |        |      |      |     |  |     | 43              |

|    |       | 5.1.5       | -           | Resetting O    |           |         |        |        |      |      |     |  |     | 45              |

|    | 5.2   | IOB-S       |             | are Impleme    |           |         |        |        |      |      |     |  |     | 46              |

|    |       | 5.2.1       |             |                |           |         |        |        |      |      |     |  |     | 47              |

|    |       |             |             | UART           |           |         |        |        |      |      |     |  |     | 48              |

|    |       |             | 5.2.1.2     | Ethernet .     |           |         |        |        | <br> | <br> |     |  |     | 48              |

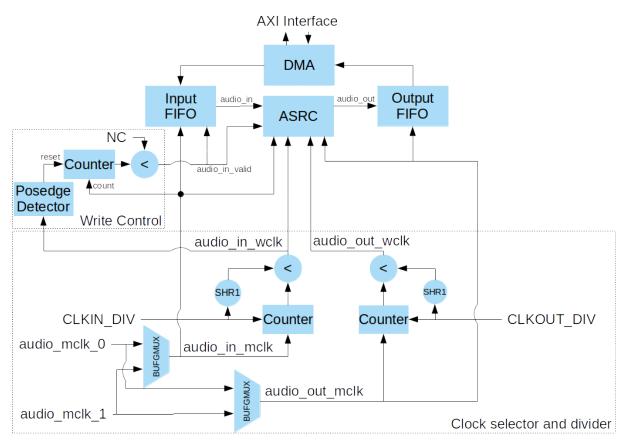

|    |       |             | 5.2.1.3     | ASRC's Wra     |           |         |        |        | <br> | <br> |     |  |     | 49              |

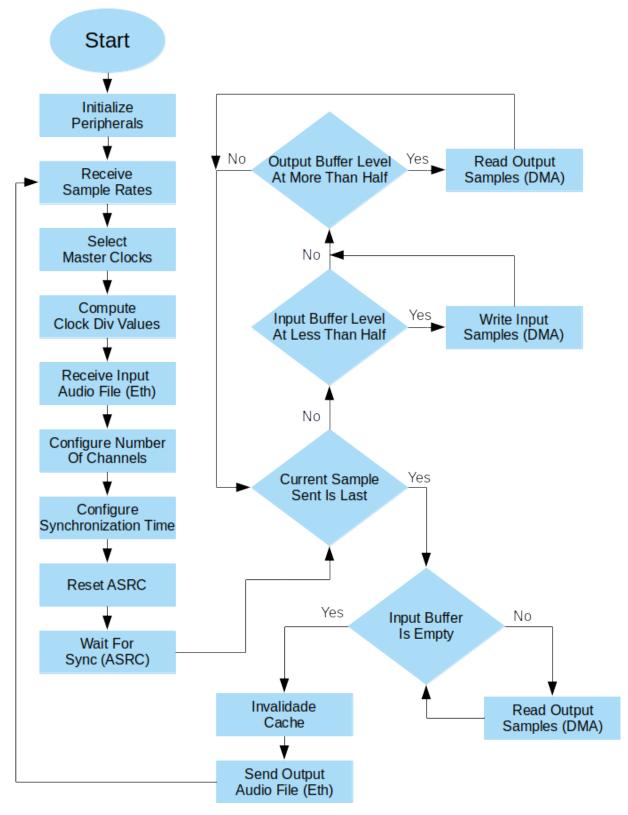

|    |       | 5.2.2       | Firmware    |                |           |         |        |        | <br> | <br> |     |  |     | 53              |

| 6  | Res   | ults        |             |                |           |         |        |        |      |      |     |  |     | 55              |

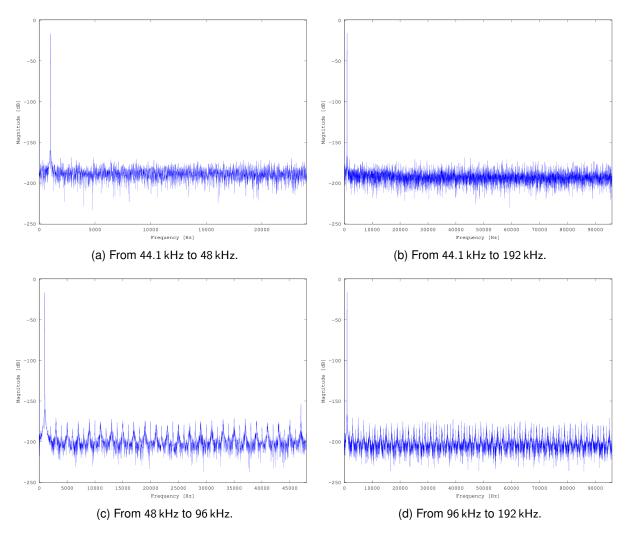

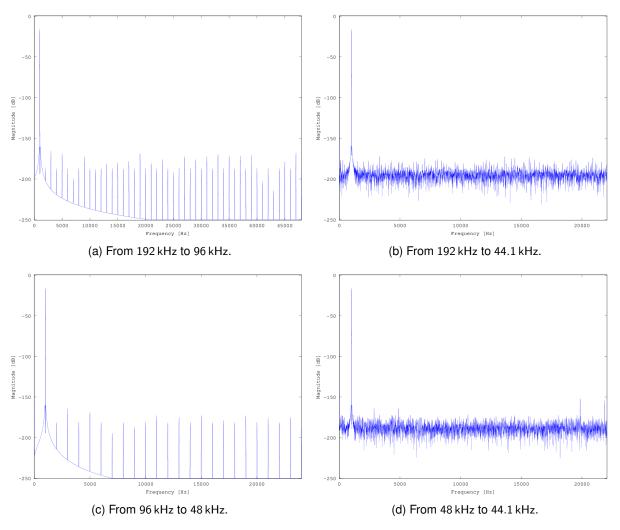

| •  | 6.1   |             | ourier Trar | nsform Setup   | )         |         |        |        | <br> | <br> |     |  |     | 55              |

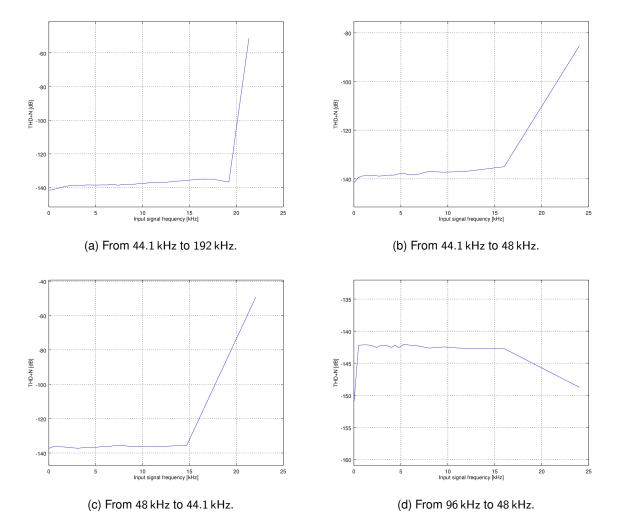

|    | 6.2   |             |             | Distortion Plu |           |         |        |        |      |      |     |  |     | 58              |

|    | 6.3   |             |             | onse           |           |         |        |        |      |      |     |  |     | 61              |

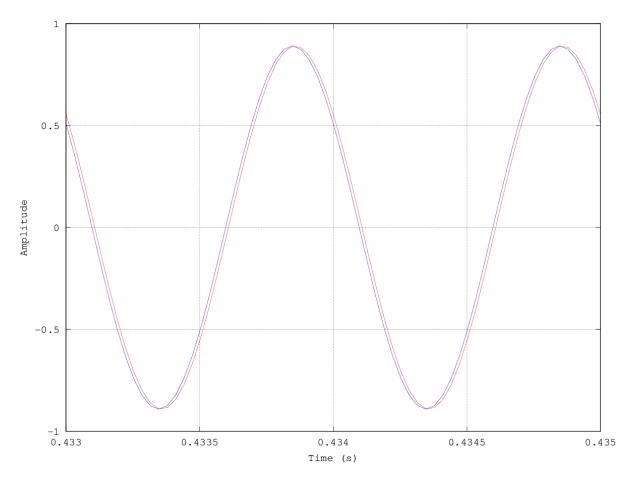

|    | 6.4   | •           |             | e After Rese   |           |         |        |        |      |      |     |  |     | 61              |

|    | 6.5   |             |             | ASRC           |           |         |        |        |      |      |     |  |     | 63              |

|    | 6.6   |             | -           | Usage          |           |         |        |        |      |      |     |  |     | 64              |

|    | 6.7   |             |             | Usage          |           |         |        |        |      |      |     |  |     | 66              |

|    | 6.8   |             |             | upport and L   |           |         |        |        |      |      |     |  |     | 67              |

| 7  | Con   | clusio      | ne          |                |           |         |        |        |      |      |     |  |     | 69              |

| '  | 7.1   |             |             |                |           |         |        |        |      |      |     |  |     | <b>09</b><br>70 |

|    |       |             |             |                |           |         |        |        |      |      |     |  |     | 70              |

|    | 1.2   | ruture      | , WUIN      |                |           |         |        |        | <br> | <br> | • • |  | ••• | 11              |

| Bi | bliog | raphy       |             |                |           |         |        |        |      |      |     |  |     | 73              |

| Α | Full Test Results |                                        |      |  |  |  |  |  |  |

|---|-------------------|----------------------------------------|------|--|--|--|--|--|--|

|   | A.1               | THD+N                                  | A.1  |  |  |  |  |  |  |

|   | A.2               | Group Delay After Reset                | A.3  |  |  |  |  |  |  |

|   | A.3               | THD+N With Varying Input Frequency     | A.6  |  |  |  |  |  |  |

|   | A.4               | Frequency Response                     | A.8  |  |  |  |  |  |  |

|   | A.5               | THD+N With Varying Input Magnitude     | A.10 |  |  |  |  |  |  |

|   | A.6               | Magnitude With Varying Input Magnitude | A.12 |  |  |  |  |  |  |

# **List of Tables**

| Interface signals.                                                         | 22                   |

|----------------------------------------------------------------------------|----------------------|

| Synthesis Parameters                                                       | 22                   |

| Conversion ratio estimator FSM output signals per state                    | 31                   |

|                                                                            | 47                   |

|                                                                            |                      |

| CPU native slave interface signals                                         | 48                   |

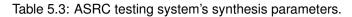

| ASRC testing system's synthesis parameters                                 | 50                   |

| Software accessible registers for the ASRC.                                | 51                   |

| Software accessible registers for the input and output buffers             | 52                   |

| Software accessible registers for the DMA.                                 | 52                   |

| Commonly used sample rates in audio applications and their particular uses | 58                   |

| Total harmonic distortion+noise ratio for some conversions                 | 58                   |

| Group delay of some conversions.                                           | 62                   |

| Results of linear regression of some conversions                           | 64                   |

| Resource utilization on a XCKU040 (hierarchical representation)            | 65                   |

| Resource utilization on a XC7A35 (left) and Cyclone V GT (right)           | 65                   |

| ASIC resource usage for the ASRC                                           | 66                   |

| ASIC resource usage for the CWda52 with two audio channels                 | 66                   |

| Total harmonic distortion+noise ratio for every tested conversion          | A.3                  |

| Group delay for every tested conversion                                    | A.5                  |

|                                                                            | Synthesis Parameters |

# **List of Figures**

| 2.1  | Analog interpretation of a sample rate converter                                          | 5  |

|------|-------------------------------------------------------------------------------------------|----|

| 2.2  | Classic digital sample rate conversion algorithm by factor L/M $\ldots$                   | 6  |

| 2.3  | Graphical representation of $h[n]$ for $	au_d = 0$                                        | 8  |

| 2.4  | Illustration of upsampling (3:4) used to determine the output sample at $n = 4.5$         | 9  |

| 2.5  | Illustration of downsampling (4:3) used to determine the output sample at n = 8 $\dots$ . | 10 |

| 3.1  | MACC filter block diagram.                                                                | 12 |

| 3.2  | Example of cascaded integrator comb filter structure, used as an interpolation filter     | 13 |

| 3.3  | Example of a piece-wise kernel filter structure                                           | 14 |

| 3.4  | Example of optimized kernel filter structure                                              | 15 |

| 3.5  | Example of farrow structure, optimized for variable fractional delay                      | 16 |

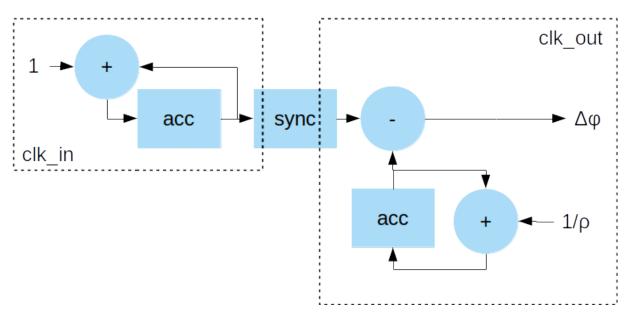

| 3.6  | Period measurement and $\rho$ computation using a PLL                                     | 17 |

| 3.7  | Period measurement and $\rho$ computation using a divider                                 | 17 |

| 3.8  | DPLL phase detector block diagram.                                                        | 19 |

| 3.9  | DPLL loop filter and VCO block diagram.                                                   | 19 |

| 4.1  | Symbol and interface diagram.                                                             | 21 |

| 4.2  | Asynchronous sample rate converter top block diagram.                                     | 23 |

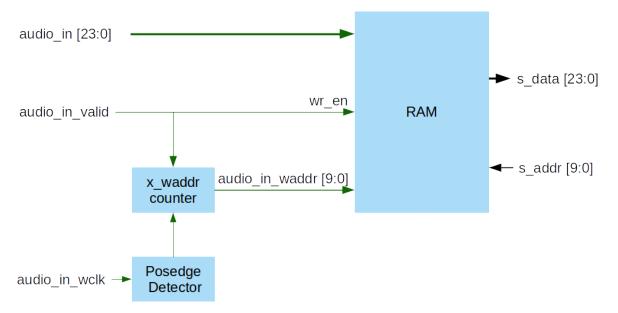

| 4.3  | Data memory module block diagram.                                                         | 24 |

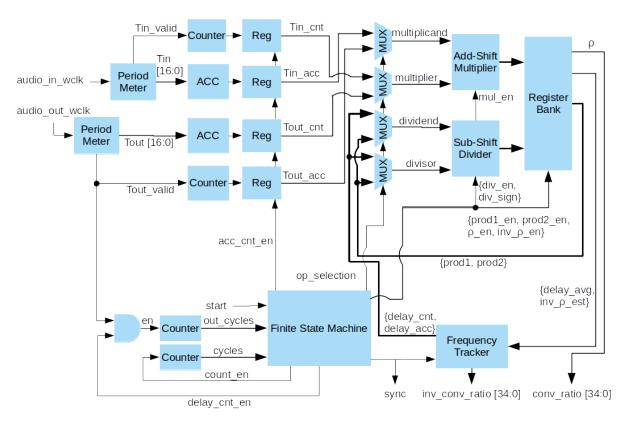

| 4.4  | Ratio Estimator module block diagram.                                                     | 25 |

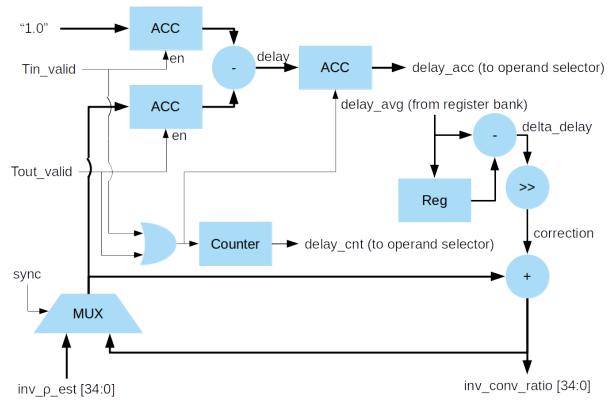

| 4.5  | Frequency Tracker module block diagram.                                                   | 27 |

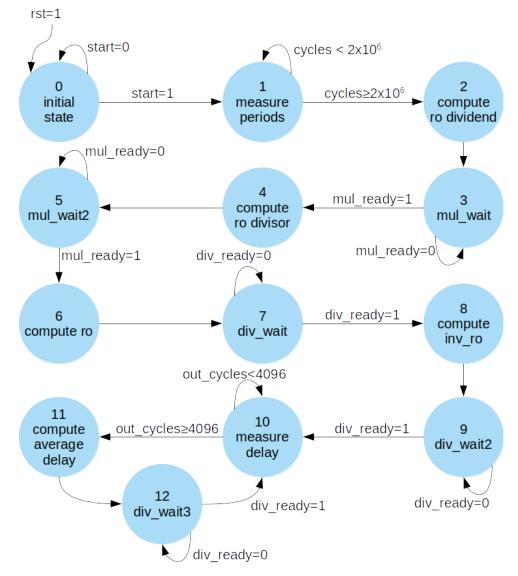

| 4.6  | Ratio Estimator FSM state diagram.                                                        | 30 |

| 4.7  | Resampler block diagram                                                                   | 32 |

| 4.8  | Address generator block diagram.                                                          | 33 |

| 4.9  | Output sample address, $h\_step$ and $\alpha$ computation submodule block diagram         | 34 |

| 4.10 | Input sample address computation submodule block diagram                                  | 35 |

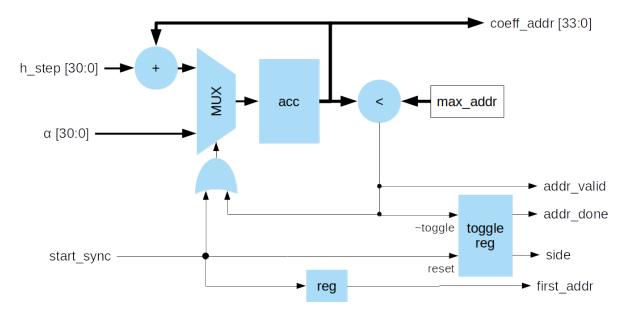

| 4.11 | Coefficient address computation submodule block diagram.                                  | 36 |

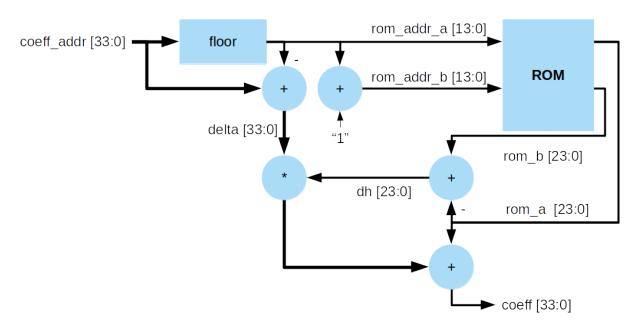

| 4.12 | Coefficient memory submodule block diagram.                                               | 36 |

| 4.13 | MACC block diagram.                                                                       | 37 |

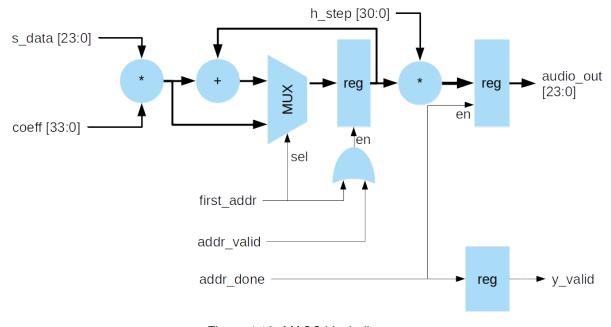

| 5.1  | IOB-SoC block diagram.                                                                    | 46 |

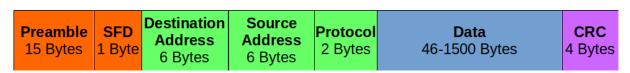

| 5.2  | Ethernet data frame format.                                                               | 48 |

| 5.3 | ASRC's wrapper block diagram                                                             | 50   |

|-----|------------------------------------------------------------------------------------------|------|

| 5.4 | ASRC testing firmware flowchart                                                          | 54   |

| 6.1 | Fast-Fourier transform of upsampled signals.                                             | 56   |

| 6.2 | Fast-Fourier transform of downsampled signals                                            | 57   |

| 6.3 | THD+N of the ASRC's output for fixed conversions and varying input frequency             | 59   |

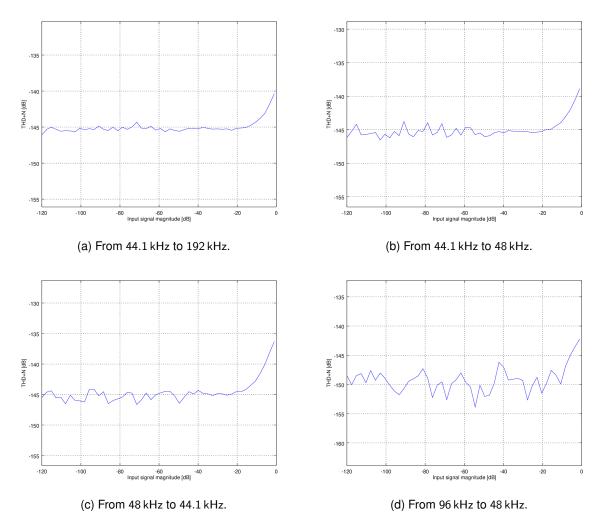

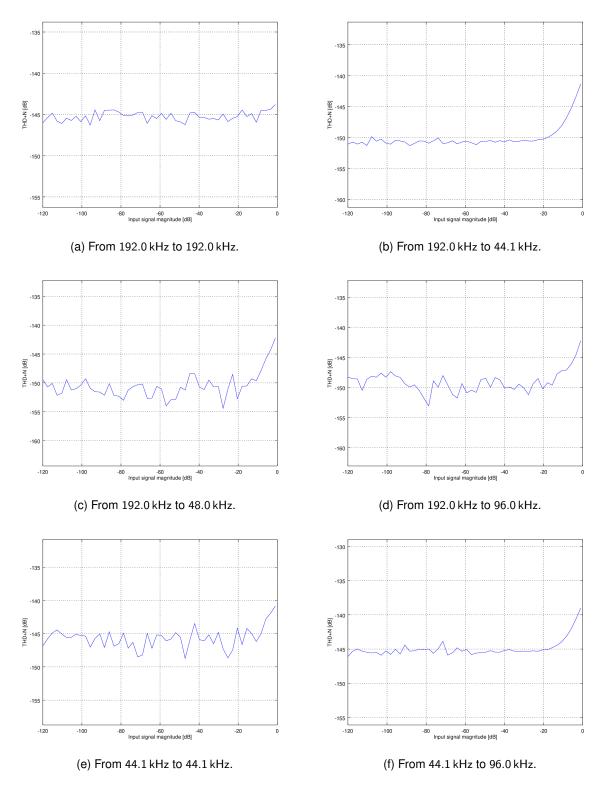

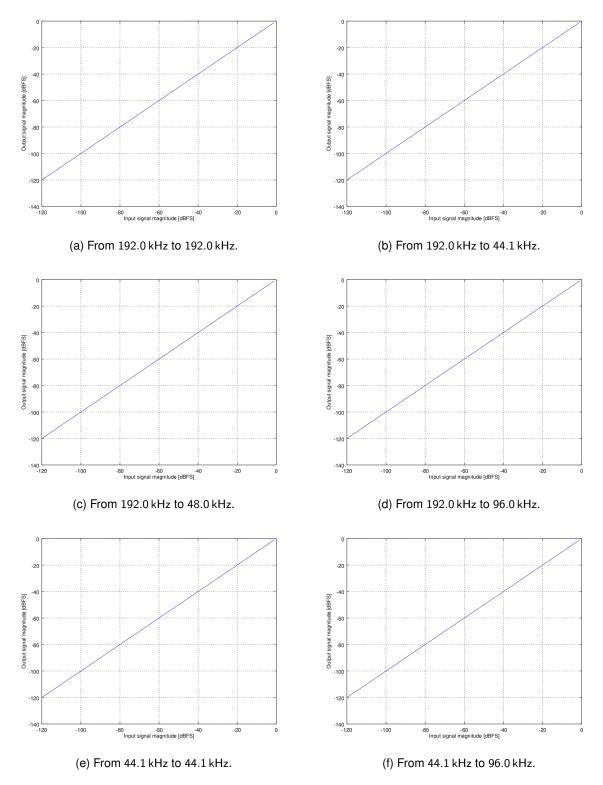

| 6.4 | THD+N of the ASRC output for fixed conversions while varying the input magnitude         | 60   |

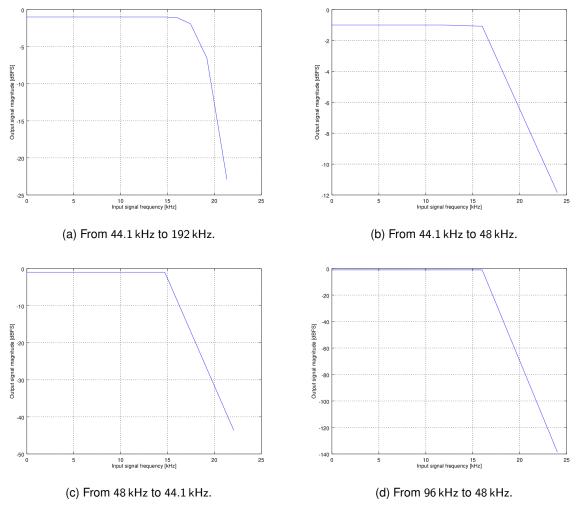

| 6.5 | Frequency response of the ASRC for a few conversions.                                    | 61   |

| 6.6 | Output signal before (blue) and after (red) reset for a conversion from 48 kHz to 32 kHz | 62   |

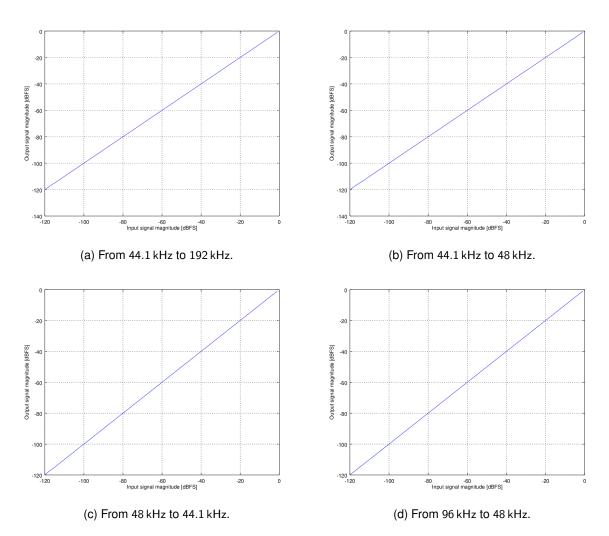

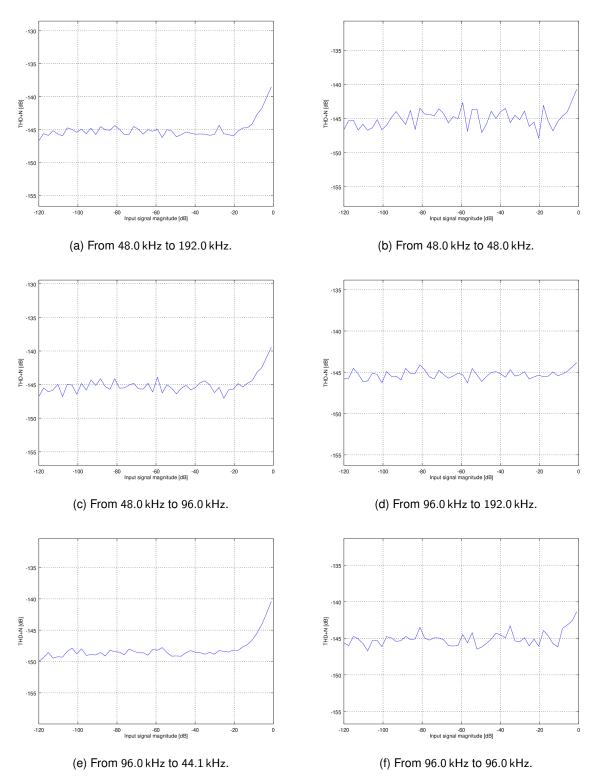

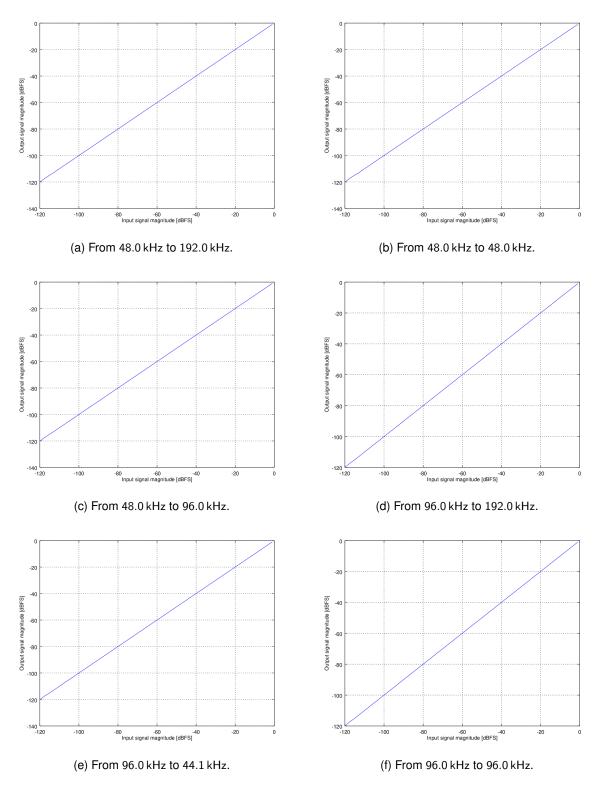

| 6.7 | Magnitude of the ASRC's output for fixed conversions and variable input magnitude        | 63   |

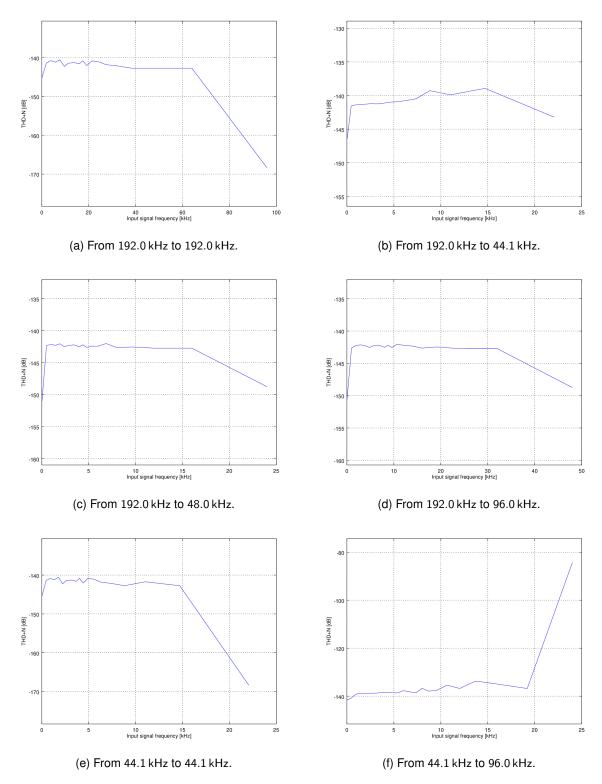

| A.1 | THD+N of the ASRC's output for fixed conversions and varying input frequency (Full re-   |      |

|     | sults - 1/2)                                                                             | A.6  |

| A.2 | THD+N of the ASRC's output for fixed conversions and varying input frequency (Full re-   |      |

|     | sults - 2/2)                                                                             | A.7  |

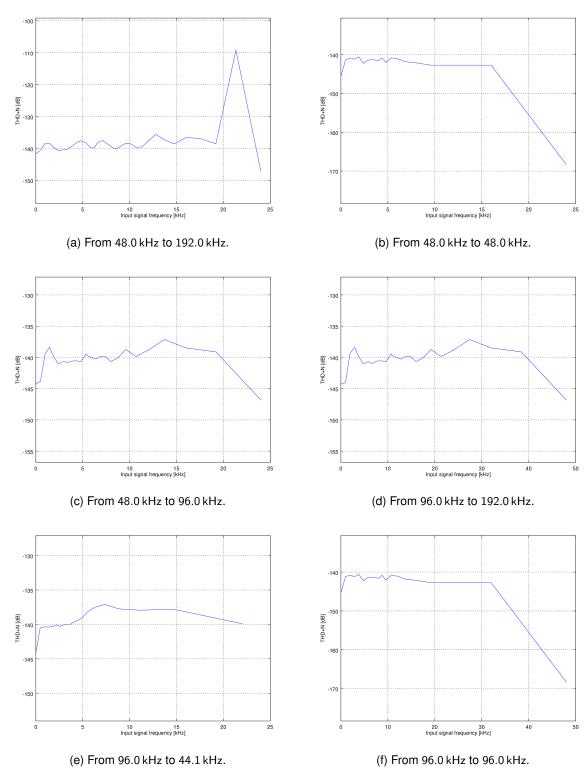

| A.3 | Frequency response (Full results - 1/2).                                                 | A.8  |

| A.4 | Frequency response (Full results - 2/2).                                                 | A.9  |

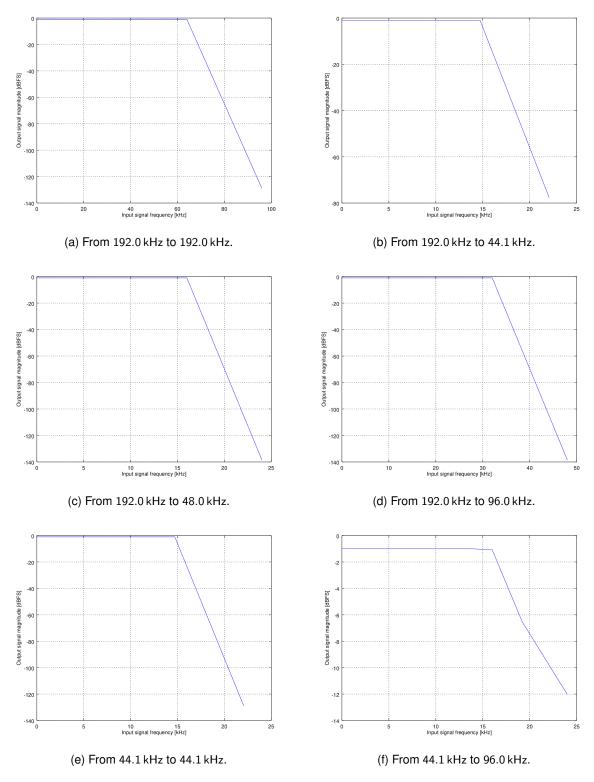

| A.5 | THD+N of the ASRC's output for fixed conversions and varying input magnitude (Full       |      |

|     | results - 1/2)                                                                           | A.10 |

| A.6 | THD+N of the ASRC's output for fixed conversions and varying input magnitude (Full       |      |

|     | results - 2/2)                                                                           | A.11 |

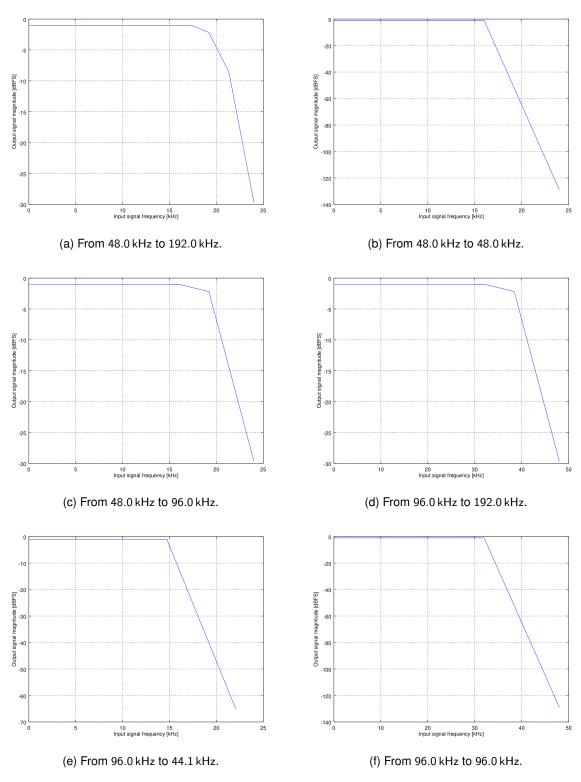

| A.7 | Magnitude of the ASRC's output for fixed conversions and varying input magnitude (Full   |      |

|     | results - 1/2)                                                                           | A.12 |

| A.8 | Magnitude of the ASRC's output for fixed conversions and varying input magnitude (Full   |      |

|     | results - 2/2)                                                                           | A.13 |

#### List of Acronyms

AES Audio Engineering Society

**ASIC** Application Specific Integrated Circuits

ASRC Asynchronous Sample Rate Converter

- **CDC** Clock Domain Crossing

- **CIC** Cascaded Integrator Comb

- **CPU** Central Processing Unit

- **CRC** Cyclic Redundancy Check

- **DDR** Double Data Rate

- DMA Direct Memory Access

- **DPLL** Digital Phase Locked Loop

- **DSP** Digital Signal Processor

- FIFO First In, First Out

- FIR Finite Impulse Response

- FPGA Field Programmable Gate Array

- FSM Finite State Machine

- HDL Hardware Description Language

- IC Integrated Circuit

- IP Intellectual Property

- LPF Low Pass Filter

- LUT Lookup Table

- MACC Multiply-Accumulate

- **MIG** Memory Interface Generator

- MMCM Mixed-Mode Clock Manager

- PLL Phase Locked Loop

- RAM Random Access Memory

- ROM Read-Only Memory

- **RTL** Register Transfer Level

- SFD Start Frame Delimiter

- SRAM Static Random Access Memory

- SSRC Synchronous Sample Rate Converter

- SoC System-on-a-Chip

- TDM Time Division Multiplexed

- THDN Total Harmonic Distortion Plus Noise

- **UART** Universal Asynchronous Receiver-Transmitter

- **USB** Universal Serial Bus

- VCO Voltage Controlled Oscillator

## **Chapter 1**

# Introduction

#### 1.1 Topic Overview

In 1977, with the growing popularity of audio interfaces, the Audio Engineering Society (AES) founded the AES Digital Audio Standards Committee, creating some of the most used audio standards to this day. One of the most popular standards, the AES3 digital audio interface is still used in current audio equipment, like microphones and speakers with XLR connectors.

Since then, there has been a significant rise in AES standards, many of them demanding the conversion of an audio signal's sample rate. One of the classic examples is the conversion from CD quality with a sampling rate  $F_s = 44.1$  kHz to DVD quality with  $F_s = 48$  kHz. Consequently, there is a great demand for sample rate converters, both in software algorithms and hardware designs.

To answer this need, some integrated circuit manufacturers developed multiple sample rate converter ers with varied specifications. The AD1896 [1], for instance, is an asynchronous sample rate converter made by Analog Devices, in 2003. It supports a stereo (2 channel) audio signal and converts its sampling rate from 7.75:1 to 1:8 ratios, with a Total Harmonic Distortion Plus Noise (THD+N) ratio of around –125 dB. Another example is the SRC4194 [2], manufactured by Texas Instruments since 2004, supporting up to 4 channel inputs and a wider sampling rate ratio, ranging from 16:1 to 1:16 ratios, with a THD+N of around –140 dB.

The implementation as Intellectual Property (IP) is quintessential for the development of embedded audio systems, as it allows one to synthesise a new core with different configurations, fulfilling different specifications, in a faster and cheaper way. Furthermore, one can implement the IP directly into the system, without the need to develop a new core specifically for the system or to externally connect a discrete core to the system.

The first IP (IP) was developed by Coreworks, an IP design company, and called the CWda52 [3]. It supports up to 8 channels and converts sampling rates between 8 kHz and 192 kHz, with ratios from 7:1 to 1:7. The THD+N of the converted signal is around -120 dB. The core uses around 700 Slices when implemented on a *Xilinx Kintex-7* Field Programmable Gate Array (FPGA) board as a stereo converter. This IP has some limitations that can be improved: Firstly, the configurable nature of the IP should allow

it to support more channels at the cost of more resources if needed. The THD+N of the output can be further reduced to make the core more competitive with its Integrated Circuit (IC) counterparts. The same reason justifies the improvement of the limit imposed on the ratios. Finally, as the core replicates itself for each pair of channels, the resource usage per channel can be further reduced.

This work started in a summer internship at IObundle Lda, another IP design company, and has been carried out in a double academic and industrial context since then. At the beginning of the work, a preliminary document describing the ASRC, an Octave model and a non-functional Verilog were available. These materials made it possible to learn the sample rate conversion algorithm and have a starting point.

The resampler was fixed, and its THD+N was reduced to near the theoretical limit of -146dB for 24-bit audio. The resampler was also used to develop a Synchronous Sample Rate Converter (SSRC) core in parallel and outside the scope of this work. Then the conversion ratio estimator module was developed from scratch, which involves very accurate digital signal processing in a 3-clock domain implementation, requiring synchroniser circuits and a comprehensive test environment.

#### 1.2 Motivation

While there are currently hardware implementations of asynchronous sample rate converters, most of them are implemented as ICs, while IP implementations are few and have limited specifications compared to their IC counterparts. This context makes it difficult for companies that manufacture multi-media devices to integrate a sample rate converter IP.

The overall growth of the market for embedded audio systems, with many requiring sample rate conversion, motivates the development of a better sample rate converter IP core. The only existing IP implementation of an ASRC, the CWda52, shows several limitations, so it makes sense to develop an improved IP core, competing with both the existing IP core and the IC counterparts.

#### 1.3 Objectives

The main objective of this work is to design an asynchronous sample rate converter (ASRC) IP core using the Verilog hardware description language. The core should meet the following specifications:

- Support for up to 24-bit samples.

- Conversion from and to any sample rate, in the range between 8 kHz and 192 kHz.

- Capability of converting multiple channels, limited by the operation clock frequencies.

- Output THD+N equal or lower than -130 dB (for 24-bit samples).

- Synchronization time equal or lower than 200 ms.

- Variation of phase between input and output after a reset of less than one output sample.

• Resource consumption per channel of the same order as the CWda52, or lower.

#### 1.4 Thesis Outline

This document is composed of 6 more chapters. The second chapter explains the sample rate conversion algorithm. The third chapter presents some sample rate converter designs, along with their advantages and disadvantages. In the fourth chapter, the hardware design of the core is described, including architecture, interfaces and sub-modules. The fourth chapter presents the process of testing and integrating the ASRC into a system-on-a-chip (SoC). The fifth chapter shows and analyses the results obtained from the tests performed. In the sixth and final chapter, some conclusions of the work performed are drawn, as the final product is compared to its IC counterparts, and some possible future work is proposed.

## Chapter 2

# Asynchronous Sample Rate Converter Theory

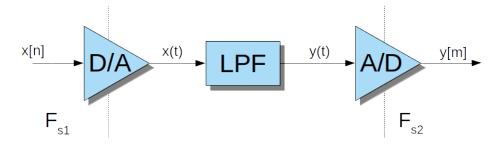

An ideal Asynchronous Sample Rate Converter (ASRC) is able to convert the sample rate of an input audio signal to a desired output sample rate without any loss of signal quality. As opposed to a synchronous sample rate converter, the ASRC also needs to measure the value of the input and output sample rates continuously to compute the conversion ratio. The ideal ASRC converts a discrete time input signal x[n], sampled at a rate  $F_{s1}$ , to a continuous time signal x(t), using a reconstruction filter. The signal is then filtered by an anti-aliasing filter which ensures that its output y(t) has no components which would violate Nyquist's law. Signal y(t) is then converted to a discrete time signal y[m], sampled at the desired output rate  $F_{s2}$  [4].

A block diagram of this model is shown in Fig. 2.1. Note that the reconstruction filter and anti-aliasing filters can be combined in a single Low Pass Filter (LPF).

Figure 2.1: Analog interpretation of a sample rate converter

#### 2.1 Sample Rate Converter's Structure

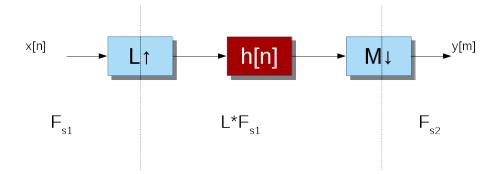

One of the challenges of creating a purely digital solution is the design of the LPF digital filter, which must be both accurate and efficient. The classical approach to the problem consists in upsampling the

signal by a factor *L* (interpolation), doing the processing at the frequency  $L \times F_{s1}$ , and downsampling the result by a factor *M* (decimation). This is a means to emulate a discrete to continuous and continuous to discrete signal conversion [5]. A simple block design of the algorithm is shown in Fig. 2.2.

Figure 2.2: Classic digital sample rate conversion algorithm by factor L/M

In practice, an input signal x[n], sampled at frequency  $F_{s1}$  is upsampled by insertion of L-1 samples with value zero between two consecutive input samples. The resultant signal is then inserted into a low pass filter h[n], which will interpolate the inserted samples and avoid both aliasing, caused by downsampling, and imaging, caused by upsampling. Finally, the output of the filter is downsampled by taking only every M-th sample for the output signal y[m]. The relationship between L and M is such that

$$F_{s2} = \frac{L}{M} F_{s1}.$$

(2.1)

To avoid the use of multiple frequencies in the computations, one defines a normalized frequency  $\Omega$ , given by

$$\Omega = \frac{2\pi f}{Lf_{s1}} [rad]. \tag{2.2}$$

Regarding the filter h[n], its cutoff frequency depends on the relationship described in Equation (2.1). In the upsampling case  $(L \ge M)$ , one needs to remove the resultant spectral images, using a filter with a normalized cutoff frequency ( $\Omega_c \le 0.5\pi/L$ ). In the case of downsampling (L < M), one needs to filter signal frequencies that would cause aliasing, leading to a filter with a normalized cutoff frequency ( $\Omega_c \le 0.5\pi/M$ ). By combining these two conditions, the filter's cutoff frequency is given by

$$\Omega_c = min(\frac{\pi}{2L}, \frac{\pi}{2M})[rad].$$

(2.3)

Note that the normalization considered is in relation to the upsampled frequency:

In the current state-of-the-art, this algorithm is the basis of most synchronous and asynchronous sample rate converters.

For conversions which use small values of L and M the computational effort is modest. However, if the conversion involves sampling rates with a small difference, the factors L and M will increase significantly. As a consequence the computational cost of the conversion increase drastically, only to have

most of the computed samples discarded. Note that, in this case, a small normalised cutoff frequency must be used for the filter.

Furthermore, one needs to design the filter to both remove aliasing and interpolate the L-1 inserted samples. This is why the design of the filter h[n] is the main challenge of this architecture. The solution presented in this thesis is based on the use of a fractional delay filter.

Additionally, for asynchronous sample rate converters, the filter is not only time-varying, but also varies with the sample rate ratio. This means that one needs to define a structure that computes the ratio and adapts the filter. For synchronous sample rate converters, the ratio stays constant. I this case the filter is predictable, and it is possible to trade off storage space for computation time, by pre-computing a finite set of filters [6].

#### 2.2 Interpolation/Decimation Filter As A Fractional Delay Filter

An efficient way of obtaining an interpolated value of a sample is to consider that the output samples needed correspond to the input samples, delayed or advanced by a certain value. Considering a discrete-time signal y[n], obtained by delaying a signal x[n],

$$y[n] = x[n - \tau_d] = x[n] * h_d[n],$$

(2.4)

where  $\tau_d$  is the normalized delay. For continuous signals, a time shift in the frequency domain can be expressed as a product between an input  $X(e^{j\omega})$  and a filter  $H(e^{j\omega})$ ,

$$Y(e^{j\omega}) = H(e^{j\omega})X(e^{j\omega}), \tag{2.5}$$

where

$$H(e^{j\omega}) = e^{-j\omega\tau_d}.$$

(2.6)

By analysis of Equation (2.6), it is possible to note that a delay filter is an all-pass filter with unitary gain and linear phase. However this is only the case for a continuous time domain x(t) signal. For the digital signal x[n], which needs to be reconstructed and aliasing-free, a low-pass filter with a cutoff frequency defined by Equation (2.3) is needed. Since both the reconstruction and anti-aliasing filters are linear systems, they can be combined together in a single filter whose frequency response  $H_d(e^{j\Omega})$  is the product of the frequency responses of the two filters:

$$H_d(e^{j\Omega}) = \begin{cases} 1, |\Omega| < \Omega_c \\ 0, otherwise \end{cases}$$

(2.7)

To obtain the impulse response of filter h[n], defined in Equation (2.4), the inverse discrete-time Fourier transform (IDTFT) of  $H_d(e^{j\omega})$  is performed.

$$h[n] = IDTFT(H_d(e^{j\omega})) = \frac{1}{2\pi} \int_{-\pi}^{\pi} e^{-j\Omega\tau_d} e^{j\Omega n} d\Omega.$$

(2.8)

Since the integrated function is non-zero only in the interval  $[-\Omega_c, \Omega_c]$  and  $e^{-j\Omega\tau_d}e^{j\Omega n} = e^{j\Omega(n-\tau_d)}$ , the integral can be solved yielding

$$h[n] = \frac{\sin(\Omega_c(n-\tau_d))}{\pi(n-\tau_d)}.$$

(2.9)

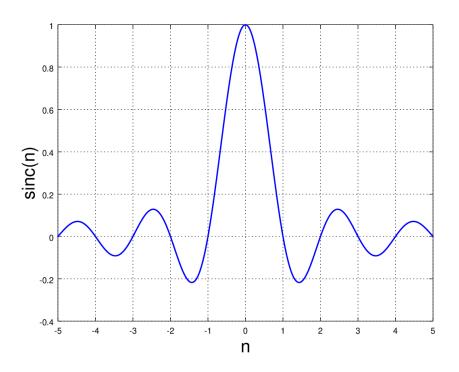

The impulse response of the filter h[n] is then defined by Equation (2.10), which is the normalized *sinc* function.

$$h[n] = \frac{\Omega_c}{\pi} sinc \left[ \frac{\Omega_c}{\pi} (n - \tau_d) \right].$$

(2.10)

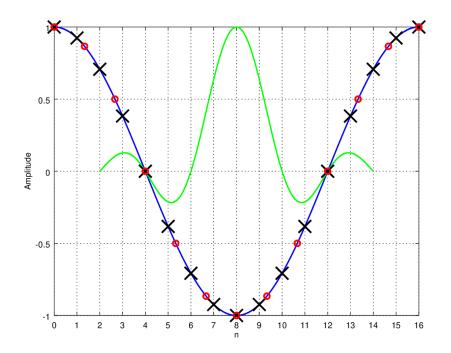

Fig. 2.3 represents the function for  $\tau_d = 0$ . Note that a variation of  $\tau_d$  is equivalent to a translation of the figure in the *n* (discrete time) axis. Furthermore, the cutoff frequency of the filer  $\Omega_c$  varies with the sample rate conversion ratio. By direct observation of the figure, it is possible to note that for integer values of  $\tau_d$ , h[n] = 0 for all samples except for  $n = \tau_d$  where h[n] = 1. This is the expected filter response for an integer delay. On the other hand, for a fractional value of  $\tau_d$ , h[n] is non-zero for all samples. For the ASRC algorithm,  $0 \le \tau_d \le 1$ , since the objective is to use the fractional delay filter as a way to obtain an interpolated sample using a finite number of input neighbor samples separated by an unitary normalized delay.

Figure 2.3: Graphical representation of h[n] for  $\tau_d = 0$

As this function is infinite and non-causal, an approximation must be done while retaining enough low-pass filtering capability to ensure quality, as explained in Section 2.1. This problem can be solved by

applying a window to the ideal filter h[n]. The choice of the format of the window and bandwidth have an influence not only on the quality of ASRC's output signal, but also on the complexity of the computations done.

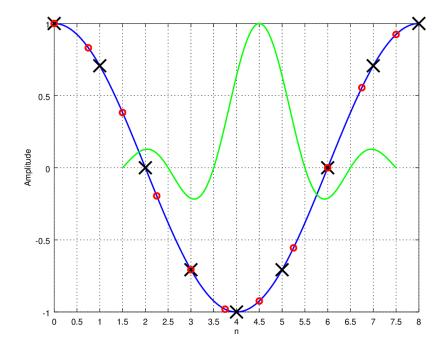

Using the truncation of the impulse response as an approximation technique, the resultant filter is a section of the sinc function which contains a certain number of zeroes. To exemplify, a filter with six zeroes is considered in Fig. 2.4, and Fig. 2.5.

Figure 2.4: Illustration of upsampling (3:4) used to determine the output sample at n = 4.5

In Fig. 2.4, the digital input signal, whose samples are represented by crosses, is plotted along its continuous time representation. To upsample the signal by a factor of 4/3, the output samples, represented by circles, need to be computed. To interpolate these signals, the filter approximation is applied, centering the window at the desired output sample, multiplying each input sample by the corresponding filter value, and accumulate all obtained values. By analysis of this illustration, it is possible to note that a larger upsampling factor will decrease the distance between the output samples. According to Equation (2.3), the normalized cutoff frequency of the filter is  $\frac{4}{3}/L$ . The filter is always the same in the upsampling case and its number of accumulations is the same as the number of zeroes in the truncated sinc function.

Fig. 2.5 is analogous to Fig. 2.4, representing downsampling by a factor of 4/3 instead. In this case, according to Equation (2.3), the cutoff frequency of the filter is given by  $\frac{3}{4}/M$ . The number of accumulations is now *M* times the number of zeroes in the truncated sinc function.

Regarding the approximation of the filter itself, there is a great variety of techniques used to obtain a fractional delay filter which minimizes the discretization error, ranging from applying a window to the

Figure 2.5: Illustration of downsampling (4:3) used to determine the output sample at n = 8

ideal filter to applying Lagrangian interpolation to compute an intermediate coefficient from a set of known filter samples. These and other methods are explained in detail in [7–10].

## **Chapter 3**

# **Previous Work**

With the knowledge that the sample rate converter can be implemented as a filter, as was explained in Chapter 2, multiple distinct implementations can be performed, leading to different results regarding output fidelity and resources usage. In this chapter, some designs proposed in previous works are shown and analyzed, regarding the implementation of the filter, as well as the implementation of the sample rate conversion ratio estimator.

#### 3.1 Implementation of the Interpolation/Decimation Filter

#### 3.1.1 Direct Filtering Using a Multiply-Accumulate Unit (MACC)

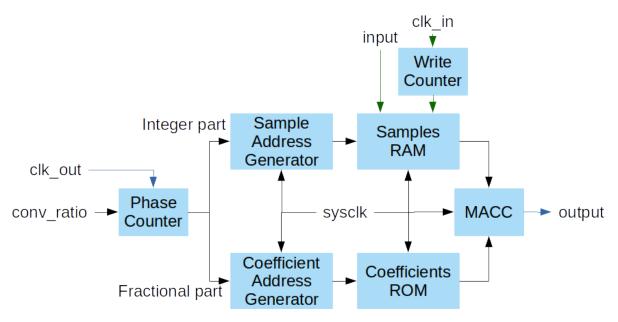

As was studied in Section 2.2, the output of the sample rate converter can be obtained by applying a low-pass filter to the input signal. As such, the most direct approach is to perform the direct computation of the discrete convolution between the filter and the samples, using two memories for the coefficients and samples, and a MACC unit for the computations [11]. A block diagram of the MACC unit is shown in Fig. 3.1.

In this implementation, an accumulator is used to generate the phase of the desired output samples, by accumulating the sample rate conversion ratio. The integer part of the accumulated value will correspond to the previous input sample that is closest in phase to the current output sample. The fractional part is the distance between the phase of the desired output sample and the closest input sample, and is used to select the starting point of the filter. Graphically, this selection is represented as centering the sinc to the closest input sample (as exemplified in Fig.2.4 and 2.5). It can also be interpreted as a polyphase filter [4].

After determining the starting values, both the coefficient and sample addresses decrement in equivalent values, obtaining the previous samples and respective coefficients. The output sample y[n], is obtained by

$$y[n] = \sum_{i=0}^{N} a_i x[n-i],$$

(3.1)

Figure 3.1: MACC filter block diagram.

where  $a_i$  are the coefficients of the filter and x[n-i] is the input sample at phase n-i.

It is important to note that the filter implemented by this method has a finite impulse response (FIR), which has a non-recursive structure. This is ideal, as FIR filters guarantee a linear phase, which is desired for audio applications.

This design has the advantage of being the easiest to implement, as well as being the one that uses the least amount of logic in comparison to the other implementations presented in this chapter, requiring only one MACC unit for the computations. However, it requires a large amount of filter coefficients, which, in hardware, results in high memory usage, an undesirable result. The problem can be solved by interpolating the filter's coefficients, leading to the use of some logic to reduce the amount of memory used, as some intermediate values do not need to be stored in it.

To guarantee that the sample rate converter supports multiple channels, the structure of the converter should be able to support the computation of multiple output samples. This can be done at the cost of hardware area, by having one output computation unit per channel, or at the cost of computation time, by having one unit computing multiple outputs sequentially.

#### 3.1.2 Cascaded Integrator Comb Filters (CIC)

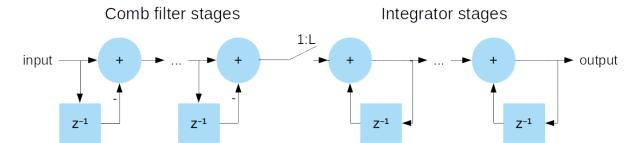

As was explained in Section 2.1, sample rate conversion can be interpreted as signal upsampling with interpolation, followed by downsampling with decimation. Furthermore, the algorithm can be implemented using FIR filters as shown in the previous section. One of the designs commonly used for this purpose is a Cascaded Integrator Comb filter (CIC) [12]. The filter, originally designed by Hogenauer [13], is based on the implementation of simple integrators and differentiators. CIC filters are obtained by combining adders and delay registers, which consumes a reduced amount of memory and has the great advantage of dispensing with multipliers, which can consume a great amount of hardware resources. Due to the fact that the CIC decimator has a symmetric structure in comparison to a

CIC interpolator, the combination of the two components leads to a highly efficient implementation in application specific integrated circuits (ASIC) and FPGA's. An interpolation filter using the CIC structure can be seen in Fig. 3.2. A decimation filter would have the same components, with the difference that the comb filters and integrator stages would swap positions.

Figure 3.2: Example of cascaded integrator comb filter structure, used as an interpolation filter

While for one CIC structure, the frequency response does not fulfill the requirements, this problem can be solved by cascading multiple interpolation and integration units [12], increasing the attenuation in the filter's stop-band. The implementation is elegant but has limited configurability, due to the fact that no coefficients are used, making it hard to adapt the filter to variations in the sample rates. Furthermore, this type of filter expects integer factors, which leads to the problem of making it able to convert fractional sample rate relations. Finally, this type of filter needs an oversampled signal to properly filter it, making it unusable for a sample rate converter without the use of another filter to obtain more samples.

#### 3.1.3 Approximation By Piece-wise Quadratic Function

As explained in Section 2.2, the impulse response of the filter is a *sinc* function, as expressed by Equation (2.10). In practice, the ideal filter impossible implement, due to its infinite number of taps and requirement to use future samples (non-causality).

The solution presented so far is to truncate and approximate the coefficients and delay the response to make it causal. Another way to address this problem is to split the sinc function into a piece-wise function, and approximate each piece by a quadratic function, leading to an interpolation filter which can be easily implemented [14, 15]. The approximation of the piece-wise sinc function h(x) into quadratic functions can be expressed as

$$h(t) = \begin{cases} a_{1,1}t^2 + b_{1,1}t + c_{1,1}, \left(0 \le |t| \le \frac{1}{N}\right) \\ \vdots \\ a_{1,n}t^2 + b_{1,n}t + c_{1,n}, \left(\frac{n-1}{N} \le |t| \le 1\right) \\ \vdots \\ a_{s,n}t^2 + b_{s,n}t + c_{s,n}, \left(s - 1 + \frac{n-1}{N} \le |t| \le s - 1 + \frac{n}{N}\right) \\ \vdots \\ a_{S,n}t^2 + b_{S,n}t + c_{S,n}, \left(S - 1 + \frac{n-1}{N} \le |t| \le S\right) \end{cases}$$

(3.2)

where N is the number of quadratic functions used to represent a piece-wise function, and S is the number of piece-wise functions of the kernel. This technique leads to the implementation presented in Fig. 3.3.

Figure 3.3: Example of a piece-wise kernel filter structure

The design can be further optimized, by considering that from a certain section onward, the polynomial remains the same, changing only in scale by a determined set of factors  $e_j$ . The block diagram of the structure is presented in Fig. 3.4. This leads to a structure where the polynomials used remain the same, while the factors  $e_j$  change with the sample rate conversion ratio. There are, however, some restrictions that need to be considered, as further explained in [14].

The main advantage of this design is the ability to change sample rate ratio without need to reconfigure the filter, leading to a kernel which not only is able to implement the function, but also does not need to change over time. However, as one needs to define a high number of pieces to obtain large attenuation in the stop-band (to acceptably attenuate distortion and noise), the design requires a large number of quadratic functions, which significantly increases the computational cost. Apart from the structure itself, there is still the high cost of computing the coefficients  $e_j$ , which turns even more problematic with applications for which the sample rate conversion ratio varies in time.

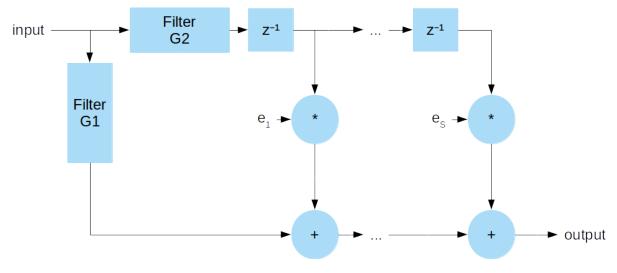

Figure 3.4: Example of optimized kernel filter structure

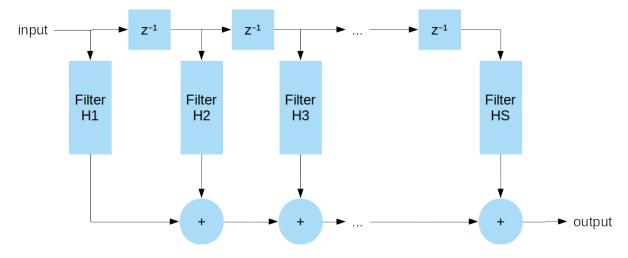

#### 3.1.4 Farrow Structure

The Farrow Structure is one of the most common implementations of fractional delay filters [16]. The structure is based on the assumption that each sample of the filter impulse response h[n] can be approximated by a polynomial of order q, which depends on the fractional delay d [17]:

$$h[n] = \sum_{m=0}^{q} c_m[n] d^m.$$

(3.3)

Similar to the structure presented in Section 3.1.3, a Farrow structure requires the implementation of a set of q FIR filters, which becomes a hardware-intensive design. Furthermore, a change in the fractional delay forces the change of all coefficients, leading to an increase of the computational cost. Over the years, this structure has been subjected to many changes and optimizations, with the objective to develop filters for different applications. For the specific application this thesis is concerned, the structure is optimized to design filters with a variable fractional delay. One possible optimization, further explained in [18], makes it possible to implement a low area Farrow structure, with the great advantage of having fixed coefficients and a single parameter  $\mu$  that corresponds to the fractional component of the output instant, when normalized to the input frequency. The block design of the structure is presented in Fig. 3.5, where the value of  $\mu$  can be computed by

$$\mu = \frac{kT_{out} - mT_{in}}{T_{in}},\tag{3.4}$$

where  $T_{in}$  and  $T_{out}$  are the input and output clock periods, respectively, m is the largest integer for which  $mT_{in} \leq kT_{out}$ , and  $k \in \{0, 1, 2, ...\}$ , is a value which increments after the computation of one output. The transfer function of each FIR sub-filter,  $C_m(z)$  is expressed by

$$C_m(z) = \sum_{k=0}^{N-1} c_m \left(k - \frac{N}{2}\right) z^{-k}.$$

(3.5)

Figure 3.5: Example of farrow structure, optimized for variable fractional delay

While the structure presented in Fig. 3.5 is optimized for interpolation, there are some modifications, explained in detail in [18] which apply to decimation. This structure has the disadvantage of having to include all sub-filters to compute all coefficients  $c_n$ , it is one of the easiest methods to allow variations on sample rate conversion ratios, and occupies a low area, which is mainly taken by the delay elements.

# 3.2 Implementation Of The Sample Rate Conversion Ratio Estimator

With the analysis done in Chapter 2, and the implementation of one of the filters described in Section 3.1, a synchronous sample rate converter (SSRC) can be implemented. To implement its asynchronous counterpart, the sample rate conversion ratio needs to be computed.

The sample rate conversion ratio can be expressed by

$$\rho = \frac{F_{sOut}}{F_{sIn}},\tag{3.6}$$

where  $\rho$  is the sample rate conversion ratio, and  $F_{sIn}$  and  $F_{sOut}$  are the respective sample rates of the input and output signals.

## 3.2.1 Period Measurement And Averaging

By analysis of Equation (3.6), it is possible to determine the value of  $\rho$  by direct measurement of the sample rate clock periods,  $T_{sIn}$  and  $T_{sOut}$ , as

$$\rho = \frac{T_{sIn}}{T_{sOut}}.$$

(3.7)

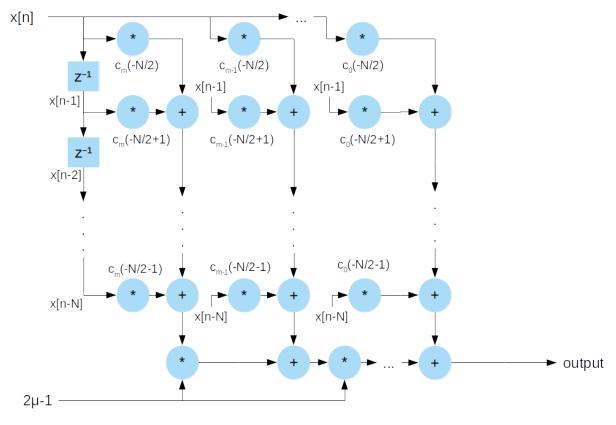

An analysis and implementation of two different implementations of this method were done in [19].

The first implementation consists on using a phase locked loop (PLL) to multiply the input sample rate clock's frequency by a factor of  $2^{L-k}$ , where *L* is the desired number of precision bits of  $\rho$ , and *k* is a parameter related to the number of measurements averaged. The output of the PLL is then used to clock a counter that will count the output sample rate clock's period. The average value of the counter's output is the inverse of  $\rho$ . A block diagram of this implementation is represented in Fig. 3.6.

Figure 3.6: Period measurement and  $\rho$  computation using a PLL.

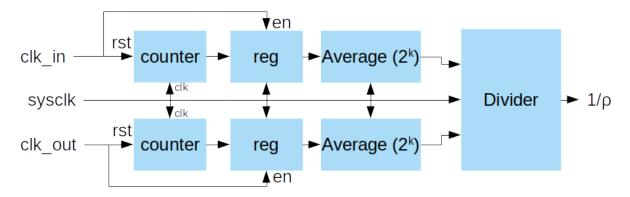

The other implementation consists on using two counters clocked at a higher speed than  $F_{sIn}$  and  $F_{sOut}$ , which will count the sample rate clock's periods. The outputs of these counters can be averaged for improved precision, and then are divided in accordance to Equation (3.7). The block diagram is represented in Fig. 3.7.

Figure 3.7: Period measurement and  $\rho$  computation using a divider.

While the first implementation requires the implementation of the PLL, which may require additional hardware, the second implementation uses an independent clock, as well as the hardware cost of the

additional counter and average block. In both implementations, the precision of the computed  $\rho$  depends on the frequency of the clock used for the counters, as well as the amount of averages done.

Additionally, this implementation has no error tracking mechanism, leading to a drift of the group delay of the converter, due small errors in the computed value of  $\rho$ . An additional module to avoid the drift needs to be implemented. This mechanism can be implemented as a frequency tracker, that stabilizes the group delay of the converter through a feedback loop.

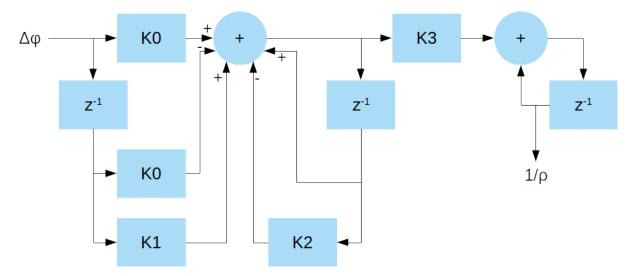

## 3.2.2 Digital Phase Locked Loop As Frequency Tracker

To compute the frequency ratio of the sample rate clocks, a digital phase locked loop (DPLL) can be used. This loop uses the value of the inverse of  $\rho$  to control the phase of the output in a feedback loop, allowing it to track the input's phase. Studies of this method were made in [19, 20]. Analog Devices' ASRC [1] also uses this loop.

Similarly to a conventional PLL, the DPLL can be split into three blocks: a phase detector, a loop filter and a voltage controlled oscillator (VCO).

The phase detector is used to compute the difference of the output and input phases. In the digital sense, it can be done with phase counters and a subtractor. Through Equation (3.6), it is possible to obtain

$$F_{sOut} = \frac{F_{sIn}}{\rho}.$$

(3.8)

Since the phase can be seen as the frequency's primitive, and assuming that the initial phase of both input and output is zero, then the input and output's phase,  $\phi_{in}$  and  $\phi_{out}$  can be expressed as

$$\begin{cases} \phi_{in} = F_{sIn} \times n \times \Delta t \\ \phi_{out} = F_{sOut} \times n \times \Delta t \end{cases},$$

(3.9)

where n is the discrete time passed since the beginning of counters' accumulations. By combining Equation (3.8) with Equation (3.9), the input and output phases can be related, yielding

$$\phi_{out} = \frac{1}{\rho} \times \phi_{in}. \tag{3.10}$$

Due to the fact that the counters are only updated at the sample rate clocks' frequencies, they need to be sampled at the same frequency. To allow this, the input's phase is sampled at the output's frequency.

The block diagram of the phase detector is shown in Fig.3.8.

For the loop filter, a low-pass filter needs to be implemented. The filter has the objective to attenuate the effect of the phase detector's jitter. However, a higher attenuation leads to a slower tracking of the DPLL. An example of a filter is a lead-lag section filter, as explained in [19].

The VCO receives the filtered phase difference to compute an output frequency. In the digital domain, this can be achieved with an integrator block.

The block diagram of the loop filter and VCO are shown in Fig. 3.9.

Figure 3.8: DPLL phase detector block diagram.

Figure 3.9: DPLL loop filter and VCO block diagram.

To improve the DPLL's dynamic behavior, the filter's bandwidth can be controlled, by allowing a higher bandwidth for a faster tracking and gradually lowering it for an improved precision and noise rejection. An in-lock detector that uses the phase difference as input can be used.

This implementation has the advantage of not requiring a fast clock to work, as the computations are done at the output's sample rate clock. However, it also leads to the need to determine the correct parameters (K0, K1, K2 and K3) of the filter, as well as the additional hardware used to implement the filter. In FPGA implementations, it may also lead to timing problems, as pipelining leads to latency in the computations, which impacts the DPLL's performance.

# **Chapter 4**

# **Proposed Design**

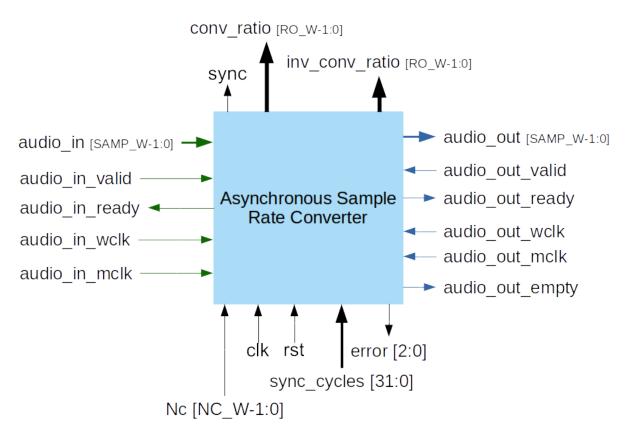

The symbol and interface signals of the sample rate converter design are presented in Fig. 4.1. The data input and output signals are *audio\_in* and *audio\_out*, respectively, and the sample rate clocks are *audio\_in\_wclk* and *audio\_out\_wclk*, respectively. The definition of all interface signals is presented in Table 4.1.

Figure 4.1: Symbol and interface diagram.

As a core designed for FPGA and ASIC implementations, the ASRC can be configured pre-synthesis to match the intended application. The synthesis parameters are presented in Table 4.2.

| Name            | Direction | Width  | Description                                                                                                                                                               |  |  |

|-----------------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| clk             | input     | 1      | System clock signal.                                                                                                                                                      |  |  |

| rst             | input     | 1      | Reset signal active high (1).                                                                                                                                             |  |  |

| Nc              | input     | NC_W   | Number of channels to convert must be power of 2.                                                                                                                         |  |  |

| sync_cycles     | input     | 32     | Number of system clock cycles to wait for synchroniza-<br>tion.                                                                                                           |  |  |

| sync            | output    | 1      | Active high (1) when the ASRC has computed conversion ratio.                                                                                                              |  |  |

| conv₋ratio      | output    | RO_W   | Sample rate conversion ratio.                                                                                                                                             |  |  |

| inv_conv_ratio  | output    | RO_W   | Inverse of sample rate conversion ratio.                                                                                                                                  |  |  |

| audio₋in        | input     | SAMP_W | Input audio stream.                                                                                                                                                       |  |  |

| audio_in_valid  | input     | 1      | Input audio valid signal.                                                                                                                                                 |  |  |

| audio_in_ready  | output    | 1      | Input audio ready signal.                                                                                                                                                 |  |  |

| audio_in_mclk   | input     | 1      | Input audio master clock (frequency should be $N \times f_{-s}$<br>where $f_{-s}$ is the input sample rate and N is an integer<br>greater than the number of channels).   |  |  |

| audio_in_wclk   | input     | 1      | Input audio word clock (frequency should be equal to in-<br>put sample rate).                                                                                             |  |  |

| audio₋out       | output    | SAMP₋W | Output audio stream.                                                                                                                                                      |  |  |

| audio_out_ready | output    | 1      | Active high (1) if the ASRC has a valid output sample buffered.                                                                                                           |  |  |

| audio_out_wclk  | input     | 1      | Output audio word clock (frequency should be equal to input sample rate).                                                                                                 |  |  |

| audio_out_mclk  | input     | 1      | Output audio master clock (frequency should be $N \times f_{-s}$<br>where $f_{-s}$ is the output sample rate and N is an integer<br>greater than the number of channels). |  |  |

| audio_out_valid | input     | 1      | Output audio valid signal.                                                                                                                                                |  |  |

| audio_out_empty | output    | 1      | Set low (0) if there are output samples to retrieve.                                                                                                                      |  |  |

| error           | output    | 3      | Error bits (2) Audio out buffer— (1) PTR_DIFF— (0) NChannels                                                                                                              |  |  |

Table 4.1: Interface signals.

| Parameter  | Default Value | Description                        |

|------------|---------------|------------------------------------|

| SAMP_W     | 24            | Audio sample width                 |

| NC_W       | 8             | Number of channels signal width    |

| RO_W       | 35            | Sample rate conversion ratio width |

| SAMP_BUF_W | 10            | Data memory size (log_2)           |

| Table 4 2 <sup>.</sup> | Synthesis | Parameters  |

|------------------------|-----------|-------------|

| Table 4.2.             | Synthesis | i arameters |

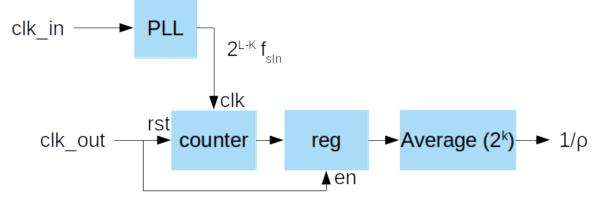

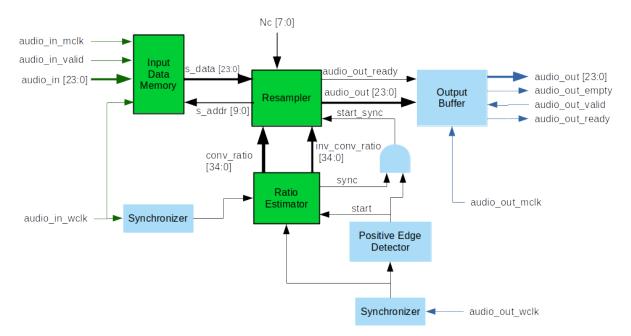

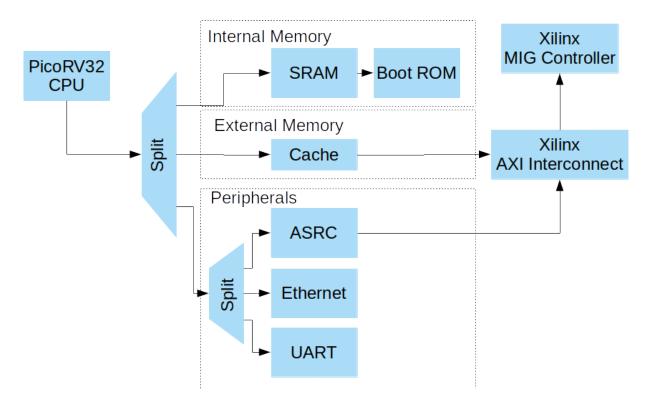

The ASRC is divided in three main modules: the Input Data Memory, the Ratio Estimator and the Resampler. Additionally, the ASRC includes a positive edge detector circuit, implemented with a register, to generate the *start* signal, used to start the computation of a new output sample, as well as an asynchronous FIFO, used to temporarily store the output samples to be read, and to allow their crossing from the system clock to the output audio master clock. A block diagram of the ASRC is presented in Fig. 4.2.

As the core works in three different clock domains, all figures present the signals in three different colors, with green arrows indicating signals in the *audio\_in\_mclk* domain, blue arrows for signals in the *audio\_out\_mclk* domain, and black arrows for signals in the *clk* domain. This is important, as wherever there is a clock domain crossing, one needs to implement a suitable synchronizer circuit.

A synchronizer module performs the crossing of the *audio\_in\_wclk* and *audio\_out\_wclk* signals to the system clock domain. Since the *wclk* signals are single wires, and the transitions are from a slower to a faster clock domain, the synchronizer module is composed by two registers, clocked by *clk*.

Figure 4.2: Asynchronous sample rate converter top block diagram.

## 4.1 Data Memory

To store the input samples, a data memory is used. The data memory is a dual port Random Access Memory (RAM) capable of working at two different clock domains. A block diagram of the data memory and its write port address counter is presented in Fig. 4.3.

In the input clock domain, the samples  $audio_in$  are stored in the position given by  $audio_in_waddr$  at the rate of  $audio_in_wclk$ . The write address counter  $audio_in_waddr$  is incremented at the  $audio_in_wclk$  rate, whenever  $audio_in_valid$  is active. In the system clock domain, the samples are read by accessing the position given by  $s_addr$ . The read samples are used to perform the filtering. For Nc Time Division

Figure 4.3: Data memory module block diagram.

Multiplexed (TDM) channels, to obtain the next sample of a certain channel, the address  $s_addr[n+1]$  is given by

$$s_addr[n+1] = s_addr[n] + Nc.$$

$$(4.1)$$

Since the accumulators do not stop or reset during the conversion, they wrap around creating a circular memory. When there is a stream of input samples, the newer ones will overwrite the older ones which will not be used anymore in the filter. On average, the write and read pointers increment at the same rate, which is guaranteed by the Ratio Estimator block.

Since the data memory is a true dual port memory, the synchronizer to cross the clock domains unnecessary, as the memory already serves that purpose.

# 4.2 Ratio Estimator

The sample rate converter is asynchronous, so the frequency of the input and output clocks can change over time. Furthermore, their frequencies can also take any value in the supported range. The frequencies of the data clocks are unknown by the core, but their ratio,  $\rho$ , must be computed. The ratio estimator computes an estimated value of the sample rate conversion ratio,  $\hat{\rho}$ .

As was studied in section 3.2, there are two possible implementations for the ratio estimator. In this thesis, a period measurement and averaging implementation, described in subsection 3.2.1, is used. The system clock is used as the reference clock, and two counters and a divider obtain the approximate sample rate conversion ratio ( $\hat{\rho}$ ), as shown in Fig. 3.7. Additionally, a frequency tracker is added to ensure that the error in the approximation  $\rho^{-1}$  of  $\rho^{-1}$  does not lead to a deviation of the write and read data memory pointers.

## 4.2.1 Initial Approximation - Period Measurement and Averaging

The block diagram of the period meter is shown in Fig. 4.4.

Figure 4.4: Ratio Estimator module block diagram.

The Period Meter block uses a counter to obtain the values,  $T\hat{i}n$  and  $T\hat{o}ut$  of the data clocks periods measured in system clock cycles. Since the counter is incremented at the system clock rate  $f_{sys\_clk}$ , approximate values of the data clock periods  $Tin_{seconds}$  and  $Tout_{seconds}$  are given by

$$\begin{cases} Tin_{seconds} = \frac{T\hat{i}n}{f_{sys.clk}} \\ Tout_{seconds} = \frac{T\hat{o}ut}{f_{sys.clk}} \end{cases} . \tag{4.2}$$

The ratio  $\rho$  between the input and output clock frequencies  $f_{in}$  and  $f_{out}$  is defined by

$$\rho = \frac{f_{out}}{f_{in}}.\tag{4.3}$$

Combining Equation (4.2) and (4.3), an approximate value of  $\rho$  can be computed by

$$\hat{\rho} = \frac{\hat{Tin}}{\hat{Tout}}.$$

(4.4)

The value of  $\hat{\rho}$  can be computed in hardware without knowing any clock frequencies. However, since the counter is only able to count integer values, the periods of the input and output clocks are imprecise. For the same clock frequency the values  $T\hat{i}n$  and  $T\hat{o}ut$  can vary each time they are measured, with an absolute error of 1 time unit (clock period). It should be noted that the resolution of the counter increases with the frequency of the system clock: a higher system clock frequency leads to a lower error in  $T\hat{i}n$  and  $T\hat{o}ut$ .

To improve the precision of this approximation, the measured periods  $\hat{Tin}$  and  $\hat{Tout}$  are accumulated ( $Tin\_acc$  and  $Tout\_acc$ ) and counted ( $Tin\_cnt$  and  $Tout\_cnt$ ), to compute an average value. The operation is expressed as

$$T\_avg = \frac{T\_acc}{T\_cnt}.$$

(4.5)

The combination of the Equations (4.4) and (4.5) leads to the expression used by the design:

$$\begin{cases} \rho = \frac{Tin\_acc \times Tout\_cnt}{Tin\_cnt \times Tout\_acc} = \frac{prod1}{prod2} \\ \rho^{-1} = \frac{Tout\_acc \times Tin\_cnt}{Tout\_cnt \times Tin\_acc} = \frac{prod2}{prod1} \end{cases}.$$

(4.6)

One needs to perform a significant number of accumulations to obtain an accurate average; the accumulations are performed for a certain synchronization time. A counter, clocked at the system clock, is used to count this synchronization time. The number of synchronization cycles counted is given by the user through the interface of the core.

After the measurements are done and the average is computed, the resulting values of  $\hat{\rho}$  and  $\hat{\rho^{-1}}$  are valid and accurate enough to allow the ASRC to start the conversion.

## 4.2.2 Frequency Tracker

The approximate values,  $\hat{\rho}$  and  $\hat{\rho^{-1}}$ , obtained are accurate enough to fulfill the specification. However, the inaccuracy of  $\hat{\rho^{-1}}$  leads to a drift of the group delay of the converter, which may lead to simultaneous read and write operations at the same address of the data memory. The Frequency Tracker block is used to correct the error by using the approximate value  $\hat{\rho_{est}}^{-1}$ , computed by the hardware described in subsection 4.2.1, as an initial approximation. The frequency tracker design is a simplification of the digital PLL described in subsection 3.2.2, as the loop filter is implemented by averaging multiple phases, obtained by the phase detector. The block diagram of the frequency tracker is shown in Fig. 4.5.

The frequency tracker uses the phases normalized to the input sample rate. As such, on every tick of the input word clock, the input phase accumulator adds '1.0'. Meanwhile, the output phase accumulator will add  $\rho^{-1}$  on every tick of the output word clock. Note that, since the output sample rate is  $\rho$  times faster than the input counterpart, the output phase accumulator will in average accumulate  $\hat{\rho}$  times the amount of input phase accumulations. During certain amount of time  $\Delta t$ , the accumulated phases  $\phi_{in}$  and  $\phi_{out}$  are given by

$$\begin{cases} \phi_{in} = 2\pi F_{sIn} \times \Delta t \\ \phi_{out} = \rho^{-1} \times 2\pi F_{sOut} \times \Delta t \end{cases},$$

(4.7)

where  $F_{sIn}$  and  $F_{sOut}$  are the sample rates of the input and output, respectively. The normalization of Equation (4.7) to the input sample rate, and the application of Equation (3.8) yield

Figure 4.5: Frequency Tracker module block diagram.

$$\begin{cases} \frac{\phi_{in}}{2\pi F_{sIn}} = \Delta t \\ \frac{\phi_{out}}{2\pi F_{sIn}} = \rho \times \hat{\rho^{-1}} \times \Delta t \end{cases}$$

(4.8)

By subtracting the two expressions of Equation (4.8) one obtains the variation of the delay between the input and output phases, given by

$$\frac{\phi_{in} - \phi_{out}}{2\pi F_{sIn}} = \Delta t - \rho \times \hat{\rho^{-1}} \times \Delta t.$$

(4.9)

To adapt to the discrete time domain, and normalize the variation of delay to a single variable  $\Delta D$ , Equation (4.9) can be rewritten as

$$\Delta D = \frac{(\phi_{in} - \phi_{out})}{2\pi} = \rho^{-1} \times N_{out} - \hat{\rho^{-1}} \times N_{out},$$

(4.10)

where  $N_{out}$  is the number of output accumulations done, given by

$$N_{out} = F_{sOut} \times \Delta t = \rho \times F_{sIn} \times \Delta t.$$

(4.11)

If the value of  $\rho^{-1}$  is accurate, being equal to  $\rho^{-1}$ , the value of  $\Delta D$  will be equal to zero. Otherwise, there is a drift of the input and output phases, which will influence the value of  $\Delta D$ . As such, the value of  $\Delta D$  can be used to apply corrections to the value of  $\rho^{-1}$ , to ensure that  $\Delta D$  converges to zero. The correction needed to apply, *C* is given by

$$C = \rho^{-1} - \hat{\rho^{-1}}, \tag{4.12}$$

By combining Equations (4.10) and (4.12), the expression used by the module to determine the correction applied to  $\rho^{-1}$  is obtained, being

$$C = \frac{\Delta D}{N_{out}}.$$

(4.13)

To obtain the value of  $\Delta D$  in hardware, two values of the delay are measured sequentially, as the difference between them is the value of  $\Delta D$  used. The delay itself is the difference between the accumulated input and output phases. To obtain more precision, the delay is measured for 4096 output clock cycles ( $N_{out} = 4096$ ). Additionally, to ensure that the corrections of  $\rho^{-1}$  occur as smoothly as possible, and to reject clock jitter, the value of the correction applied is attenuated, as a strong variation of  $\rho^{-1}$  negatively impacts the audio fidelity, increasing the THD+N.

## 4.2.3 Ratio Estimator Control Unit

To save on the silicon area used, only one multiplier and one divider are used, and shared by both the Ratio Estimator and the Frequency Tracker. The divider and the multiplier are implemented using a serial shift-subtract and shift-add units, respectively, for minimum size and power consumption, as performance is not important here.

The inputs of the multiplier and divider, as well as the accumulators and counters, are controlled by a finite state machine (FSM). The Frequency Tracker block is also controlled by the FSM, and also uses the divider to compute  $\hat{\rho}$ . The state transition diagram of the FSM is shown in Fig. 4.6.

The FSM has the following states:

- State 0: Initial state The FSM resets the counters and accumulators.

- State 1: Measure periods The FSM keeps the enables of the period meters active. The state does not change until the system clock cycle counter reaches the value input by the user.

- State 2: Compute ρ dividend (prod1) The FSM selects Tin\_acc as multiplicand and Tout\_cnt as multiplier, and enables the multiplier.

- State 3: Wait for multiplication The FSM keeps the multiplier enabled. The state does not change

until the multiplier is ready for a new multiplication. During the state transition, the FSM enables

the register for *prod1*, storing the output of the multiplier in it.

- State 4: Compute ρ divisor (prod2) The FSM selects Tout\_acc as multiplicand and Tin\_cnt as multiplier, and enables the multiplier.

- State 5: Wait for multiplication Similar to State 3. Instead of enabling the register for *prod1* during the state transition, the FSM enables the register for *prod2*.

- State 6: Compute ρ The FSM selects *prod*1 as dividend and *prod*2 as divisor, enables the divider and keeps the divider sign signal disabled (unsigned division).

- State 7: Wait for division The FSM keeps the divider enabled. The state does not change until the divider is ready for a new division. During state transition, the FSM enables the register for *ρ*.

- State 8: Compute *inv<sub>-</sub>ρ* The FSM selects *prod2* as dividend and *prod1* as divisor, enables the divider and keeps the divider sign signal disabled (unsigned division).

- State 9: Wait for division Similar to State 7. Instead of enabling the register for *ρ*, the FSM enables the register for *inv\_ρ* during state transition.

- State 10: Measure delay The FSM keeps the delay counter and accumulator enabled. The state is kept while the output period counter counts up to 4096. Note that from this state onward, the ASRC is ready to start the conversion. As such, the FSM toggles the *sync* signal on.

- State 11: Compute average delay The FSM selects *delay\_acc* as dividend and *delay\_cnt* as divisor, and enables the divider with sign active (signed division).

- State 12: Wait for division Similar to State 7 and 9. During state transition, the FSM enables the register for *delay\_avg*, and resets the delay counter and accumulator. This state transitions to state 10. Note that the frequency tracker module uses the value of *delay\_avg* to periodically adjust ρ<sup>-1</sup>

The outputs of the FSM per state are shown in Table 4.3.

Figure 4.6: Ratio Estimator FSM state diagram.

| State ID | Output Signals          | Notes                                                                                                                |

|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------|

|          | count₋rst = 1           |                                                                                                                      |

| 0        | delay_cnt_rst = 1       |                                                                                                                      |

|          | sync_nxt = 0            |                                                                                                                      |

| 1        | count₋en = 1            |                                                                                                                      |

|          | multiplicand = Tin_acc  |                                                                                                                      |

| 2        | multiplier = Tout_cnt   |                                                                                                                      |

|          | mul_en = 1              |                                                                                                                      |

| 0        | mul_en = 1              | Only if mul_ready=0.                                                                                                 |

| 3        | prod1_en = 1            | Only if mul_ready=1. Multiplier output is stored in register prod1.                                                  |

|          | multiplicand = Tout_acc |                                                                                                                      |

| 4        | multiplier = Tin_cnt    |                                                                                                                      |

|          | mul_en = 1              |                                                                                                                      |

| 5        | mul_en = 1              | Only if mul_ready=0.                                                                                                 |

| 5        | prod2_en = 1            | Only if mul_ready=1. Multiplier output is stored in register prod2.                                                  |

|          | dividend = prod1        |                                                                                                                      |