# Validation of Industrial Processes Implemented on PLCs based on Petri Nets

## Hugo José Damas Mora Conde Barroso

Thesis to obtain the Master of Science Degree in

## **Electrical and Computer Engineering**

Supervisor: Professor José António da Cruz Pinto Gaspar

## **Examination Committee**

Chairperson: Professor João Fernando Cardoso Silva Sequeira Supervisor: Professor José António da Cruz Pinto Gaspar Member of the Committee: Professor Fernando Joaquim Ganhão Pereira

February 2021

# Declaration

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

ii

## Resumo

Os Sistemas de Eventos Discretos (SED) são ubíquos na indústria, aparecendo normalmente como supervisores implementados em Controladores Lógicos Programáveis (CLP). Projetar e implementar um SED em CLP é um processo moroso que normalmente requer várias fases de verificação e validação.

As redes de Petri são um paradigma de modelação prático, aplicável a uma grande variedade de SED, principalmente devido às suas representações claras e expressivas, gráficas e matemáticas. Ao modelar os sistemas com Redes de Petri IOPT, uma classe de redes de Petri estendida com recursos de entrada e saída, caso as redes sejam seguras (ou limitadas), pode-se traduzir tais modelos diretamente para programas de CLP. Isto fornece uma maneira eficaz de criar programas de CLP harmonizando a complexidade de representar SEDs.

Uma rede de Petri, representante de um processo, permite encontrar o conjunto de estados alcançável, que é uma via para verificar e validar a produção de código CLP. Uma árvore de cobertura baseada no conceito de dominância de nó é proposta para considerar apenas processos com conjuntos alcançáveis finitos. Finalmente, encontramos ciclos de operação, evitando assim casos de *deadlock*, e usamos as sequências de transições para avaliar se o código do processo atinge efetivamente todos os estados possíveis.

A ferramenta *IOPT tools*, criada na Faculdade de Ciências e Tecnologia para desenvolver controladores de sistemas embebidos, é utilizada nesta dissertação para criar redes de Petri IOPT. As redes de Petri projetadas são então utilizadas como entrada da ferramenta geradora de controladores CLP/SED, criada no Instituto Superior Técnico para ensino de automação de processos industriais.

Foram obtidos resultados promissores em casos práticos de validação da produção de código CLP, pelo teste exaustivo de estados alcançáveis determinados a partir da rede de Petri que representa o processo industrial. Adicionalmente, a metodologia proposta mostrou ser possível detectar antecipadamente problemas de design e estudar os efeitos de restrições impostas por hardware.

**Palavras chave:** Sistemas de Eventos Discretos (SED), Redes de Petri, Redes de Petri IOPT, Alcançabilidade, Árvore de Cobertura, Controlador Lógico Programável (CLP), Structured Text, Validação, Verificação.

## Abstract

Discrete Event Systems (DES) are commonly found as supervisors in industrial applications which are, in general, implemented by Programmable Logic Controllers (PLC). Designing and implementing a DES in a PLC is a thorough process typically requiring multiple verification stages and process validation.

Petri nets are a powerful modeling paradigm for a variety of DES, mostly because of their clear and expressive, graphical and mathematical, representations. By modeling the systems with IOPT Petri Nets, a class of Petri nets extended with input and output capabilities, in the case the nets are safe (or bounded), one may translate those models directly to PLC programs. This provides an effective way to create PLC programs by mediating the complexity of representing DES.

Verification and validation are required to assess the PLC code production. A Petri net representing a process allows finding the reachable set of states. A coverability tree based on the node dominance concept is proposed to consider just processes with finite reachable sets. Finally, we find operation cycles, avoiding therefore deadlock cases, and use sequences of transitions to assess whether the process code effectively reaches all possible states.

The *IOPT tools* toolchain, created in Faculdade de Ciências e Tecnologia to develop embedded system controllers, is used in this thesis to design Petri nets. The designed Petri nets are then used as the input of the PLC/DES controller maker toolchain, created in Instituto Superior Técnico for teaching automation.

Promising results were obtained in practical cases of validation of the production of PLC code, by the exhaustive test of reachable states determined from the Petri net that represents the industrial process. In addition, the proposed methodology showed that it is possible to anticipate the detection of design problems and study the effects of restrictions imposed by hardware.

**Keywords:** Discrete Event System (DES), Petri Net, IOPT Petri net, Reachability, Coverability Tree, Programmable Logic Controller (PLC), Structured Text, Validation, Verification.

vi

# Contents

| De | Declaration |         |                                                        |     | i   |

|----|-------------|---------|--------------------------------------------------------|-----|-----|

| Re | esumo       | )       |                                                        |     | iii |

| Al | bstrac      | t       |                                                        |     | v   |

| 1  | Intr        | oductio | n                                                      |     | 1   |

|    | 1.1         | Progra  | mming and Validation based on Petri nets               |     | 2   |

|    | 1.2         | Relate  | d Work                                                 |     | 3   |

|    | 1.3         | Object  | ives and Challenges                                    |     | 4   |

|    | 1.4         | Thesis  | Structure                                              | ••• | 5   |

| 2  | Bac         | kground | 1                                                      |     | 7   |

|    | 2.1         | Verific | ation vs Validation                                    |     | 7   |

|    | 2.2         | Petri N | Jets                                                   |     | 9   |

|    | 2.3         | The Re  | eachability Problem                                    |     | 17  |

|    | 2.4         | Covera  | ability Tree                                           |     | 19  |

|    | 2.5         | Thesis  | Approach                                               |     | 22  |

| 3  | Imp         | lementa | ation of Industrial Processes on PLCs using Petri Nets |     | 23  |

|    | 3.1         | DES T   | To PLC Conversion Toolchain                            |     | 24  |

|    |             | 3.1.1   | Finite Reachable Set                                   |     | 25  |

|    |             | 3.1.2   | DES Implementation                                     |     | 25  |

|    | 3.2         | Case S  | Study - Alarm System                                   |     | 30  |

|    |             | 3.2.1   | Modes of Operation                                     |     | 31  |

|    |             | 3.2.2   | Proposed IOPT Petri net model                          |     | 32  |

|    |             | 3.2.3   | Properties Study                                       |     | 35  |

| 4 | Validation of Industrial Processes based on Petri Nets |                                                                   | 37 |

|---|--------------------------------------------------------|-------------------------------------------------------------------|----|

|   | 4.1                                                    | System Validation based on the Coverability Tree                  | 37 |

|   | 4.2                                                    | Petri net Graphs and Coverability Trees                           | 38 |

|   | 4.3                                                    | Coverability Tree Construction                                    | 38 |

|   |                                                        | 4.3.1 Node Dominance                                              | 38 |

|   |                                                        | 4.3.2 Algorithm General Steps                                     | 40 |

|   | 4.4                                                    | Generation of Event Sequences                                     | 41 |

|   | 4.5                                                    | Extension of Petri net models to include Time                     | 45 |

| 5 | Exp                                                    | periments                                                         | 47 |

|   | 5.1                                                    | Use Case 1 - Reach All Possible States                            | 47 |

|   | 5.2                                                    | Use Case 2 - PLC-DES interaction with World-DES                   | 51 |

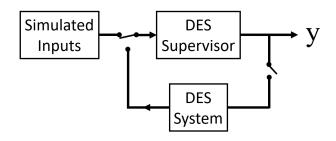

|   |                                                        | 5.2.1 Closed Loop Simulation, PLC and World Interaction           | 52 |

|   |                                                        | 5.2.2 Validation using the PLC Development Tools                  | 55 |

|   | 5.3                                                    | Use Case 3 - Effects of Hardware Constraints on Petri net Designs | 58 |

| 6 | Con                                                    | clusion and Future Work                                           | 65 |

| A | Imp                                                    | lementation details of Use Case 1                                 | 67 |

| B | Implementation details of use case 2                   |                                                                   | 71 |

|   | <b>B</b> .1                                            | Function Implementation                                           | 71 |

|   | B.2                                                    | Storyboard Implementation                                         | 72 |

| С | Con                                                    | necting Digital Systems to noisy Inputs                           | 75 |

|   | C.1                                                    | Handling input bouncing on PLCs                                   | 76 |

| D | Cov                                                    | erability Tree Construction Algorithm                             | 83 |

# **List of Figures**

| 1.1 | Automated conversion from high level Petri net to Structured Text as an faster<br>alternative to direct PLC programming. May induce errors in the conversion as |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | well as conceptual errors in the Petri net design.                                                                                                              | 2  |

| 2.1 | Example of a Petri net.                                                                                                                                         | 10 |

| 2.2 | Example of a Petri net (left) and its corresponding reachability tree (right), if                                                                               |    |

|     | the initial marking is $[1; 0; 0]$ .                                                                                                                            | 16 |

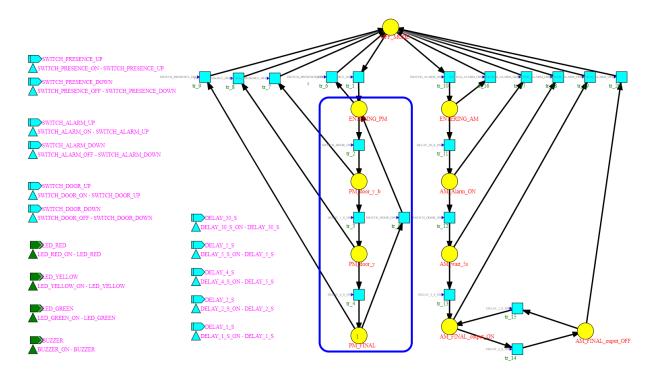

| 3.1 | Petri net supervising the system HW to be controlled                                                                                                            | 23 |

| 3.2 | IOPT PN to ST Converter. A decision method to reject unbounded PN is added                                                                                      |    |

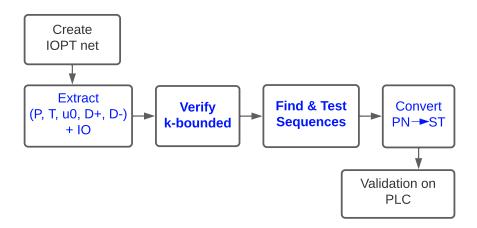

|     | as well as to automatically generate testing sequences.                                                                                                         | 24 |

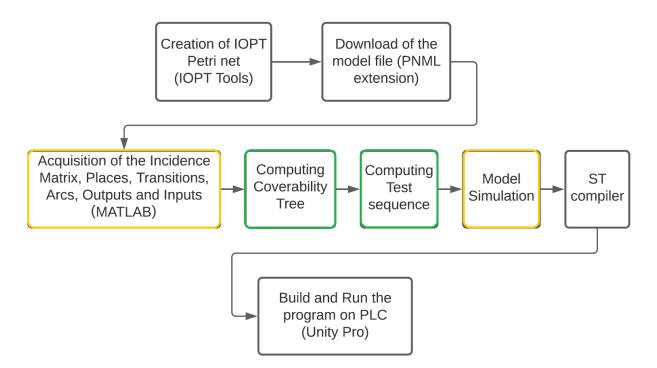

| 3.3 | A more detailed block diagram of the IOPT PN to ST Converter. The green box                                                                                     |    |

|     | represents proposed additions with this thesis. The yellow box represents                                                                                       |    |

|     | where main changes were introduced.                                                                                                                             | 30 |

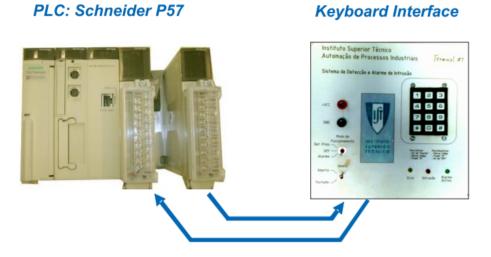

| 3.4 | Alarm system, based in one PLC and one terminal - extracted from [15]                                                                                           | 31 |

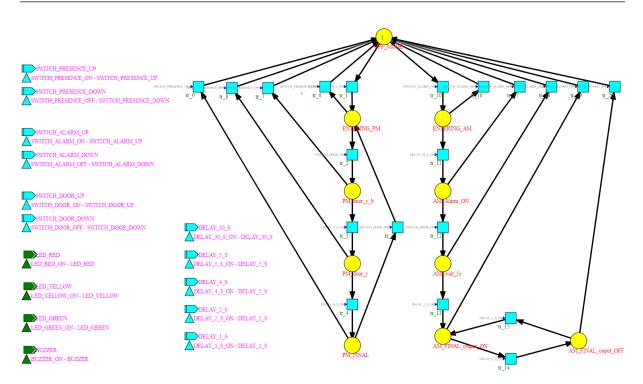

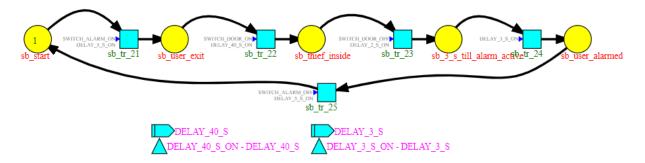

| 3.5 | Petri net edited with IOPT Tools [16] to control the alarm.                                                                                                     | 33 |

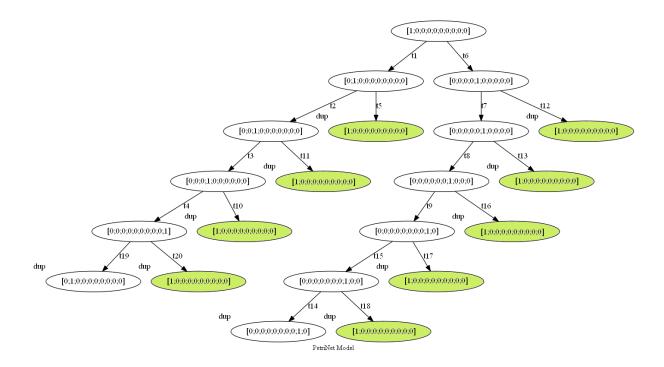

| 3.6 | Coverability Tree for the proposed Alarm Petri net (Duplicate states are marked                                                                                 |    |

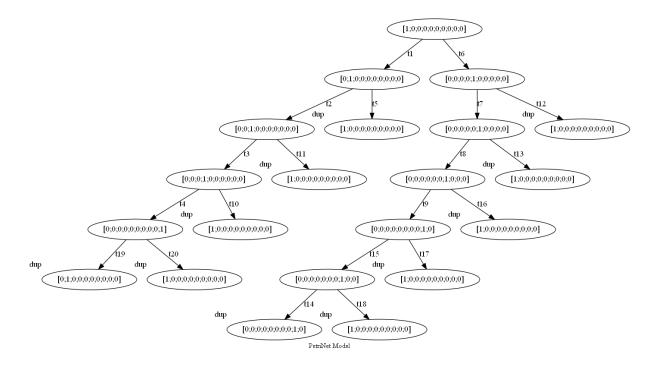

|     | "dup" on the top left corner)                                                                                                                                   | 36 |

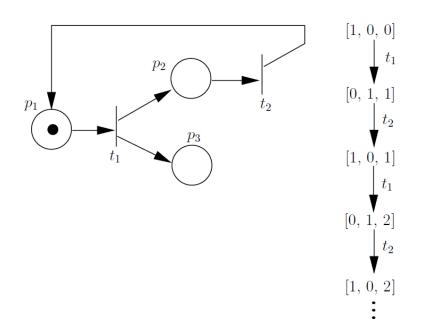

| 4.1 | Unbounded Petri net (left) and part of its infinite reachability tree (right)                                                                                   | 39 |

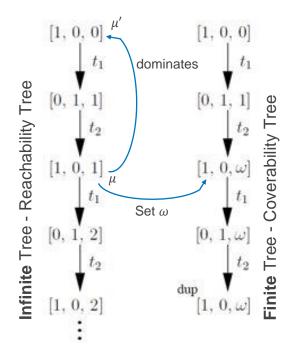

| 4.2 | Infinite Reachability Tree (left) and corresponding Coverability Tree (right),                                                                                  |    |

|     | for Petri net in Figure 4.1. When a state $\mu$ dominates a state $\mu'$ in the path from                                                                       |    |

|     | the root node to $\mu$ set the marking of the places that verify both conditions of                                                                             |    |

|     | dominance in state $\mu$ to $\omega$ .                                                                                                                          | 40 |

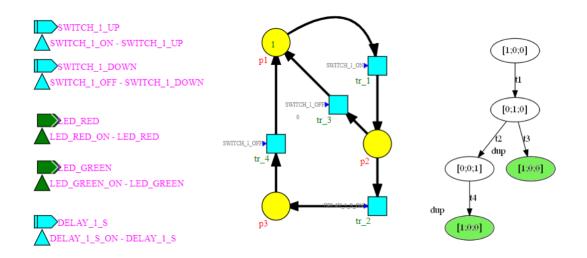

| 4.3 | IOPT Petri net C (middle), IO signals and events (left) and Coverability Tree                                                                                   |    |

|     | (right)                                                                                                                                                         | 41 |

| 4.4 | The $MP$ structure: (a) $P$ cell matrix, (b) $S$ cell matrix, (c) $M$ cell matrix                                                                               | 43 |

### LIST OF FIGURES

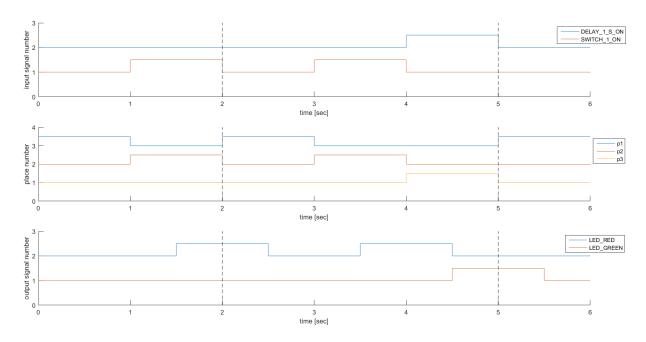

| 4.5  | Simulation results.                                                               | 45 |

|------|-----------------------------------------------------------------------------------|----|

| 5.1  | Illustration of use case 1 testing. The IOPT Petri net of the DES supervisor      |    |

|      | reacts only to the given input sequences, disregarding any possible interaction   |    |

|      | with the system it should supervise.                                              | 48 |

| 5.2  | Coverability Tree of the proposed Petri net (PN) to supervise the alarm           | 49 |

| 5.3  | Behaviour of alarm supervisor IOPT from Figure 3.5 given the sequence of          |    |

|      | events extracted from its coverability tree                                       | 51 |

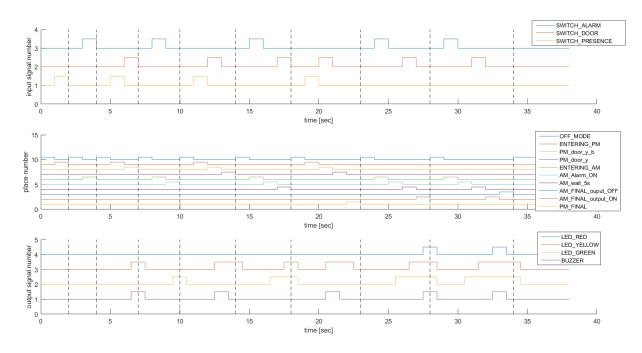

| 5.4  | Storyboard IOPT proposed for Use Case 2                                           | 52 |

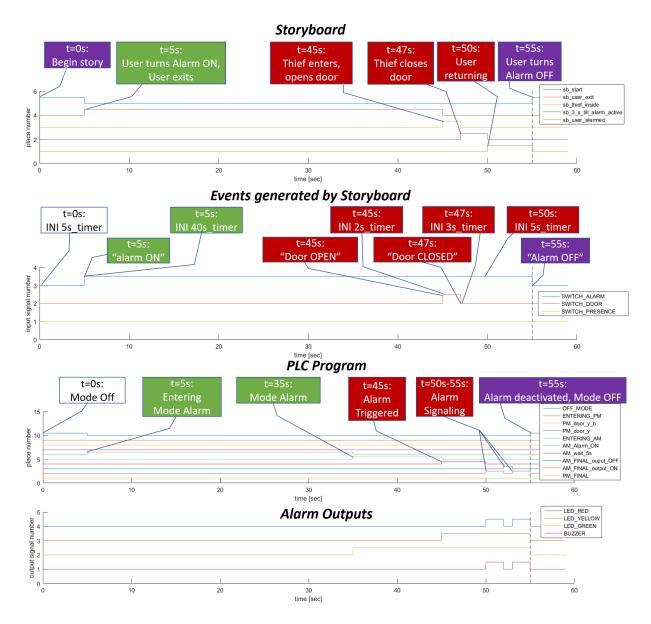

| 5.5  | Alarm PLC program (Figure 3.5) driven by a storyboard (Figure 5.4) showing        |    |

|      | the typical correct functioning of the alarm in Alarm mode                        | 54 |

| 5.6  | myterminal5 interface that emulates the alarm system                              | 55 |

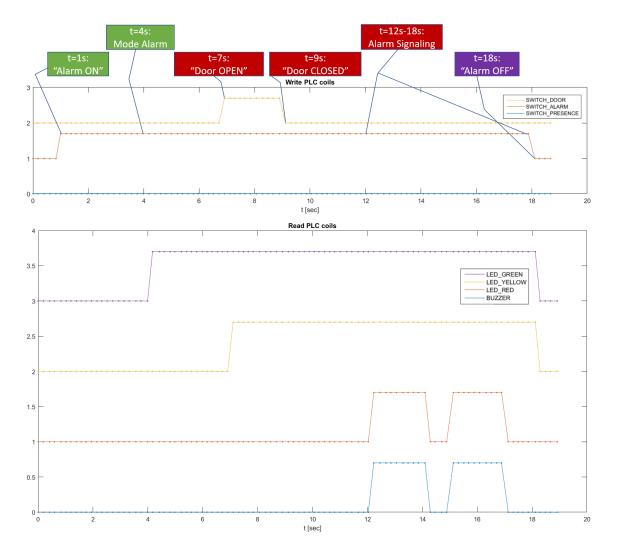

| 5.7  | Alarm PLC-DES simulation on Unity Pro given a table $U_t$                         | 57 |

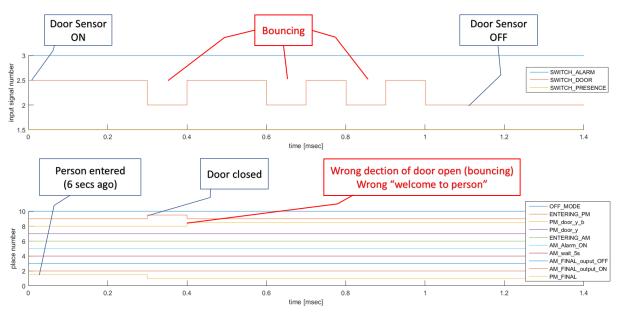

| 5.8  | Alarm setup. Bouncing happens on the switches, but exists mostly in the push-     |    |

|      | buttons.                                                                          | 58 |

| 5.9  | Area where bouncing may disrupt the expected functioning of the controller        | 59 |

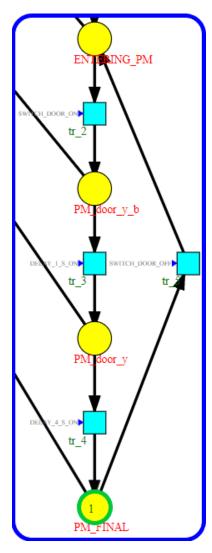

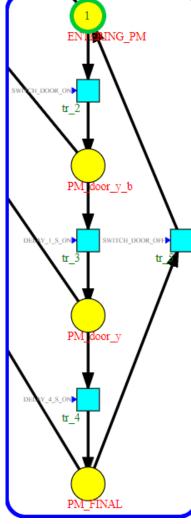

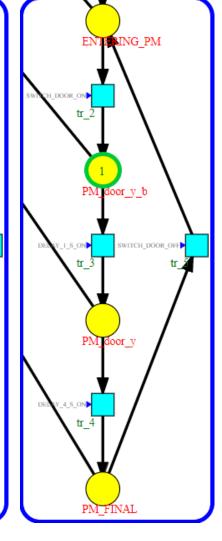

| 5.10 | Petri net currently at state PM_FINAL                                             | 60 |

| 5.11 | Evolution to state ENTERING_PM by turning OFF the door switch, enabling           |    |

|      | transition tr_5                                                                   | 60 |

| 5.12 | Evolution to state PM_door_y_b due to bouncing on the door switch, causing        |    |

|      | the signal to be ON and enabling transition tr_2                                  | 60 |

| 5.13 | Behaviour of Petri net's region of Figure 5.9 given table $U_t$ (5.5)             | 61 |

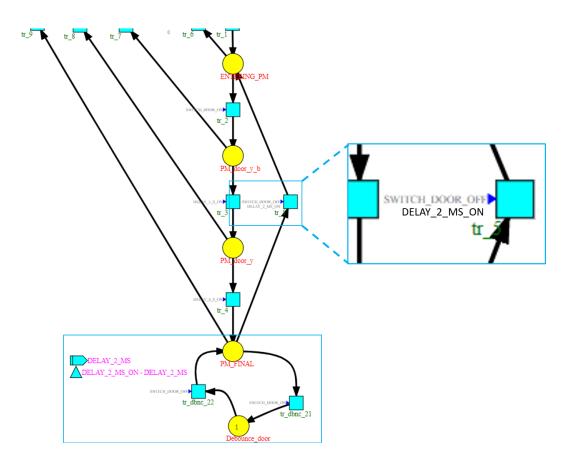

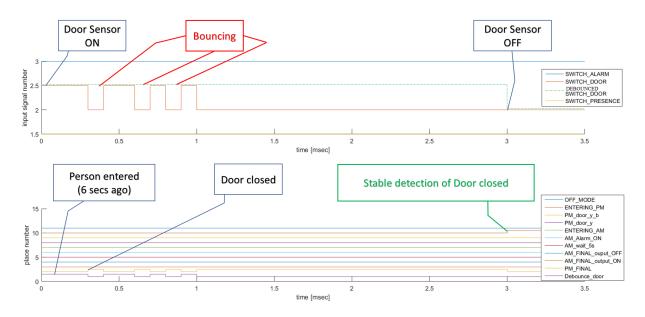

| 5.14 | Petri net debouncing implementation for place PM_FINAL and input signal           |    |

|      | SWITCH_DOOR                                                                       | 63 |

| 5.15 | Behaviour of Petri net's region of Figure 5.14 given table $U_t$ (5.5)            | 63 |

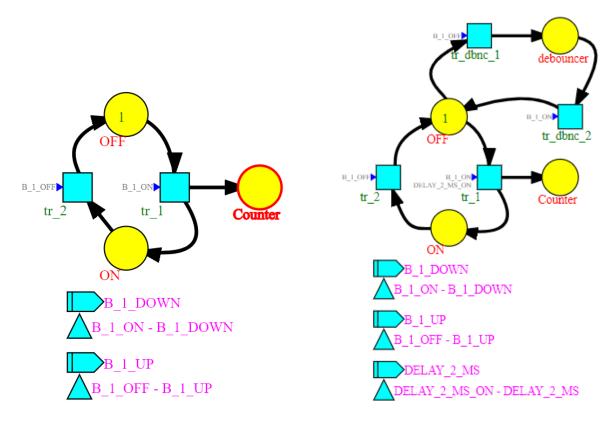

| C.1  | A simple counter to detect bouncing                                               | 80 |

| C.2  | A simple counter with debouncing mechanism.                                       | 80 |

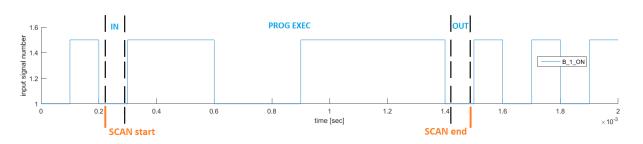

| C.3  | Behaviour of IOPT Petri net in Figure C.1 given table $U_t$ (C.1) overlapped with |    |

|      | a possible scan cycle, showing an incorrect reading of the input signal due to    |    |

|      | bouncing.                                                                         | 80 |

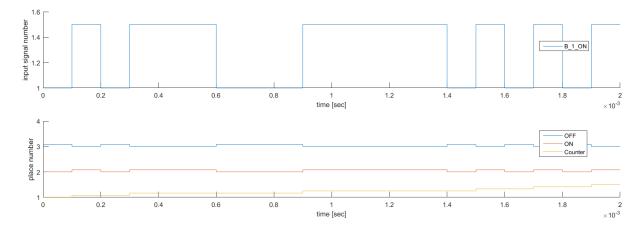

| C.4  | Behaviour of Petri net in Figure C.1 given table $U_t$ (C.1). The DES to PLC      |    |

|      | conversion toolchain does not apply debouncing.                                   | 81 |

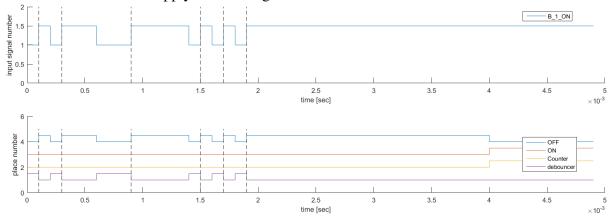

| C.5  | Behaviour of Petri net in Figure C.2 given table $U_t$ (C.1). Debouncing is now   |    |

|      | done on the IOPT Petri net                                                        | 81 |

# **List of Tables**

| 2.1         | Coverability Tree Algorithm General Steps as described by C.G. Cassandras     |    |

|-------------|-------------------------------------------------------------------------------|----|

|             | and S. Lafortune in [2]                                                       | 21 |

| 3.1         | Inputs and Outputs of the IOPT Petri net that controls the alarm system       | 32 |

| 3.2         | Identification of DES Conditions (Places).                                    | 34 |

| 3.3         | Identification of DES Events (Transitions)                                    | 34 |

| 4.1         | Coverability Tree Algorithm Implementation.                                   | 42 |

| 4.2         | Transition Function Implementation.                                           | 43 |

| <b>B</b> .1 | New Inputs and Outputs necessary for the storytelling.                        | 72 |

| B.2         | Identification of Storyboard Conditions (Places). The storyboard generates no |    |

|             | outputs                                                                       | 72 |

| B.3         | Identification of Storyboard Events (Transitions).                            | 73 |

| D.1         | Coverability_Tree function description                                        | 84 |

| D.2         | transition_function function description                                      | 85 |

| D.3         | add_path function description                                                 | 86 |

## Chapter 1

## Introduction

Industrial processes are procedures involving chemical, physical, electrical or mechanical steps to aid in the manufacturing of an item. When each step or set of steps is thought of as the *state* of the process and the inputs given by a user or sensor as *events* defined at discrete time instants only, one can describe every industrial process as a *Discrete Event System* (DES). A DES is a method for the modelling of systems as sequences of operations (events) - it is described as a discrete-state and event-driven system. Reasons as to why discrete-time systems might be a good approach include the fact that any digital computer that might be used as a component of a system is equipped with an internal discrete-time clock, meaning variables or controls given are only evaluated at those time instants.

Programmable Logic Controllers (PLCs) are the most common devices for integrating and controlling industrial processes. PLCs are industrial solid-state computers that monitor inputs and outputs, and make logic-based decisions for automated processes or machines. PLCs are robust and can survive harsh conditions including severe heat, cold, dust, and extreme moisture. However, despite the widespread usage based on standard programming languages, it is still time consuming their direct programming.

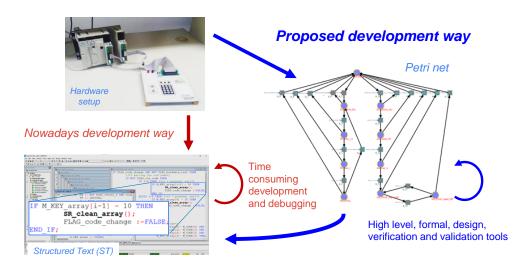

In this thesis, we focus on a more convenient way to create PLC program: convert higher level design (IOPT Petri nets) to PLC languages (Structured Text) [40, 41], as shown in Figure 1.1. However, there may be errors in the conversion from Petri net to Structured Text as well as conceptual errors in the Petri net design.

Figure 1.1: Automated conversion from high level Petri net to Structured Text as an faster alternative to direct PLC programming. May induce errors in the conversion as well as conceptual errors in the Petri net design.

## **1.1** Programming and Validation based on Petri nets

Features, properties and other information may be lost in translation, causing the PLC implementation to not be exactly the desired one. An incorrectly programmed PLC can result in lost productivity and dangerous conditions. Testing the project in simulation improves its quality, increases the level of safety associated with equipment and can save costly downtime during installation and commissioning of automated control applications since many scenarios can be tried and tested before the system is activated. A validation process must be imposed to check that the software system meets the specifications and fulfills its intended purpose.

The fact that PLCs work with scan cycles have to be considered in the assessment that the implemented system meets the purpose. The PLC scan cycle is formed by scanning inputs, then executing the program while inputs and outputs are kept unchanged, and finally generating the output signals. PLCs execute programs using the input values read at the end of the input scan cycle. Therefore, input signals can be seen as discrete events. The same occurs when output values. The PLC will receive the inputs given by sensors belonging to the real system and will provide output to actuators for the same system.

The modeling of a PLC as a discrete events system (DES) allows testing and verifying programs by using input sequences. In a digital environment one can simulate and inspect how

#### **1.2 Related Work**

the designed program responds and actuates. Simulation tools also need to be verified and validated to assure their correctness so it can best translate both the DES model and its response to inputs.

Many industrial processes based on PLCs can be seen as discrete event systems, which in turn can be represented by Petri nets. Then, resorting to a toolchain that converts a given Petri net to PLC Structured Text code as well as Petri net and PLC simulation tools, it is possible to model, analyse, implement and control these systems. Validation of the toolchain is therefore a necessary step towards evaluating its correctness and robustness, eliminating any bug that might misrepresent the DES model or its relation to inputs and outputs. Focusing on the Input-Output Place-Transition Petri net subclass, validation testing is done to the toolchain simulation processes and new utilities are added to improve its robustness.

## **1.2 Related Work**

Petri nets were first developed by C.A. Petri in the 1960s [39] for the purpose of describing automata communications. That doctoral thesis was followed by a series of papers by Petri himself and his research group on the applicability of Petri nets in other fields of science.

In 1969 [23], Karp and Miller wrote a paper on parallel program schemata and vector addition systems, also known as Petri nets, and dwelled on properties particular to parallel computation.

Later in 1981 [33], E. Mayer proved decidability for the reachability problem for Petri nets, a central problem of net theory. In the same year, due to the continuous increase of Petri net usage, J.L. Peterson published the first complete book [38] compiling the major parts of on Petri net theory scattered among many sources, presenting them in a coherent and consistent manner.

In 1986, a general formalization of Interpreted Petri nets was then established by Manuel Silva [43], where actuator signals and sensor signals are modeled as one or more input and output alphabets respectively.

Still regarding Petri Nets, Cassandras and Lafortune published a book in 2008 [2] intended to be a comprehensive introduction to the field of discrete event systems. This book is renowned within the academic community. It also contains an easily understandable description of the coverability tree algorithm that is used within this thesis.

In 2005, R. Pais, S. P. Barros and L. Gomes [36] developed a new Petri net class based on place/transition nets and well-known concepts from Interpreted Petri nets: the IOPT Petri net class [14]. This Petri net class allows the association of external input signals to transitions

and the association of external output signals to transitions and place markings. Additionally, the class provides support for the specification of input and output events. The same authors explored this concept for several applications in other works [17]. In one of them, in 2013 [37], they developed software to convert Petri Nets to VHDL that inspired Gonçalves, in 2015 [15], to explore a way to convert a Petri net into PLC programming language Structured Text (ST).

The IOPT Petri net authors also took part in developing a web-based IOPT Petri net tool that converts a Petri net to PNML [16], among other formats and utilities. Taking on the work of Gonçalves, the DES to PLC conversion toolchain was improved and worked up by J. Meleiro [35], R. Rei [40] and R. Reis [41].

## **1.3** Objectives and Challenges

In this thesis we propose validation tools for a toolchain that creates PLC programs, in Structured Text, from Petri nets. Are used IOPT Petri nets in order to include input and output, signals and events. The toolchain allows the simulation of the IOPT Petri nets in addition to the translation into Structured Text. Use and validation of the toolchain involves verification and validation of intermediate steps, including specific objectives and challenges:

- (i) Design IOPT Petri nets representing DESs performing tasks at hand. Challenges are found in using the IOPT web tool to design Petri nets modeling the intended DESs. In particular is important to properly read, translate and organize the data extracted from the tool, safeguarding all details and structure of the designed Petri net;

- (ii) Generation of the coverability tree as per Cassandras' algorithm [2] in order to detect unbounded Petri nets. Only bounded Petri nets are considered in this thesis. From the tree we obtain the sequence of events for testing. Obstacles laid in formulating the data structure to represent the tree while making available organized information to compile the sequence of events;

- (iii) Validating a Petri net with the necessary test sequences on a PLC or in simulation. Case study Petri nets are considered. Traditionally, this is a time consuming step, as developers are required to check each output of the simulation and compare it to the expected results. The challenge consists in finding and using, automatically, test sequences;

- (iv) Assessment of toolchain robustness to problems originated from the connection of digital systems to noisy, transient-prone, *bouncing* inputs. Solutions for the focused problem are also proposed.

### **1.4 Thesis Structure**

Chapter 1 introduces the problem to approach in the thesis, in particular it presents a short discussion on the state of the art of Petri Nets, the importance of PLCs in modern industry and the advantages of digitalisation for testing before implementation. Chapter 2 states the distinction between verification and validation. It also presents the relevant definitions and concepts regarding Petri nets and the coverability tree, as well as an algorithm to generate it. Moreover, some insight is given on the subject of Petri nets complemented with input and output. Chapter 3 introduces both the DES to PLC conversion toolchain to be verified and further developed and the chosen alarm case study. Chapter 4 contains the implementation of the coverability tree algorithm. It details the generation of event sequences and the extension of the Petri net model to include the notion of time. Chapter 5 provides an overview of three different use cases for the validation of the toolchain. Chapter 6 summarizes the work performed, its achievements, and proposes further work to extend the activities described in this document.

## **Chapter 2**

## Background

One of the objectives of this thesis is to implement and test the algorithm presented in [2] for constructing the finite version of an infinite reachability tree called a *coverability tree*.

In this chapter the issue of validation versus verification is addressed. The Petri Net mathematical modelling language is introduced and narrowed down to the class of Input-Output Place-Transition (IOPT) Petri Nets. After presenting the reachability problem as one of the central problems in Petri net theory, the concept of *coverability tree* is distinguished from *reachability tree*. The description and implementation of the aforementioned algorithm is then presented, preceded by the introduction of some necessary notation, and concluding with the testing of a few examples.

## 2.1 Verification vs Validation

Quality control is essential to building a successful business that delivers products that meet or exceed customers' expectations. It also forms the basis of an efficient business that minimizes waste and operates at high levels of productivity. Verification and Validation (V&V) are two of the most important terms in the industry when it comes to creating a process or product as they are mandatory steps for the quality management process: it makes sure that the process or product meets the purpose intended. Regulatory authorities like EMA (European Medicines Agency) and FDA (Food and Drug Administration) have published guidelines relating to process validation<sup>1</sup>.

Verification evaluates the on-going development phases and the product on regular basis

<sup>&</sup>lt;sup>1</sup>https://www.fda.gov/regulatory-information/search-fda-guidance-documents/ process-validation-general-principles-and-practices

against the specified requirements. Verification testing is a type of static testing, which means it involves the correct functioning of each part on its own. It can be seen as low level testing. The verification of system configuration can ensure system behavior is trusted if system components are configured properly. This means that all system services and applications should run as specified and contain no bugs or vulnerabilities that could be exploited to affect the functioning of the whole system.

Validation ensures that the product meets the predefined and specified business requirements as well as the end users/customers' demands and expectations. Validation testing is a form of dynamic testing, meaning it is performed in an environment where the code is actually executed. This testing takes on the final software product obtained after the development process, it can be seen as a high level testing.

The pharmaceutical industry is well know by its V&V standards, as ISO 9000. Electronics and computer hardware and software industries also follow similar terminology and body of knowledge<sup>2</sup>. For software systems it is called Software Verification and Validation (SVV) and has been formalised in IEEE 1012-2016 [3]. When it comes to PLCs, the IEC evaluates the complete projects of PLCs, including hardware, installation, testing, documentation, programming and communication, and develops International Standards for all electrical, electronic and related technologies.

In software project management, engineering and testing, the terms Verification and Validation are defined as the process of checking whether or not a software system meets specifications and fulfills its desired purpose. SVV for control systems can be simply addressed considering formal approaches or simulation. On the one hand, formal techniques are less used due to the complexity of formalisms and languages to be approached by the industrial user. Usually, implemented algorithms for PLCs use languages proposed in the standard IEC 61131-3 [22]. Even though the standard has harmonized how PLCs are programmed, the standardized languages do not force programmers to implement their algorithms in a formal way. Thus the definition of the control system formal model is not as simple and intuitive as to build a simulation model. On the other hand, simulation is a widely recognized and adopted technique for verification and validation of industrial automation systems. The main open problem of this approach is the definition of test cases to analyse the model in a complete and exhaustive manner.

While in formal verification [20, 21] are used formal methods of mathematics to prove or disprove the correctness of intended algorithms, we consider software tools associated to DES and Petri nets to confirm the specifications are met.

<sup>&</sup>lt;sup>2</sup>https://www.pmi.org/pmbok-guide-standards/foundational/pmbok/ software-extension-5th-edition

In this thesis, we focus on validation of the simulation processes of the DES to PLC conversion toolchain. We propose an automatic generation of the test sequence that helps us simulate the Petri net. Through manual comparison, since we know the expected evolution of the DES given a test sequence, we can test and analyse multiple critical cases to ensure the simulation environment behaves correctly.

### 2.2 Petri Nets

In this work, Petri nets are chosen for the description of DESs, since it is the most common representation for models of DES. Their basic characteristic is that they provide an excellent tool for capturing concurrency and conflict within a system. They have an appealing graphical and mathematical representation and they are well accepted when it comes to the implementation of tools [44].

#### Definition

A Petri Net is a collection of *oriented arcs* connecting *places* and *transitions*. Places may hold any non-negative number of *tokens*, having infinite capacity by default. The marking of a Petri net is a vector formed by the number of tokens in each place. The marking of all places characterizes the state of the Petri net. Arcs have weight 1 by default; if other than 1, the weight is marked on the arc. Arcs can only connect transitions to places and vice-versa, there are no arcs connecting transitions to transitions or places to places. Transitions are associated with events and can be fired, i.e., are enabled when the number of tokens in each of its input places is at least equal to the arc weight going from the place to the transition. An enabled transition may fire at any time. When fired, the tokens are subtracted from the the input places and are added to the output places, according to arc weights, resulting in a new marking of the net. This way tokens may disappear or be created.

The procedure of defining a Petri net involves two steps. First, the Petri net graph is defined, meaning the places, transitions and oriented arcs are drawn as desired. Places are graphically represented by circles, transitions by bars and oriented arcs by lines with an arrow setting orientation. Secondly, an initial set of marked places, also named *initial marking*, is added alongside a *transition function* resulting in the complete Petri net model and the corresponding dynamics as well as the languages that it generates and marks.

From [2], a Marked Petri net is formally defined as a five-tuple  $(P, T, A, w, \mu_0)$ , where

1. *P* is the finite set of places defined as  $P = (p_1, p_2, ..., p_n), n \in \mathbb{N}$

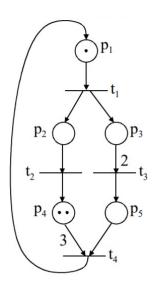

$(P, T, A, w, \mu_0)$   $P=\{p_1, p_2, p_3, p_4, p_5\}$   $T=\{t_1, t_2, t_3, t_4\}$   $A=\{(p_1, t_1), (t_1, p_2), (t_1, p_3), (p_2, t_2), (p_3, t_3), (t_2, p_4), (t_3, p_5), (p_4, t_4), (p_5, t_4), (t_4, p_1)\}$   $w(p_1, t_1)=1, w(t_1, p_2)=1, w(t_1, p_3)=1, w(p_2, t_2)=1$   $w(p_3, t_3)=2, w(t_2, p_4)=1, w(t_3, p_5)=1, w(p_4, t_4)=3$   $w(p_5, t_4)=1, w(t_4, p_1)=1$   $\mu_0 = \{1, 0, 0, 2, 0\}$

Figure 2.1: Example of a Petri net.

- 2. T is the finite set of transitions defined as  $T = (t_1, t_2, ..., t_m), m \in \mathbb{N}$

- 3. *A* is the finite set of arcs from places to transitions and from transitions to places in the graph defined as  $A \subseteq (PxT) \cup (TxP)$

- w is the weight function on the arcs defined as A → 1, 2, 3, ...; one assigned weight for each arc in A. The matrix comprised of all w(t<sub>j</sub>, p<sub>i</sub>) values is called the postconditions matrix D<sup>+</sup> and the matrix comprised of all w(p<sub>i</sub>, t<sub>j</sub>) is defined as preconditions matrix D<sup>-</sup>, with D<sup>+</sup>, D<sup>-</sup> ∈ ℝ<sup>nxm</sup>.

- 5.  $\mu_0$  is the initial state of the Petri net given by the markings of all the places. A Petri net state is defined as  $\mu = [\mu(p_1), \mu(p_2), ..., \mu(p_n)] \in \mathbb{N}^n$ .

For simplicity, a marked Petri net shall henceforth be referred to as just a Petri net. Figure 2.1 shows an example of a Petri net graphically represented.

Regarding the Petri net algebraic representation, Petri nets can be represented in matrix form by the *Incidence Matrix*  $D \in \mathbb{R}^{n \times m}$ , which in turn is obtained from the weight function w as seen in (2.1).

$$D_{ij} = w(t_j, p_i) - w(p_i, t_j)$$

, where  $i = 1, ..., n$  and  $j = 1, ..., m$ . (2.1)

The incidence matrix for Petri net in Figure 2.1 is given by

$$D = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} - \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 3 \\ 0 & 0 & 0 & 1 \end{bmatrix} \Leftrightarrow D = \begin{bmatrix} -1 & 0 & 0 & 1 \\ 1 & -1 & 0 & 0 \\ 1 & 0 & -2 & 0 \\ 0 & 1 & 0 & -3 \\ 0 & 0 & 1 & -1 \end{bmatrix}$$

(2.2)

In the interest of understanding the dynamics of Petri nets, the two following concepts must be introduced

- Enabled Transition. For a given marking, a transition t<sub>j</sub> is said to be enabled if all input places of t<sub>j</sub> contains at least the number of tokens equal to the weight of the directed arc connecting each input place to t<sub>j</sub>, i.e., μ(p<sub>i</sub>) ≥ w(p<sub>i</sub>, t<sub>j</sub>), ∀(p<sub>i</sub>, t<sub>j</sub>) ∈ w.

- 2. *Firing Rule*. Only enabled transitions may fire. The firing on an enabled transition  $t_j$  removes from each input place of  $t_j$  the number of tokens equal to the weight of the directed arc connecting each input place to  $t_j$ . It also deposits in each output place of  $t_j$  the number of tokens equal to the weight of the directed arc connecting  $t_j$  to each output place of  $t_j$ .

The Petri net dynamics is given by equation (2.4), also known as state transition mechanism. A state transition occurs by moving the tokens along the net according to the firing rule by firing an enabled transition. In Petri nets, enabled transitions may fire at any time. If more than one transition is enabled, the fired transition is chosen arbitrarily. The state transition function of a Petri net is defined through the change in the state of the Petri net due to the firing of an enabled transition.

The state transition function,  $f : \mathbb{N}^n \ge T \to \mathbb{N}^n$ , of Petri net  $(P, T, A, w, \mu_0)$  is defined for transition  $t_j \in T$  if and only if transition  $t_j$  preconditions are met. Mathematically it is written as in (2.3).

$$\mu(p_i) \ge w(p_i, t_j) \ \forall (p_i, t_j) \in w \tag{2.3}$$

If  $f(\mu, t_i)$  is defined, then the next state is given by

$$\mu' = \mu + D \cdot q(j), \tag{2.4}$$

where q is the firing vector, being q(j) a vector representing the firing of transition  $t_j$ .

For the scope of this thesis, another important observation about the dynamic of Petri nets must be made. It is not necessarily true that all states in  $\mathbb{N}^n$  can be reached by a Petri net model. It may also occur that different initial markings lead to a different set of states reached by the same Petri net. This leads to the defining of the Reachable set  $\mathscr{R}$  as being the set of all reachable states by the given Petri net for the given initial marking.

#### **Input and Output**

We want to validate the tool that converts a DES to a PLC program. After uploading the program to a PLC, one obtains a DES interacting with real systems. The Petri net representing the DES models just the structural information, state dynamics, of the system. In addition, it is important to test how the proposed DES responds to external inputs and acts on external outputs. To do so, we consider a class of Petri net that complements our common Petri net with input-output interactions. The following statements on the IOPT Petri net class mention only the characteristics necessary to learn how to use the IOPT tool software [16] to design an IOPT Petri net model abiding by the rules and conditions that must be met before feeding it to the DES to PLC conversion toolchain .

IOPT Petri nets [36] are based on Place-Transition nets and well-known concepts from Interpreted Petri nets and allow the specification of models with input and output signals and events. More specifically, it allows the association of input events to transitions and output events to places. The IOPT Petri net supports the specification of input and output events which simulate the readings of sensors and manipulation of actuators. The input and output signals guide the controller through each execution step by defining the system current state while the input or output events are associated to changes in input or output signals.

The IOPT Petri dynamics are very similar to the Petri net dynamics as explained in section 2.2. Regarding transition firing, now a transition has to be both *enabled* and *ready* to be firable. A transition is ready when the associated input event happen. After a transition fires, the marking changes according to the usual Petri net dynamics. If the marked places are associated with an output event, these events will be triggered and the corresponding output signal's value will change.

#### **Properties**

Modeling with Petri nets by itself is of little use. It is necessary to analyze the modeled system to better understand its behaviour. The objective of analysing a Petri net is to determine the answers to questions about the Petri net. To better understand the usefulness of Petri net analysis techniques we introduce the questions by stating the adjacent property. Let C be the Petri net defined by  $(P, T, I, O, \mu_0)$ .

1. **Safeness** - important property for Petri nets modeling hardware devices. If a place is safe, then the number of tokens in that place is either 1 or 0. The interpretation made is that of a place representing a logical condition, it is either correspondingly true or false making a place easily implemented as a flip-flop.

A place  $p_i \in P$  of C is safe if  $\forall \mu' \in R(C) : \mu'_i \leq 1$ .

A Petri net is safe if all its places are safe.

2. **Boundedness** - Safeness is a special case of the boundedness property. In this more general property, one can interpret a place as a counter. Any hardware counter has a limit to which it can count, therefore the boundedness of each place is relevant to prevent the hardware from malfunctioning.

Boundedness defines the maximum number k of tokens a place can hold. A place  $p_i \in P$  is k-bounded if  $\mu'_i \leq k \ \forall \mu' = (\mu'_1, ..., \mu'_i, ..., \mu'_N) \in R(C)$ .

A Petri net is k-bounded if all places are k-bounded.

3. **Conservation** - Petri nets can be used to model resource allocation systems. In these systems some tokens may represent said resources. A Petri net should conserve the resources which it is modeling, i.e., tokens that represent resources are neither created nor destroyed.

If for every marking the number of tokens remains the same, a Petri Net is strictly conservative. Mathematically

$$\sum_{p_i \in P} \mu'(p_i) = \sum_{p_i \in P} \mu(p_i)$$

- 4. Liveness The system transitioning into a deadlock is not desirable for obvious reasons. A deadlock in a Petri net is a transition (or a set of transitions) which can never fire. A transition is *live* if it is not deadlocked. This does not mean that the transition is enabled, but rather that it can be enabled. The liveness property studies the possibility of a given transition being able to eventually fire, or not. There are 5 levels of liveness. We say a transition  $t_i$  is live of

- Level 0 if it can never be fired (transition is Dead).

- Level 1 if it is potentially firable an upper-bounded number of times, that is, if there exists a μ' ∈ R(C) such that t<sub>i</sub> is enabled in μ'.

- Level 2 if for every integer n, there exists a firing sequence such that  $t_j$  occurs n times, i.e., the upper-bound number transition  $t_j$  can be potentially fired can be set by a certain firing sequence or by the repetition of a certain firing sequence.

- Level 3 if there exists an infinite firing sequence such that  $t_j$  occurs infinite times. This is the same as saying transition  $t_j$  can be fired an infinite number of times until the Petri net reaches a state where  $t_j$  can never fire again.

- Level 4 if the transition is live of level 1 for every possible state reached from μ<sub>0</sub>. In other words, if for each μ' ∈ R(C) there exists a sequence σ such that the transition t<sub>j</sub> is enabled (transition is Live).

- 5. **Reachability** When modeling a real system it is important to know if the systems reaches all expected steps of functioning or if a known deadlock can happen. Since these steps can be seen as states in the Petri net, the reachability problem arises from the need to know whether from the given initial marking there exists a sequence of valid execution steps that reaches the given final marking.

The common definition of the reachability problem is: given a Petri net C, does the marking  $\mu'$  belong to the set of all markings that can be obtained, i.e.,  $\mu' \in R(C)$ ?

6. **Coverability** - The coverability problem is similar to the reachability one. Answering this problem plays a central role in the verification of concurrent shared-memory programs.

Given a Petri net C and states  $\mu$ ,  $\mu' \in R(C)$ , then  $\mu'$  is covered by  $\mu$  if  $\mu'(p_i) \leq \mu(p_i) \forall p_i \in P$ .

7. **Temporal Invariance** - This property addresses the ability of a machine being able to return to a specific state from itself, if cycles of operation can be found. An example for a real system is the ability to to perform a reset on its own without external intervention. For a given Petri net C, one can infer the existence of temporal invariance if there exists a sequence of transitions fired that evolve the Petri net from each state to itself.

#### Petri Net Analysis, Method of Matrix Equations

The Method of Matrix Equations (MME) is based on the dynamics of the Petri net as seen in (2.4) and conditions are imposed to study each property. This methodology allows the immediate study of three of the above mentioned properties:

• Conservation - To maintain the (weighted) number of tokes one writes:

$$w^T \cdot \mu' = w^T \cdot \mu + w^T \cdot D \cdot q, \qquad (2.5)$$

where  $w^T$  is the vector of weights of each transition. As seen before, the total number of tokens can not vary, therefore  $w^T \cdot \mu' = w^T \cdot \mu$ . Since the total number of tokens is the same regardless of the transition firing vector q, one needs only to find the vector w such that

$$w^T \cdot D = 0. \tag{2.6}$$

$\exists w(t_i) > 0 \ \forall t_i \in T$  is a necessary and sufficient condition to prove the Petri net is conservative.

Reachability - Given the final state μ(k + 1) and the starting state μ(k), one can assess if state μ(k + 1) is reachable from state μ(k) by solving the equation of Petri net dynamics in order to the transition firing vector q, which is the only unknown.

$\exists q$  such that  $Dq(k) = \mu(k+1) - \mu(k)$  is a necessary condition to prove reachability for the presented conditions, but not sufficient to derive the correct order in which the transitions must be fired. Even if the system holds a solution it may not be possible to reach the desired state, since the MME mathematical description does not take into account restrictions found in the Petri net's dynamics. It can happen if, for example, for all possible order of transition firings the system evolves into a deadlock. The difficulty of finding a set of constraints that guarantees that the solution is feasible makes the reachability problem one of the main questions in Petri net theory, which will be discussed on section 2.3.

Temporal Invariance - Since one wants to determine the transition firing vectors that make the Petri net return to the same state one makes μ' = μ and hence one needs only to calculate the firing vector q such that

$$D \cdot q = 0. \tag{2.7}$$

$\exists q \text{ is a necessary to prove temporal invariance, but not sufficient to conclude on the correct firing vector.}$

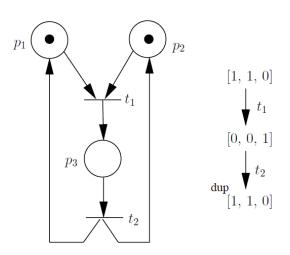

Figure 2.2: Example of a Petri net (left) and its corresponding reachability tree (right), if the initial marking is [1;0;0].

#### Petri net Analysis, Reachability Tree

The set of all states reachable by a Petri net C from the initial state  $\mu_0$  is called reachable set  $\mathscr{R}(C, \mu_0)$ . The reachability set can be graphically represented by a reachability tree. One can then say a reachability tree is a tree of reachable states. Each reachable state is represented by a node in the tree. The components used to build a tree are described in subsection 2.4.

As one can see in the example of a Petri net and its reachability tree shown in Figure 2.2, the transitions that are fired to change between states are also represented attached to the arcs in the tree, providing extra information such as the sequence of transitions needed to reach a state from any other, if possible.

Depending on the Petri net, more precisely, on whether the Petri net is bounded or unbounded, the reachability tree can be finite or infinite, correspondingly.

When the reachable set is finite it may be represented by the finite reachability tree, allowing the study of all previously enunciated properties.

When the reachable set is infinite the reachability tree becomes infinite. There exists a way of representing an infinite reachability tree in a finite form by introducing the infinity symbol  $\omega$  and the notion of *node dominance*, which are presented in section 2.4. The advantage of getting a finite representation is accompanied with loss of information regarding the reachability property. It is often possible, for instance, to determine that some state is not reachable, while being unable to check if some other state is reachable. Such instances give way to the reachability problem.

### 2.3 The Reachability Problem

The reachability problem is a decision problem, meaning it is a problem with yes or no answer. To solve a problem one develops procedures using computing resources. The formal descriptions of these procedures are called algorithms. A problem is said to be undecidable if there is no algorithm that takes as input an instance of the problem and determines whether the answer to that instance is yes or no.

The reachability problem for Petri nets consists of deciding, given a Petri net C with initial marking  $\mu_0$ , if a possible marking  $\mu$  can be reached from  $\mu_0$ , i. e. if  $\mu \in \mathscr{R}(C, \mu_0)$ .

This problem was first proposed by Karp and Miller [23] within the scope of Vector Addiction Systems, but left unsolved.

#### **Decidability of the Reachability Problem**

Hack [19] and Keller [24] observed that many other problems were recursively equivalent or reducible to the reachability problem turning it into on of the most studied decision problems in computer science theory.

Inspecting Esparza's research on decidability issues for Petri nets [9], we uncover that, after an incomplete proof by Sacerdote and Tenney [42], decidability of the problem was established by Mayr in his seminal STOC 1981 work [33]. Presenting a structure called *regular constraint graphs*, Mayr introduces an algorithm whose nondeterministic computation will determine if there is a firing sequence or not. Hence, a deterministic implementation of the algorithm provides a decision procedure for the general Petri net reachability problem. This algorithm uses a slightly modified version of Karp and Miller's original reachability tree construction [23] and is based on conditions given by Presburger's Arithmetic.

The proof was then simplified by Kosaraju [25]. Kosaraju does not add any "significantly new ideas", he just simplifies the proof by disposing of the complicated tree constructions used by Sacerdote and Tenney, and Mayr, introducing a "more general model o VASS's" known as *Generalized Vector Addiction Systems with States* (GVASS). Further refinements were made by Lambert [26], where he completely suppressed the use of Presburger's Arithmetic.

#### Lambert's proof outline

Lambert [26] introduced the concept of *Marked Graph-Transition Sequences* (MGTS), which are the result of the decomposition of the *precovering graphs* implicit in Mayr's and Kosaraju's proofs.

Lambert's algorithm finds a MGTS having some properties which allow the computation of a sequence belonging to its language. The language L of a MGTS is the set of the sequences firable in the Petri net R which are made of paths in the *initiated precovering graph* (IPG) of the *graph-transition sequences* (GTS) and respect the initial and the final markings of each IPG.

He states that if a MGTS on a Petri net R, with Ax = b as its characteristic equation, is *perfect* then it is possible to find any element of L. A MGTS is perfect if it contains a covering for both the initial and final marking, and if there exists a solution to the characteristic equation respecting the proper conditions.

Lambert proceeds to show how to compute the finite (possible empty) set  $\Gamma$  of perfect MGTS by decomposition of a MGTS  $\mathscr{U}_0$ , with marking  $\varphi_0$  as the pair  $(\mu_i, \mu_f)$ , on a Petri net R and initial an final markings  $\mu_i$  and  $\mu_f$ , respectively. This decomposition means

$$L(R,\mu_i,\mu_f) = L(\mathscr{U}_0,\varphi_0) \tag{2.8}$$

which is read as, for a Petri net R, the language of the sequences firable at  $\mu_i$  for which the resulting marking is  $\mu_f \in \mathbb{N}^P$  ( $\mathbb{N}^P$  =markings of Petri net R) is equal to the language of the MGTS  $\mathscr{U}_0$  on R, with marking  $\varphi_0$  as the pair ( $\mu_i, \mu_f$ ).

In other words, we can compute a finite (possible empty) set  $\Gamma$  of perfect MGTS having  $\mu_i$ and  $\mu_f$  as input and output marking such that

$$L(R,\mu_i,\mu_f) = \bigcup_{(\mathscr{U},\varphi)\in\Gamma} L(\mathscr{U},\varphi) \quad .$$

(2.9)

He states that reachability is decidable if the algorithm can compute for a Petri net R and two markings  $\mu_i$  and  $\mu_f$  a finite (possibly empty) set  $\Gamma$  of perfect MGTS. The algorithm is shown to converge as a consequence of the well-foundedness of multiset ordering [7] thus confirming decidability.

In the computer science community, the *decomposition technique* that lies at the heart of the proofs is called the Kosaraju-Lambert-Mayr-Sacerdote-Tenney (KLMST) decomposition.

#### Complexity

Regarding its complexity, Lipton showed in 1976 that the reachability problem's lower bound is EXPSPACE-hard [32].

Leroux made substantial progress over the past ten years [27, 28, 29] culminating in 2015 in the first upper bound on the complexity [30].

In 2019, Leroux and Schmitz [31] published a new upper bound to be non-primitive recur-

sive Ackermannian. Later in the same year, Czerwinski [4] established a non-elementary lower bound, i.e. that the reachability problem needs a tower of exponentials of time and space.

### 2.4 Coverability Tree

In 1969, R. M. Karp and R. E. Miller [23] introduced the *rooted tree*  $\mathscr{T}(\mathscr{W})$ , for any vector addition system  $\mathscr{W}$ , and the *infinity symbol*  $\omega$  terminology to help represent an infinite reachability set  $\mathscr{R}(\mathscr{W})$  in a finite form, in order to discuss effective tests of schemata properties.

Later in 1981, J. L. Peterson [38] used  $\omega$  to represent "a number of tokens which can be made arbitrarily large", that can be thought of as "infinity", and described an algorithm to reduce the infinite reachability tree to a finite representation. Peterson chose to name both the finite and the infinite reachability tree as reachability tree.

Finally, 1993, C. G. Cassandras and S. Lafortune [2] introduced the notation of *node dominance*, which the previous authors also used but did not label, to present the technique of the *coverability tree*. The authors named *coverability tree* as the finite representation of the infinite reachability tree, which contains the infinity symbol  $\omega$ .

In this work, the latter terminology is chosen since the implemented algorithm is based on theirs.

Note that seeking the finite version is always possible, meaning the algorithm always terminates, as proven in [38] who based the proof on [18] and [23].

Generating a coverability tree allows us to discard Petri net with an associated tree that contains the infinity symbol, which translates into an unbounded Petri net. Being presented with a bounded Petri net with a corresponding coverability tree containing no  $\omega$  one can obtain all possible sequences leading to all reachable states. Access to this information makes the creation of test sequences possible. We first introduce some notation to better comprehend the algorithm presented in [2] and then we explain the general steps.

#### Notation

Before describing the algorithm, some notation regarding the components used to build a tree must be introduced as to better understand the technique.

- 1. Node. Represent a reachable state of the Petri net.

- *Root node*. The node at the top of the tree structure, has no parent. Corresponds to the initial state of the Petri net.

- *Terminal node*. Also known as leaf node, does not have child nodes. Corresponds to a state with no enabled transitions (e.g., deadlock).

- *Duplicate node*. Corresponds to a state that is identical to a state already present in the tree. For a node to be considered duplicate, the already existing identical node must be in the path from the root node to the node under consideration. No successors of a duplicate node need to be considered; all these successors will be produced from the first occurrence of the node in the tree.

- 2. *Infinity symbol*  $\omega$ . Represents a number of tokens that can be made arbitrarily large. For any constant *a*

$$\omega \pm a = \omega$$

$$a < \omega$$

$$\omega \le \omega$$

The symbol  $\omega$  will appear as the marking of any unbounded place belonging to a state that *dominates* another.

- 3. *Node dominance*. Let any state  $\mu = [\mu(p_1), \mu(p_2), ..., \mu(p_n)]$ . Consider states  $\mu$  and  $\mu'$  belonging to the coverability tree and n the total number of places in the Petri net. If there is a node  $\mu'$  on the path from the root node to  $\mu$  such that

- (i)  $\mu(p_i) \ge \mu'(p_i), \forall i = 1, ..., n$  (state  $\mu$  covers state  $\mu'$ ),

- (ii)  $\exists i : \mu(p_i) > \mu'(p_i), \forall i = 1, ..., n$  (there exists at least one place of  $\mu$  that has more tokens than the corresponding place of  $\mu'$ ),

then  $\mu >_d \mu'$ , i.e.  $\mu$  dominates  $\mu'$ .

Allied with the infinity symbol, node dominance is the concept that allows the representation of the coverability tree (for an example see subsection 4.3.1).

#### **Algorithm Steps Outline**

The algorithm as presented in [2] builds a coverability tree for a given Petri net. The only information required from the Petri net is the preconditions matrix, post-conditions matrix and initial state. With both matrices one can obtain the incidence matrix needed for the state evolution according to the Petri nets dynamics equation. The tree starts out with the initial state, which is the first "new state".

For each new state, if there are no enabled transitions then the state is branded "terminal", since it cannot be expanded, otherwise the algorithm computes the next state for each one of the enabled transitions. One can think of each enabled transition as a branch on the tree.

Mark each new state according to the Petri net dynamics equation 2.4 and considering the  $\omega$  properties and node dominance. Correct the marking if *node dominance* is verified. The last step on each new state is to check if there already exists a state in the tree identical to this new state. If so, brand the new state as "duplicate". Else it stays branded "new state".

Repeat for all new states until all states have been branded as either "duplicate" or "terminal".

The general steps of the algorithm to construct the coverability tree are given on Table 2.1.

#### **Coverability Tree Algorithm - General Steps**

# **Input**: Preconditions matrix, post-conditions matrix and initial node **Output**: Coverability Tree

**Step 1** Initialize  $\mu$  as the root node (initial state):  $\mu_1 = \mu_0$ .

**Step 2** For each new node in  $\mu$ , evaluate the state transition function  $f(\mu_i, t_j)$  for all  $t_j \in T$ :

**Step 2.1** If  $f(\mu_i, t_j)$  is undefined for all  $t_j \in T$  (i.e., no transition is enabled at state  $\mu_i$ ), then mark  $\mu_i$  as a terminal node.

**Step 2.2** If  $f(\mu_i, t_j)$  is defined for some  $t_j \in T$  (i.e., there exists at least one transition enabled at state  $\mu_i$ ), for each enabled transition, create a new node  $\mu'$  with the marking as given by the state transition function ( $\mu' = f(\mu_i, t_j)$ ). Adjust as follows:

**Step 2.2.1** For each place in state  $\mu_i$  that is marked with  $\omega$  tokens, if there is any, set the corresponding place in  $\mu'$  with  $\omega$  tokens: for all  $\mu_i(p_i) = \omega$  found, set  $\mu'(p_i) = \omega$ .

**Step 2.2.2** If there exists a node y in the path from the root node  $\mu_0$  (included) to  $\mu'$  such that  $\mu' >_d y$ , set  $\mu'(p_i) = w$  for all  $p_i$  such that  $\mu'(p_i) > y(p_i)$ .

**Step 2.2.3** Else  $\mu'$  remains as obtained in **Step 2.2**.

**Step 2.2.4** If there already exists a state in the tree identical to  $\mu'$ , then mark  $\mu'$  as a duplicate node, else add  $\mu'$  to  $\mu$  as a new node.

**Step 3** Stop when all nodes have been marked as either duplicate or terminal.

Table 2.1: Coverability Tree Algorithm General Steps as described by C.G. Cassandras and S. Lafortune in [2].

## 2.5 Thesis Approach

We use Petri nets to model industrial processes, namely in the aspect of creating DES supervisors implemented on PLCs. More precisely, we use extended Petri nets, allowing the communication with real systems.

The extended Petri nets provide means for simulating the interactions between the PLC (implementing the Petri net) and the inputs and outputs associated to real world (PLC external) systems. In particular we use IOPT Petri nets which are converted to structured text (PLC programming language).

Besides converting a IOPT Petri net to Structured Text, the considered DES to PLC conversion toolchain also provides a MATLAB simulation environment that allows the testing and validation of the Petri net before implementation, as well as a PLC simulator.

The simulation environment is designed to work regardless of the modeled DES, however, as any environment created by a software tool, may have translation induced errors. The simulated Petri net may behave incorrectly even if the DES is properly modeled. We propose tools to assess the correctness of the PLC/DES implementations.

In this thesis we propose validation of the simulation environment through the study of three use cases on a alarm system based on a PLC. We also propose implementing the automatic generation of all possible cyclic input event sequences, extracted from the reachable set, to simulate all possible state evolutions. Knowing how the IOPT Petri net is supposed to react to each input event we can validate if the simulation is done correctly through the observation of the state evolution.

## **Chapter 3**

# **Implementation of Industrial Processes on PLCs using Petri Nets**

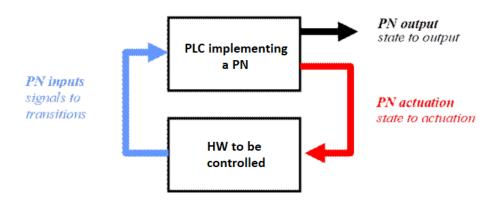

A PLC program implemented by a Petri net with I/O interacts with a system or, in other words, supervises a system. A Petri net typically has inputs at the transitions and outputs at the places. See in Figure 3.1 the arrows *PN actuation* meaning the outputs required to drive the system and *PN inputs* meaning the signals observed in the system and used to drive the Petri net. To run a Petri net it is required a real or a simulated supervised system that can handle the inputs and the outputs that make the interaction possible.

A DES to PLC conversion toolchain started to be developed by H. Gonçalves [15] based on the tools [12] and [13] presented in the Industrial Processes Automation course taught at Instituto Superior Técnico. In the years that followed, the toolchain was improved by J. Meleiro [35], R. Rei [40] and R. Reis [41]. Currently, the toolchain allows converting a Discrete Event Sys-

Figure 3.1: Petri net supervising the system HW to be controlled.

Figure 3.2: IOPT PN to ST Converter. A decision method to reject unbounded PN is added as well as to automatically generate testing sequences.

tem modeled by a Petri net into a PLC Structured Text program, and, in addition, provides a controlled simulation environment.

In this thesis is proposed an automatic generation of PLC-code to implement an industrial process represented by a Petri net, starting by assessing the net is bounded, in order to ensure the states have finite markings which translate directly to finite PLC representations. In addition, are proposed automatic tests to guide the PLC-program (controller) through all its states to confirm they are reachable.

This chapter is divided in two parts. On the first part we describe the DES to PLC conversion toolchain chosen as the object of analysis for this thesis (see Figure 3.2). On the second part we present the alarm system to be supervised.

## 3.1 DES To PLC Conversion Toolchain

Unbounded Petri nets imply infinite reachable sets, therefore do not allow exhaustive testing of the reachability set. We start by adding a decision method to reject unbounded nets to the PLC-code production toolchain (Figure 3.2). Given a bounded Petri net, we propose a method to automatically generate testing sequences.

#### **3.1.1 Finite Reachable Set**

As referred, we want to consider just bounded Petri nets since in those cases one finds finite reachable sets and can automatically generate sequence of events for testing the system. More in detail, we want to start by finding an algorithm to decide whether a Petri net is bounded. We start by the reachability problem introduced in section 2.3.

Given a Petri net C with initial marking  $\mu_0$ , the reachability problem consists of finding if a state  $\mu$  is in the reachable set, i.e.  $\mu \in \mathscr{R}(C, \mu_0)$ . This problem was shown to be decidable [33, 26, 9]. While approaching the reachability problem in [23], Karp and Miller introduced the *node dominance* concept to build a coverability tree. The coverability tree has a finite number of nodes, but may contain the symbol  $\omega$  indicating unbounded places on the Petri net. A coverability tree not containing  $\omega$  symbols indicates a bounded Petri net (see section 2.4).

Our proposal, complementing the DES to PLC conversion toolchain , involves two additional steps. The first step is to include a coverability tree construction algorithm in the toolchain to reject unbounded Petri nets, which are associated to coverability trees containing  $\omega$ . This is introduced in section 2.4 and is implemented in section 4.3.

The second step is to extract the finite sequence of transitions for testing, given a finite reachability tree, i.e. a coverability tree which has no  $\omega$  symbols as the Petri net did not require its use. We find operation cycles, avoiding therefore deadlock cases, and use sequences of transitions to assess whether the process code effectively reaches all possible states. This methodology is developed in section 4.4.

Before detailing the additional methodologies, we explain the DES to PLC conversion toolchain general steps.

#### 3.1.2 DES Implementation

We assume that the modelling of the DES is made by a system designer. More in detail, we assume the IOPT Petri net properly models the system and that the Petri net meets the format required by the toolchain. The already mentioned IOPT Tools is the only acceptable modelling program, at the moment. This web tool allows the download of the Petri net as a *pnml* extension file, which is the required file format.

We are only interested in bounded Petri nets. Unbounded Petri nets allow infinite length non-cyclic transition firing sequences; it would be impossible to test an DES modeled by an unbounded Petri net to its full extent. It would also be rather difficult to choose the set of most important and sufficient sequences to properly verify and certify each DES independently in an automatic manner, let alone generalize the extraction of such sequences to be independent of the DES. By creating a coverability tree, we can automatically discard Petri nets that originate a tree containing the  $\omega$  symbol, which means the Petri net is unbounded.

Another reason to focus solely on bounded Petri nets is their direct translation to the PLC programming language *Sequential Function Charts* (SFC) (also known as Grafcet or IEC 60848), which in turn is equivalent and easily mapped to all other PLC programming languages [6], assuming that the ambiguities of the standard are first resolved [1]. In the best case scenario (safe Petri nets), a Petri net place corresponds directly to a step on Grafcet. In the worst case scenario (k-bounded Petri nets), the steps on Grafcet will relate one to one to the reachability tree nodes, i.e. the Grafcet will have as many steps as nodes in the tree.

Before describing the toolchain steps, note that the toolchain offers some options of usage, one of which is worthy of mentioning for the scope of this thesis: the user has the option of setting a simulation that considers timed transitions or normalize all transitions to non-timed.

We present below the general steps of the DES to PLC conversion toolchain, accompanied a block diagram of the complete process to convert an IOPT Petri net to ST and its testing on Unity Pro presented in Figure 3.3. For more detailed information on the functions used in each step, please refer to the master thesis [15, 35, 40, 41] and the tools [12, 13].

**Data extraction** The first step of the toolchain starts with extracting all the information it requires from the IOPT Petri net prototype and parse it. It produces lists of related information about the Petri net's places, transitions, arcs, input signals, output signals, and determines both the preconditions and postconditions matrices and initial marking matrix.

In this thesis we added three new utilities within this parsing function. Now, it is also responsible for defining timed transitions for simulation as well as attributing a time delay to each type of input. It also attributes initial values to the input signals according to their initial definition in the IOPT Petri net. Finally, this tool can now identify a *storyboard*.

**Computing Coverability Tree [Added]** The second step of the toolchain is to compute the coverability tree. This is done using the preconditions and postconditions matrices stored as well as the initial marking as input to the coverability tree construction algorithm, which is explained in detail on subsection 4.3. This function implements a version of Cassandra's algorithm for constructing the coverability tree and outputs a structure MP containing all information pertaining said tree (refer to section 4.3 for more detail on MP). The main function uses three subroutines:

• transition function, returns the adjusted marking of the new node by checking node

dominance and infinity symbol carrying. More detail on its implementation please refer to Table 4.2.

- add path, adds a new sequence of transitions fired or nodes achieved on the path from the root node to the current node under evaluation. Returns the updated structure of path sequences.

- **tracker**, returns the updated structure that records essential information to generate the dot file used by Graphviz. This file is used to generate a visual representation of the coverability tree.

**Computing Test Sequence [Added]** An internal function receives as input the MP structure and extracts all sequences of transitions fired that allow the Petri net starting at a given initial state to return to that same initial state, performing a soft-reset. Then it compiles a table  $U_t$  that represents the timeline for the input events to happen. I.e., it assigns chronological timestamps to input signals changes so that the Petri net evolves in accordance to the cyclic sequences of transitions.

Each row in table  $U_t$  contains a timestamp on the first column. The other columns are paired consecutively two by two representing the OFF and ON component of each input signal, respectively. On each of these columns, the integers represent the values to be set for each component.

More detail on the computation of both the test sequence and the table of events on section 4.4.

**Model Simulation** The Petri Net simulator used is an adaptation of the one found in [13]. Note that for the original simulator, the user is responsible for creating the entire testing sequence (see vector tu, in the function filename\_IO, in philosophers example of [13]). For this toolchain, a custom table  $U_t$  can be provided by the user.

The simulation of a Petri net consists of two main steps namely (i) the verification that the preconditions are met and (ii) the state evolution after selecting just the possible-to-fire events.

A loop is run where each iteration corresponds to a time value (default is 0.5 seconds). This can be interpreted as the scanning times. The simulation loops over the following actions:

• Handling Outputs - updates the timers assigned to the transitions and returns an array containing the information on how to actuate on the hardware for that iteration, given the marking of the places;

- Enabled Transitions finds the transitions that are enabled at the current time of the loop. This is achieved by comparing the transitions enabling conditions against the hardware inputs and the readied timers at the time instance;

- Filter Possible Firings compares the enabled transitions with the marked places from the previous loop iteration, taking into consideration the Petri net's incidence matrix, and finds the transitions that are ready. The program triggers the readied transitions and updates the marking of the places.

**ST compiler** The method chosen to transcribe Petri net to ST, creating a PLC program from a Petri Net and IO mapping, uses three auxiliary functions to prepare a problem's specific data, like timed transitions and physical inputs or outputs, to be used straightforward by the main script. The auxiliary functions enable the following: (1) Load a Petri Net from file, that contains the incidence matrix and the Petri net's initial marking; (2) Define the mapping of PLC inputs to PN transitions, creating a structure with the PLC inputs and the selected corresponding transitions, and with the conflicts between transitions; (3) Define the mapping of PN places to PLC outputs, creating a structure with the outputs that should change value when the places are marked.

- **PN definition** loads a Petri Net from a file that contains the incidence matrix and the Petri net's initial marking and splits D into postconditions matrix D+ and preconditions matrix D-. Next, the priority and timed transitions are declared. Finally, all the previous information is stored on a structure, that is the Petri net representation of this program.

- **Input mapping definition** defines the system inputs that trigger each untimed transition. There are transitions that are triggered due to the conjugation of multiple inputs, or due to the negation of some inputs. Each untimed transition is represented as an entry on the cell array which contains all the input mappings.