# Back-Projection Algorithm Optimization for On-Board Embedded SAR Imaging System

## **Afonso Miguel Soares Fernandes**

Thesis to obtain the Master of Science Degree in

# **Electrical and Computer Engineering**

Supervisors: Prof. José João Henriques Teixeira de Sousa,

Dr. Rui António Policarpo Duarte

## **Examination Committee**

Chairperson: Prof. Francisco André Corrêa Alegria Supervisor: Prof. José João Henriques Teixeira de Sousa Member of the Committee: Prof. Mário Pereira Véstias

January 2021

ii

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

# Acknowledgments

This thesis is integrated in the FCT project "Synthetic Aperture Radar Robust Reconfigurable Optimized Computing Architecture" (SARRROCA) with reference PTDC/EEI-HAC/31819/2017.

With thanks to Dr.Rui Duarte for his guidance, and Prof.Horácio Neto for always finding time for my curiosities.

## Resumo

O Radar de Abertura Sintética (SAR) é um radar capaz de criar imagens coerentes de alta resolução. Para produzir imagens a partir de informação recolhida por um SAR é necessário usar um algoritmo de formação de imagem. Backprojection é um algoritmo conhecido por gerar imagens de alta qualidade com a desvantagem de ser computacionalmente intensivo. Devido a esta desvantagem o Backprojection nunca foi adoptado em aplicações em tempo real ou em dispositivos de baixo consumo energético e dimensões e poder computacional reduzido.

O primeiro contributo deste trabalho é o estudo do algoritmo Backprojection e a sua conversão para fixed-point. A caracterização temporal foi feita através de profiling. Para fazer a conversão foram conduzidos dois estudos de forma a escolher os parâmetros do formato fixed-point.

O segundo contributo é a implementação do algoritmo Backprojection num dispositivo System-on-Chip (SoC) Field Programmable Gate Array (FPGA). A implementação deve ser capaz de produzir uma imagem de 512 x 512 pixeis por segundo. A optimização é focada na aplicação e uma arquitectura pipeline.

Usando uma placa Zybo Z7-10 foi possível implementar o sistema de processamento capaz de produzir uma imagem com um SNR de 99.21 dB em apenas 959ms. Sendo o dispositivo escolhido da gama mais baixa, este trabalho comprova o enorme potencial que esta família de dispositivos tem no futuro do processamento de imagem em tempo real.

**Palavras-chave:** Synthetic Aperture Radar, Backprojection, FPGA, ponto fixo, projecto HW/SW, optimização

## Abstract

The Synthetic Aperture Radar (SAR) is a type of radar capable of high-resolution coherent Imaging. To produce images from SAR data, an image forming algorithm must be used. The Backprojection Algorithm is known for generating high resolution images at the expense of computational intensity. Due to this drawback, the Backprojection Algorithm has never been widely adopted for real time applications or implementation in Small, Weight and Power (SWaP) devices.

The first contribution of this work is the analysis and fixed-point conversion of the Backprojection Algorithm while providing high-quality images. The time characterization was done by means of profiling. To perform the fixed-point conversion two studies were conducted in order to set the parameters of the fixed-point format.

The second key contribution of this work is the implementation of the Backprojection algorithm in a System-on-Chip (SoC) Field Programmable Gate Array (FPGA) device. The implementation should be capable of producing an image with 512 per 512 pixels, per second. The optimization is focused on the development of a pipeline architecture.

Using a Zybo Z7-10 board it was possible to achieve a successful design, capable of producing an image with a signal-to-noise ratio of 99.21 dB in 959ms. With the target system being an entry-level device this works proves that these devices have an immense potential in the future of image processing for real-time applications.

**Keywords:** Synthetic Aperture Radar, Backprojection, FPGA, fixed-point, optimization, Hw/Sw system design

# **Table of Contents**

| Acknowledgments                                 | iii  |

|-------------------------------------------------|------|

| Resumo                                          | vii  |

| Abstract                                        | ix   |

| Table of Contents                               | xi   |

| List of Figures                                 | xiii |

| List of Tables                                  | xv   |

| Acronyms                                        | xvii |

| 1 Introduction                                  | 1    |

| 1.1 Motivation                                  | 1    |

| 1.2 Scope and Objectives                        | 2    |

| 1.3 Contributions                               | 2    |

| 1.4 Structure and Organization                  | 3    |

| 2 Background and State of the Art               | 5    |

| 2.1 SAR                                         | 5    |

| 2.1.1 Functioning Principles                    | 6    |

| 2.1.2 Image Formation Algorithms                | 7    |

| 2.1.2.1 Backprojection Algorithm                | 8    |

| 2.1.2.2 Image Quality Assessment                | 11   |

| 2.2 Reconfigurable Hardware                     | 12   |

| 2.2.1 Zybo Z7-10                                | 13   |

| 2.3 Numeric Formats                             | 15   |

| 2.3.1 Floating-Point                            | 15   |

| 2.3.2 Fixed-Point                               | 16   |

| 2.3.3 Numeric Format Comparison                 | 17   |

| 2.4 Approximate Computing Techniques            | 18   |

| 2.4.1 Square Root                               | 18   |

| 2.4.1.1. Newton-Raphson                         | 18   |

| 2.4.1.2 Binary restoring square root extraction | 19   |

| 2.4.2 Trigonometric Functions                   | 20   |

| 2.4.2.1 CORDIC                                  | 21   |

| 2.4.2.2 Taylor Series                           | 23   |

| 3 Optimization Methodology                      | 25   |

| 3.1 Algorithm Profiling                         | 25   |

| 3.2 Hardware/Software Partition                 | 28   |

| 3.3 Word-Length Optimization                    | 30   |

| 3.4 Resource Utilization Study                  | 33   |

| 3.5 Algorithm Rescheduling                      | 38   |

| 4 Propos  | ed System Architecture                                                          | 41 |

|-----------|---------------------------------------------------------------------------------|----|

| 4.1       | Memory                                                                          | 42 |

| 4.1.      | 1 Memory Units                                                                  | 43 |

| 4.1.      | 2 Memory Accesses                                                               | 44 |

| 4.2       | Algorithm Execution Circuit                                                     | 47 |

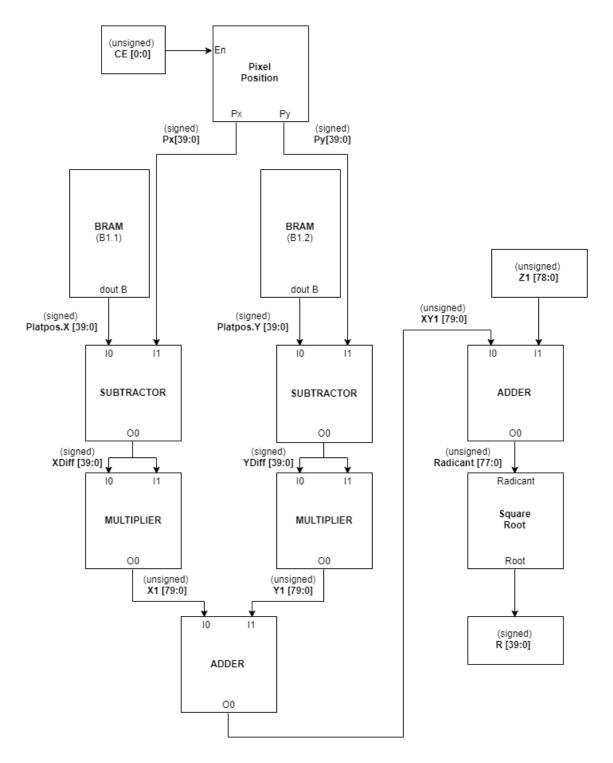

| 4.2.      | 1 Distance Module                                                               | 48 |

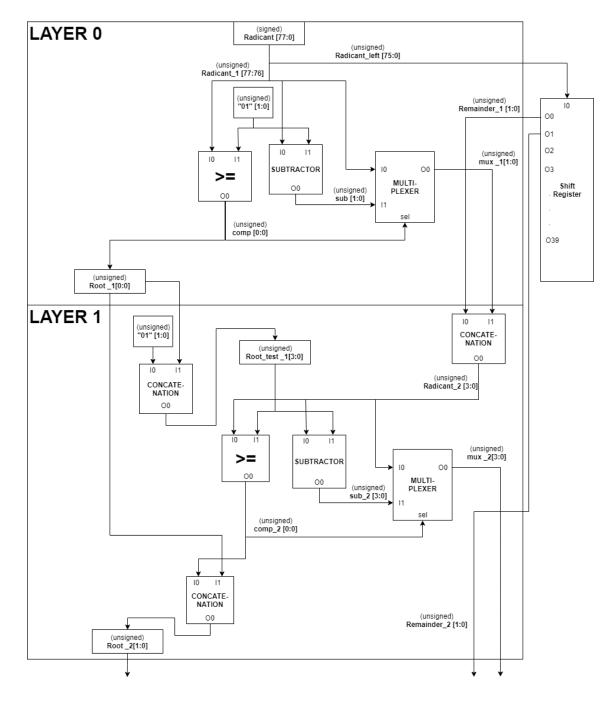

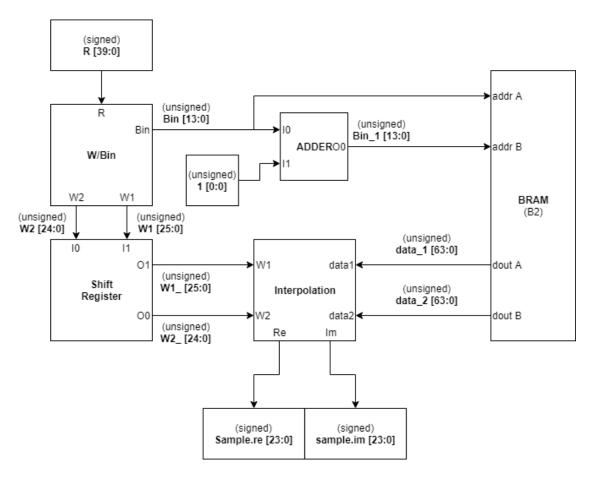

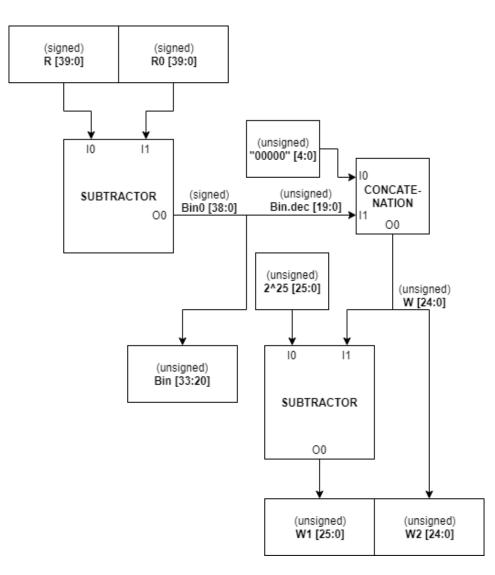

| 4.2.      | 2 Samples Module                                                                | 53 |

| 4.2.      | 3 Filter Module                                                                 | 57 |

| 4         | 2.3.1 Alternative Filter Module                                                 | 60 |

| 4.2.      | 4 Complex Multiplication Module                                                 | 61 |

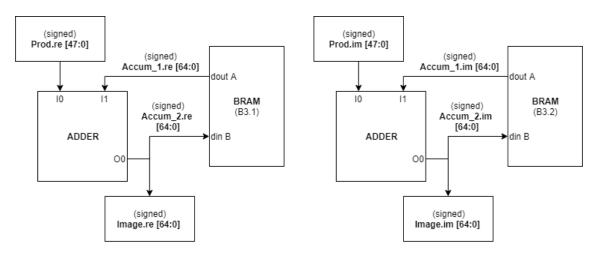

| 4.2.      | 5 Accumulator Module                                                            | 63 |

| 4.3       | System Control                                                                  | 64 |

| 5 Results |                                                                                 | 65 |

| 5.1       | SNR                                                                             | 65 |

| 5.2       | Resources                                                                       | 67 |

| 5.2.      | 1 Programmable Logic Resources                                                  | 68 |

| 5.2.      | 2 CPU and Memory                                                                | 69 |

| 5.3       | Timing and Latency                                                              | 69 |

| 5.4       | Energy Consumption                                                              | 70 |

| 6 Conclu  | sion                                                                            | 71 |

| 6.1 Fu    | ture Work                                                                       | 72 |

| Referenc  | es                                                                              | 73 |

| Appendi   | x A – Word-length study results                                                 | 77 |

| Appendix  | B - Area models for basic arithmetic operators with operands of different sizes | 81 |

| Appendix  | C – Fixed-point formats for circuit signals                                     | 85 |

# List of Figures

| Figure 1-RADARSAT-1 100-metre resolution mosaics of the Canadian provinces over a brief      |    |

|----------------------------------------------------------------------------------------------|----|

| seven-day period in January 1999 (https://www.nrcan.gc.ca/earth-sciences/geomatics/satellite | э- |

| imagery-and-air-photos/sensors-and-methods/synthetic-aperture-radar/10968)                   | 6  |

| Figure 2 - SAR's functioning principle [10]                                                  | 7  |

| Figure 3 - SAR data flow [9]                                                                 | 8  |

| Figure 4 - Pseudocode of the Backprojection Algorithm [15]                                   | 10 |

| Figure 5 - Pseudocode to compute the SNR of an Image [16]                                    | 11 |

| Figure 6 - Overview of the Zynq APSoc Architecture [26]                                      | 14 |

| Figure 7 - Word structure of a number in Floating-Point format                               |    |

| (https://courses.physics.illinois.edu/cs357/sp2020/notes/ref-4-fp.html)                      | 15 |

| Figure 8 - Word structure of a number in Fixed-Point format [30]                             | 16 |

| Figure 9 - Floating-Point Multiplication Architecture [29]                                   | 17 |

| Figure 10 - Rotation of a vector by an arbitrary angle                                       |    |

| Figure 11 - Graphic representation of the profiling results of the zybo board from table 4   |    |

| Figure 12 - Overview of the proposed system's partition                                      |    |

| Figure 13 - Snippet of code responsible for performing the error inducing operation          | 32 |

| Figure 14 - Proposed system architecture, discriminating memory units and inter-system       |    |

| communication.                                                                               |    |

| Figure 15 - AXI DMA IP core configuration in Vivado Environment                              |    |

| Figure 16 - Hardware Accelerator Top-Level Architecture                                      |    |

| Figure 17 -Simplified Distance module block design.                                          |    |

| Figure 18 - Simplified Square Root module block design.                                      |    |

| Figure 19 - Simplified Sample module block design.                                           |    |

| Figure 20 - Simplified WBin module block design                                              |    |

| Figure 21 - Simplified Interpolation module block design.                                    |    |

| Figure 22 - Simplified Filter module block design.                                           |    |

| Figure 23 - CORDIC IP core configuration                                                     |    |

| Figure 24 - Simplified Alternative Filter module block design.                               |    |

| Figure 25 - Simplified MultC module block design.                                            |    |

| Figure 26 - Simplified Accumulator module block design.                                      |    |

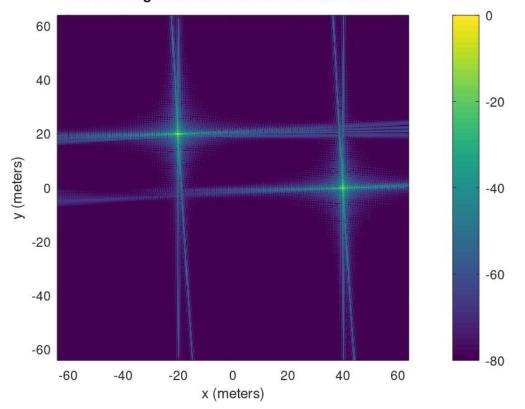

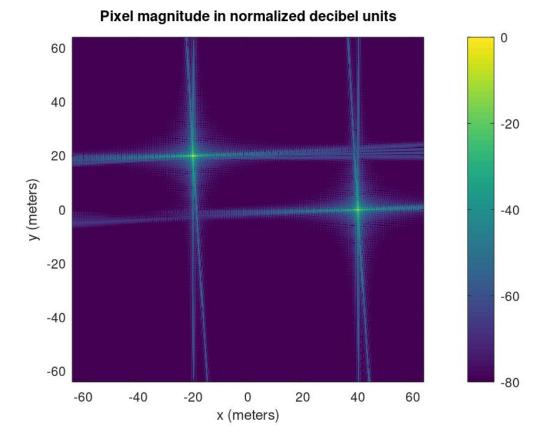

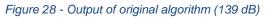

| Figure 27 - Image correspondent to the golden reference                                      |    |

| Figure 28 - Output of original algorithm (139 dB)                                            |    |

| Figure 29 - Output of the fixed-point algorithm with the largest word-lengths (183 dB)       |    |

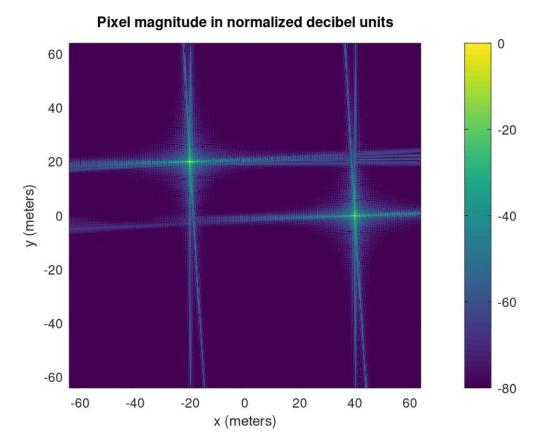

| Figure 30 - Output of the final Hardware/Software implementation (99.21 dB)                  | 67 |

# **List of Tables**

| Table 1 - Zybo Z7-10 PL main resources. [22]                                                   | . 13 |

|------------------------------------------------------------------------------------------------|------|

| Table 2 - Computer Specifications and Configuration                                            | . 25 |

| Table 3 - Target device Specifications and Configuration                                       | . 26 |

| Table 4 - Profiling results of the C language implementation of the Backprojection Algorithm . | . 26 |

| Table 5 - Hardware / Software partition                                                        | . 28 |

| Table 6 - SNR (dB) obtained for each word-length combination studied                           | . 31 |

| Table 7 - SNR (dB) obtained for the word-length combinations closest to the threshold          | . 32 |

| Table 8 - Resources used by support IP cores*                                                  | . 34 |

| Table 9 - Breakdown of resource estimate for system with input variables of width of 64 bits   | . 35 |

| Table 10 - Resources required by Estimate A                                                    | . 35 |

| Table 11 - Breakdown of resource estimate for system with input variables of optimal width     | . 36 |

| Table 12 - Resources required by Estimate B                                                    | . 36 |

| Table 13 - Estimate of memory capacity required to store all input values in BRAMs in the PL   | -    |

| system                                                                                         | . 37 |

| Table 14 - Estimate of memory capacity required to store all output values in BRAMs in the R   | PL   |

| system                                                                                         | . 37 |

| Table 15 - Estimate of BRAM cells required to store all input/output values                    | . 37 |

| Table 16 - Pseudocode of the loop hierarchy for the schedules studied                          | . 39 |

| Table 17 - Overview of the schedules' requirements and implementation details                  | . 39 |

| Table 18 - Input files format and size                                                         | . 43 |

| Table 19 - BRAM modules configurations                                                         | . 44 |

| Table 20 - Distance module composition in terms of basic arithmetic IP cores                   | . 50 |

| Table 21 - Correspondence between C code variables and circuit signals for the square root     |      |

| implementation*                                                                                | . 53 |

| Table 22 - Interpolation module composition in terms of basic arithmetic IP cores              | . 57 |

| Table 23 - Filter module composition in terms of basic arithmetic IP cores                     | . 58 |

| Table 24 - MultC module composition in terms of basic arithmetic IP cores                      | . 62 |

| Table 25 - Accumulator module composition in terms of basic arithmetic IP cores                | . 63 |

| Table 26 - Resources used in PL by the whole system                                            | . 68 |

| Table 27 - DDR and RAM memories occupancy through the execution (PS memories)                  | . 69 |

| Table 28 - Slowest Datapaths between 2 endpoints, in the circuit                               | . 69 |

| Table 29 - Latency of the Top-Level modules                                                    | . 69 |

| Table 30 - Power consumption discriminated by component of the target device                   | . 70 |

| Table 31 - Results from Word-length study of Constants                                         | . 77 |

| Table 32 - Results from Word-length study of the Distance group variables                      | . 77 |

| Table 33 - Results from Word-length study of Sample group variables                            | . 78 |

| Table 34 - Results from Word-length study of Filter group variables                            | . 79 |

| able 35 - Results from Word-length study of Complex Multiplication group variables | 79 |

|------------------------------------------------------------------------------------|----|

| able 36 - Resources used by a multiplier, latency = 0, implemented with DSP        | 81 |

| able 37 -Resources used by an adder, latency = 0, implemented with LUT             | 81 |

| able 38 - Resources used by a multiplier, latency = 1, implemented with DSP        | 81 |

| able 39 - Resources used by an adder, latency = 1, implemented with LUT            | 82 |

| able 40 - Resources used by an adder, latency = 1, implemented with DSP            | 82 |

| able 41 - Resources used by a multiplier, latency = 2, implemented with DSP        | 82 |

| able 42 - Resources used by a multiplier, latency = 3, implemented with DSP        | 82 |

| able 43 - Resources used by a multiplier, latency = 4, implemented with DSP        | 83 |

| able 44 - Resources used by a multiplier, latency = 5, implemented with DSP        | 83 |

| able 45 - Resources used by a multiplier, latency = 6, implemented with DSP        | 83 |

| able 46 - Resources used by a multiplier, latency = 7, implemented with DSP        | 83 |

| able 47- Fixed-Point formats of the signals in the figures in section 4.2          | 85 |

|                                                                                    |    |

# Acronyms

- AMBA Advanced Microcontroller Bus Architecture

- APSoC All Programmable SoC

- ASIC Application Specific Integrated Circuit

- AXI Advanced eXtensible Interface

- BRAM Block RAM

- CPU Central Processing Unit

- CORDIC Coordinate Rotation Digital Computer

- DDR Double Data Rate

- DMA Direct Memory Access

- DSP Digital Signal Processor

- FIFO First In, First Out

- FPGA Field Programable Gate Array

- IEEE Institute of Electrical and Electronics Engineers

- ILA Integrated Logic Analyser

- IP Intellectual Property

- IST Instituto Superior Técnico

- GP General Purpose

- GPU Graphics Processing Unit

- HP High-Performance

- LSB Least Significant Bit

- LUT Look-Up Table

- MSB Most Significant Bit

- PC Personal Computer

- PL Programmable Logic

- PLL Phase-Locked Loop

- PS Processing System

- RAM Random Access Memory

- SAR Synthetic Aperture Radar

- SLAR Side-Looking Aperture Radar

- SNR Signal-to-Noise Ratio

# **1** Introduction

This work was developed in the scope of a master's thesis to conclude the IST Integrated Master's in Electrical and Computer Engineering course. The thesis is integrated in the Synthetic Aperture Radar Robust Reconfigurable Optimized Computing Architecture (SARRROCA) project (PTDC/EEI-HAC/31819/2017).

The overarching goal of this project is to promote mass adoption of Synthetic Aperture Radar (SAR) imagery and its deployment on aircraft by providing reliable, portable and lighter computational on-board systems to produce real-time SAR images. This will be achieved by coupling known optimization techniques with the flexibility, power efficiency and performance of System-on-Chip (Soc) Field-Programable Gate Arrays (FPGA).

The SAR is a complex imaging data collection system with diverse sensing applications. It captures several target parameters, providing unique information that complements standard optical remote sensing methods, which can use a wide range of image formation algorithms. The Backprojection algorithm is one of the most well-suited for use in non-ideal conditions, as its working principle overcomes most of the obstacles that others can only compensate for. Being a high-quality image formation algorithm also implies being a complex and resource-intensive algorithm. For these reasons, the optimization of the Backprojection algorithm is an active field of research [1].

The main goal of this work is the optimization of the Back-Projection Algorithm for On-Board Embedded SAR Imaging System.

## 1.1 Motivation

Radar data has historically been used to advance the Earth study science, with applications in areas ranging from resource identification and monitoring, to landscape mapping and monitoring of the Earth's natural changes.

However, radar data is also expensive and complicated to use. The advances in the past decades in this area have broadened the scope of radar uses, allowing satellite remote sensing datasets to be used in a series of applications as an option for sustainable and replicable methods

Technological advances in electronic appliances have unveiled unique opportunities that take advantage of the enhanced data processing capacity of simple devices, like FPGA, allowing the exploitation of algorithms operating in real time applications using a small, lightweight, mobile, energetically efficient and battery-powered device, which is an ever growing need [2].

The advantages of coupling data collection with image formation techniques in the devices is the reduced time consumption for image processing at the receivers [1]. This allows

the widespread use of these devices and technology in applications such as surveillance radars and mapping of natural resources and geological structures, among others.

## 1.2 Scope and Objectives

The Backprojection Algorithm is an algorithm capable of generating high quality images of the Earth's surface. However, it is one of the most computationally intensive image formation algorithms which has led to it being overlooked for real time applications (especially in small, light and power efficient platforms) [3].

The purpose of this work is to develop a Hardware/Software implementation of the Backprojection Algorithm capable of producing a 512x512 pixels image per second, using a small, lightweight, power-efficient device. At the same time, this work aims to build a generalized methodology for optimizing algorithms.

The developed architecture implements the Backprojection Algorithm for image formation using SAR data samples. The architecture is composed of a hard-core Central Processing Unit (CPU) coupled with FPGA fabric, forming a Soc device. The target device used in this work is the Zybo Z7-10 (Digilent.inc, Washington, USA) which has a Zynq 7000 FPGA containing a dual-core ARM Cortex-A9 processor and Programmable Logic (PL) in which custom hardware will be implemented. The advantages brought by the target device chosen coupled with the use of fixedpoint arithmetic will allow the implementation to surpass the previous software implementations without compromising too much the quality of the output. This work will accompany the development of this system with all the studies performed to guarantee reproducibility for optimization studies of a range of algorithms.

## 1.3 Contributions

The main contributions of this thesis are:

- Wordlength study of the Backprojection algorithm;

- Conversion of the algorithm from floating-point to fixed-point;

- Development of a methodology for algorithm optimization

- Hardware/Software (Hw/Sw) implementation of the Backprojection algorithm in a SoC device.

## 1.4 Structure and Organization

This thesis is structured in six chapters:

Chapter 1: Motivation, objectives, main contributes and structure of this work are described.

Chapter 2: Presents context and the basic knowledge about SAR, Backprojection Algorithm, Reconfigurable Hardware and numeric formats needed in the scope of this work. It concludes by presenting the approximate techniques used in the acceleration of the algorithm.

Chapter 3: Presents the studies performed to the Backprojection Algorithm and its implementation in the C language, along with a study about the target system. This chapter includes a profiling study, a word-length study, a resource study and a schedule study.

Chapter 4: The full implemented architecture is described in detail. The chapter focus is on the Datapaths, the resources used and the timing considerations of the modules.

Chapter 5: Presents the results obtained in terms of output quality, energy consumption, performance and resources used, and the respective analysis.

Chapter 6: Presents the conclusions drawn from the work and discusses future work.

## 2 Background and State of the Art

This chapter introduces the state of the art for this work. It begins by introducing the SAR technology in terms of main characteristics, functioning principle, image formation algorithms and image quality evaluation, with emphasis on the image formation algorithm chosen for this work, the Backprojection algorithm. The chapter continues by presenting the reconfigurable hardware technology, presenting its advantages and disadvantages when compared to common computer systems and Application Specific Integrated Circuits (ASICS). Following is the numeric format section, in which the floating-point and fixed-point representations are presented and compared in the context of this work. The chapter finishes with an explanation of the approximate computing techniques studied for use on the implementation of the square root operation and trigonometric functions.

## 2.1 SAR

The SAR is a type of coherent radar capable of high-resolution coherent imaging [4][5]. This type of radar uses the relative motion between itself and the target to generate high resolution 2-D or 3-D images, making it ideal for mounting on moving platforms such as satellites, aircrafts or drones [1][4][6]. In development since the 1950's, it has since then evolved into a powerful and valuable tool for monitoring the Earth's environment, among other uses [7][8][6].

Due to being an active sensor, i.e. a sensor that provides its own source of illumination, a SAR can operate during day or night [4][5][7][6]. By selecting the operating frequency correctly, the microwave signal can penetrate clouds, haze, rain and fog and precipitation with very little attenuation, allowing SAR to operate in weather conditions that make the use of visible light/infrared systems unviable [1][4][5][7][9].

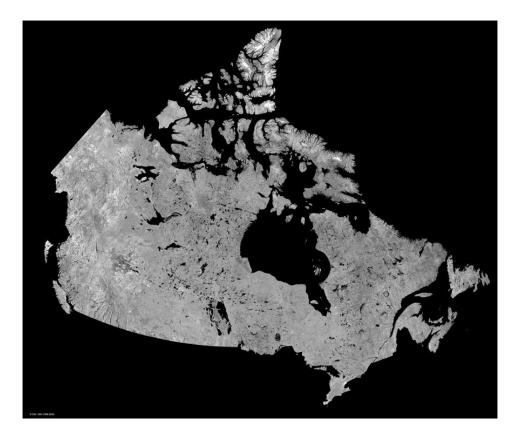

Figure 1-RADARSAT-1 100-metre resolution mosaics of the Canadian provinces over a brief seven-day period in January 1999 (https://www.nrcan.gc.ca/earth-sciences/geomatics/satellite-imagery-and-air-photos/sensors-and-methods/synthetic-aperture-radar/10968).

SAR has been successfully used over a wide range of applications, including surveillance [3], forest, sea, snow and ice monitoring, mining, oil pollution monitoring, oceanography and classification of terrain [4] [7] [10]. Figure 1 shows an example of these applications.

#### 2.1.1 Functioning Principles

The SAR gets its name from the signal processing method it uses, emulating an antenna with big aperture using a moving antenna of smaller aperture[2] [7]. This represents the main difference to its predecessor, the Side-Looking Aperture Radar (SLAR), that had poor azimuth resolution and could only solve the problem by using shorter wavelength signals (that have high attenuation in the atmosphere) or using an impractically long antenna [7].

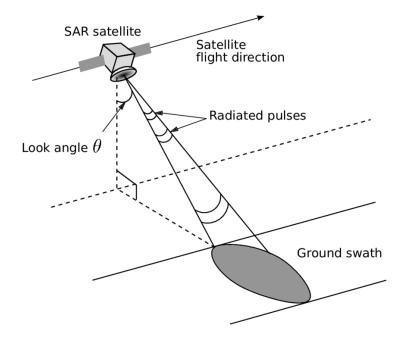

In a SAR system an antenna is usually mounted on an airborne or spaceborne moving platform [2][5]. The platform moves in a straight line with the antenna pointing in a direction perpendicular to the azimuth, while illuminating the desired surface at an angle, the Slant Range (with 0° being the direction straight down from the platform) [9][10].

Figure 2 - SAR's functioning principle [10]

The SAR works by periodically emitting pulses with a well-defined spectrum and then collecting the echoes reflected back to the antenna at regular time intervals, resulting in samples containing information regarding amplitude and phase [2][3][4][8][11][12]. Allying the samples with the precise time at which they were recorded creates a data set that can be passed to an imaging forming algorithm to obtain the final image [12].

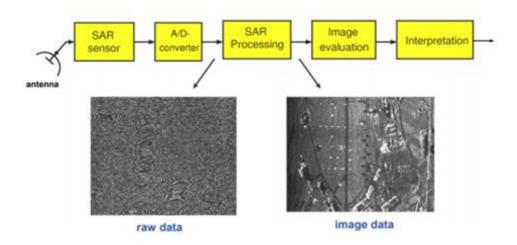

### 2.1.2 Image Formation Algorithms

To create SAR images an image formation algorithm is necessary [1][3]. The algorithm reads the collected raw data and, through several calculations defines an output image, as schematically presented in Figure 3 [5].

Figure 3 - SAR data flow [9]

Image formation algorithms can be divided in two groups: frequency-domain algorithms and time-domain backprojection algorithms [13][5]. Due to their computational efficiency, frequency-domain algorithms are the most widely used [5][12]. Despite this advantage, assumptions regarding squint, range curve mitigation, the planarity of both the surface and the wavefront and the idealized trajectory of the radar platform, among others, reduce the computation costs but degrade the quality of the image formed [2][5][13]]. Compensation techniques can be applied for deviations from these assumptions, but image quality degrades as the deviation increases [2].

The Backprojection Algorithm is a time-domain algorithm [1] capable of generating images with superior quality than those generated with frequency-domain algorithms, being sometimes referred to as the gold standard in terms of quality for SAR image forming [3][6]. It makes nearly no assumptions and can work in a range of modes and geometries [3][5][8], with its biggest drawback being the high computational cost [1][3]. This algorithm will be described in greater detail in the next section.

#### 2.1.2.1 Backprojection Algorithm

This work uses the Global Backprojection Algorithm[3] as an example to show the generic functioning of these algorithms. The following parameters are needed as inputs [2][5][6]:

- Carrier Frequency;

- Range from platform to centre of the swath;

- Range Bin Resolution;

- Image pixel spacing;

- Number of pulses;

- Number of samples per pulse;

- Output image dimensions;

- Platform Locations (Aperture Points);

- Samples from the radar.

To calculate the final value for each pixel, the Backprojection Algorithm executes the following steps for every pair (pixel<->pulse) in the order they are presented [1][3][6]:

- 1. Calculate the distance between the SAR and the pixel.

- 2. Convert the previously calculated distance into a position (range bin) in the sample data set.

- Compute sample value by linear interpolation between the sample of the position obtained before and the sample in the next position. The interpolation can be described by Eq.1:

$$g_{x,y}(r_k) = g(n) + \frac{g(n+1) - g(n)}{r(n+1) - r(n)} * (r_k - r(n))$$

(1)

g(n) – Radar sample in range bin

g(n + 1) - Radar sample in adjacent range bin after

r(n) – Corresponding range to bin

r(n + 1) - Corresponding range to adjacent bin after

4. Compute the values for the matched filter described by the Eq.2, with *dr* calculated according to Eq.3:

$$e^{i.\omega.2.|\vec{r_k}|} = \cos(2.\omega.dr) + isen(2.\omega.dr)$$

(2)

$$dr = \sqrt{(x - x_k)^2 + (y - y_k)^2 + (z - z_k)^2} - r_c$$

(3)

x, y, z – Coordinates of the pixel.

$x_k$ ,  $y_k$ ,  $z_k$  – Coordinates of the radar.

- 5. Scale the sampled values by the matched filter to obtain the pulse's contribution.

- 6. Accumulate the contribution for the pixel. End cycle.

The mathematical formulation for this algorithm is described in Eq.4:

$$f(x,y) = \sum_{k} g_{x,y}(r_k,\theta_k) \cdot e^{i.\omega \cdot 2 \cdot |\overline{r_k}|}$$

(4)

f(x, y) – Output of Algorithm, final value of pixel (x, y)

$\theta_k$  - Aperture point

$$r_k$$

– Range from pixel (x,y) to aperture point  $\theta_k$

$\omega$  – Angular velocity of radar waveform

$g_{x,y}(r_k, \theta_k)$  – Reflection received by radar at  $r_k$  at  $\theta_k$

The C language implementation of the Backprojection Algorithm present in the PERFECT suite [14] differs from the algorithm above in the use of the range from the platform to the centre of the swath [15]. In this implementation it is replaced by R0, representing the minimum distance for which the radar collected samples [15]. Distances inferior to R0 do not have a corresponding sample in the data set.

The pseudocode for this implementation is presented in figure 4:

| Algorithm 1 Backprojection pseudocode.                                                                   |

|----------------------------------------------------------------------------------------------------------|

| 1: for all pixels $k$ do                                                                                 |

| 2: $\mathbf{y}_k = 0$                                                                                    |

| 3: for all pulses $p$ do                                                                                 |

| 4: $R =   \mathbf{a}_k - \mathbf{v}_p  $ /* Distance from platform to voxel */                           |

| 5: $\operatorname{bin} = \lfloor (R - R_0) / \Delta R \rfloor$ /* Range bin (integer) */                 |

| 6: <b>if</b> $bin \in [0, N_{BP} - 2]$ <b>then</b>                                                       |

| 7: $w = (R - R_0)/\Delta R - \operatorname{bin}$                                                         |

| /* Data sampled using linear interpolation $*/$                                                          |

| 8: $s = (1 - w) \cdot \mathbf{x}(p, \operatorname{bin}) + w \cdot \mathbf{x}(p, \operatorname{bin} + 1)$ |

| 9: $\mathbf{y}_k = \mathbf{y}_k + s \cdot e^{j \cdot k_u \cdot R}$                                       |

| 10: end if                                                                                               |

| 11: end for                                                                                              |

| 12: end for                                                                                              |

#### Figure 4 - Pseudocode of the Backprojection Algorithm [15]

The value *Ku* present in the pseudo-code is defined as  $\frac{2\pi f_c}{c}$ , where *c* is the speed of light in vacuum and  $f_c$  is the carrier frequency.

#### 2.1.2.2 Image Quality Assessment

The Signal-to-Noise-Ratio (SNR) metric was chosen to evaluate the quality of the output image. The SNR provides the relation between the power of the desired signal and the power of the background noise, expressed in dBs and calculated using the Eq.5 [1][15],

$$SNR_{dB} = 10\log_{10}(\frac{\sum_{k=1}^{N}|s_{k}|^{2}}{\sum_{k=1}^{N}|s_{k}-n_{k}|^{2}})$$

(5)

where the  $s_k$  and  $n_k$  terms represent the reference and output image values of the k-th element respectively, and N represents the number of values to be compared. The noise is defined as the difference between the reference and the result obtained. This reference is provided in the PERFECT suite. Eq.5 is computed by the pseudocode in figure 5, where *test* represents the output image of the Backprojection algorithm and *ref* represents the reference image. The *re* and *im* fields represent the real and imaginary parts of the value of each pixel.

Algorithm 2 SNR calculator pseudocode. 1: for all pixels p do  $den \leftarrow den + (ref[p].re - test[p].re)^2$ 2:  $den \leftarrow den + (ref[p].im - test[p].im)^2$ 3:  $num \leftarrow num + (ref[p].re)^2 + (ref[p].im)^2$ 4: 5: end for 6: if den == 0 then 7: return 140.0 8: **else** return  $10.0 \cdot \log_{10} \frac{num}{den}$ 9: 10: end if

Figure 5 - Pseudocode to compute the SNR of an Image [16]

Large positive numbers of SNR represent a high degree of similarity between the two images. Each 20 dB of SNR correspond roughly to a single digit of accuracy between values [15]. The PERFECT suite manual sets 100 dB as the reasonable correctness threshold [15].

### 2.2 Reconfigurable Hardware

Reconfigurable computing refers to the use of a computer architecture that combines the flexibility of software with the high performance of very flexible high-speed computing fabrics hardware [1]. The family of devices that best embodies this philosophy results from the fusion of a SoC with a FPGA device. The FPGA part of the device provides the configurable high-speed computing fabric while the SoC architecture guarantees a tight coupling between components, the existence of a microcontroller or microprocessor, the existence of external memories or connectors for external memories and a range of peripheral ports [17].

The most important difference between these devices and regular microprocessors is the ability to make substantial changes to the Datapath [18]. Modern microprocessors are complex, mainly sequential devices designed to be applicable for solving virtually any mathematical problem and as such are not fully optimized to solve simple calculations [18]. The FPGA, on the other hand, allows the Datapath to be designed with only the necessary elements while offering a parallelization-friendly environment [19]. By fusing the two systems a new one is created with a generic CPU and connectors granting high portability and compatibility, tightly coupled with a programmable fabric allowing the design of high-performance modules that perform specific operations considerably faster than the CPU [20].

The Graphics Processing Unit (GPU) based accelerators are usually preferred over their CPU-based counterparts due to their improved throughput, but the high-power consumption of GPU has brought up concerns regarding cooling in data centres [19][21]. When comparing these to a SoC-FPGA device, a considerable difference lies on power consumption [21][20]. This topic has been a case study over the last decade, with some studies reporting an increase in energy efficiency of 75 times in the most favourable situations and an increase of 9.5 times when working in the most favourable to the GPU architecture [18][21].

Another type of devices that can offer this granularity in the design of the Datapath are the ASICs. What the ASICs offer in specificity, they lose in flexibility. These devices are built to perform only very specific operations offering no means of re-configuration [20]. FPGA devices have clear advantages in design revisions and development costs by making available a high performance system from the get-go with well-known available resources, unlike the ASICs that must make a lot more decisions regarding the chip composition and production [22].

There are several accelerators for the Backprojection algorithm. Some target High performance systems [23], while others target embedded systems using variants of the algorithm like the works in [24] and [25]. Previous work on implementations of the Backprojection algorithm using a SoC device can be found in [1] and [6]. The work in [6] presents an accelerator, developed with the High-Level-Synthesis tool, to compute the more time consuming operations identified through profiling, using floating-point.

### 2.2.1 Zybo Z7-10

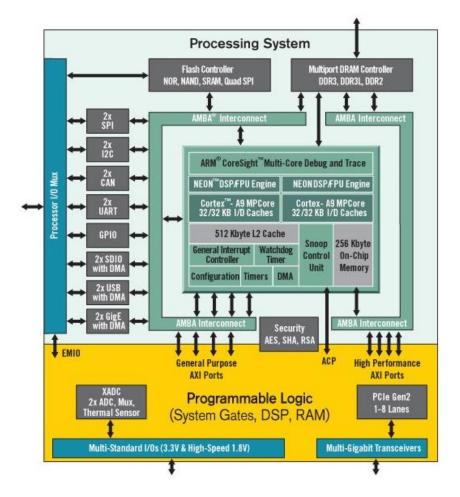

This work was developed to be implemented in a Zybo Z7-10 board [26] containing a Zynq 7000 device from Xilinx.inc (Califórnia, USA), an external DDR3 memory with capacity for 1GB and I/O peripherals. The Zynq 7000 is composed of a Processing System (PS) and PL block. The main components in the PS are the Dual-core ARM Cortex-A9, containing cores identified as CPU0 and CPU1, the memory controller and the Advanced Microcontroller Bus Architecture (AMBA) Interconnect bus. The ARM processor has two levels of cache, the L1 cache being composed of a 32KB memory for data and another 32KB memory for instructions and the L2 cache having 512KB and being shared between the cores. Additionally, it features a 256KB On-Chip-Memory split into two continuous address spaces, the Random Access Memory (RAM) 0 and 1, with 192KB and 64KB respectively. The ARM processor has a clock frequency of 667MHz and a dedicated Phase-Locked Loop (PLL) capable of generating up to four reference clocks, each with settable frequencies, that can be used to clock custom logic implemented in the PL.

The AMBA Interconnect bus links all the peripherals as slaves to the processor and contains readable/writable control registers (reg) that are addressable in the processors' memory space. The main connections used in this project are the High-Performance (HP) ports and the General Purpose (GP) ports. Although it is not a physical component is important to mention the Advanced eXtensible Interface (AXI) protocol, that is the Intellectual Property (IP) interconnect standard chosen by Xilinx. It provides not only improved performance and flexibility to build custom IP cores, but also compatibility with the Xilinx IP-catalog and a worldwide community of ARM Partners.

The PL is a Xilinx 7-series FPGA. The resources available are shown in table 1.

| Table 1 - Zybo Z7-10 PL main reso | ources. [26] |

|-----------------------------------|--------------|

|-----------------------------------|--------------|

| LUT elements | Flipflops | DSP | BRAM       | Slice |

|--------------|-----------|-----|------------|-------|

| 17 600       | 35 200    | 80  | 60 (270KB) | 4400  |

The schematic of the APSoC (All Programmable SoC) is shown in figure 6.

Figure 6 - Overview of the Zynq APSoc Architecture [26]

The board was selected due to its embedded architecture, reconfigurable capabilities, and low power consumption.

The implementation, that is detailed in chapter 4, uses primarily:

- the Double Data Rate (DDR) memory to store the input files and the final output;

- HP ports with Direct Memory Access (DMA) capabilities and high bandwidth to link the DDR memory to the Hardware Accelerator;

- the GP ports used by the CPU for controlling the AXI-DMA modules that manage the channels between the Hardware Accelerator and the HP ports;

- the CPU for controlling the DDR memory accesses through the control of the AXI-DMA modules;

- the PL fabric to implement the Hardware Accelerator. The PL uses only one clock, from the four references made available by the PS.

## 2.3 Numeric Formats

The design of embedded systems usually starts at the algorithmic level where an execution model is created from the general concept of an algorithm. The development at this stage in the design process is made invariably using the Floating-Point numeric format since it provides the best precision of all formats and is natively supported in most Personal Computer (PC) systems [27].

After the initial phase, design constraints change drastically due to the target system changing from a common PC system to an embedded system. In the new target, the use of a fixed-point format is known to allow drastic savings in the traditional cost metrics: silicon area, power consumption and latency/throughput [27][28].

In this section both types of numeric formats are presented, followed by a comparison based on the differences observed in the multiplication operation and the impact they have in an FPGA implementation.

### 2.3.1 Floating-Point

The floating-point format stores in a variable three numbers to represent a value. These numbers are unsigned integers and have a specific position in the word, i.e. each value is interpreted by the position it occupies. The size of these numbers (in bits) differs between floating point formats. The floating-point representation is composed by the following fields, in the order presented below from Most Significant Bit (MSB) to the Least Significant Bit (LSB):

- the sign field (0 = positive, 1= negative);

- the exponent field;

- the significant field.

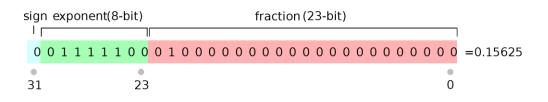

To categorize a floating-point format, it is also necessary to know the base and the bias value used, with 2 and 127 being the values adopted in the Institute of Electrical and Electronics Engineers-754 (IEEE) for the 32-bit single precision floating-point numbers [29]. Figure 7 provides a graphical representation of the standard 32-bit single precision floating-point format.

Figure 7 - Word structure of a number in Floating-Point format (https://courses.physics.illinois.edu/cs357/sp2020/notes/ref-4-fp.html)

A value stored in a floating-point format can be converted to a real value by performing the operations in Eq. 6, where  $\sigma$  represents the signal,  $\sigma = \pm 1$ .

$$X = \sigma * 2^{(exponent-bias)} * significant$$

(6)

The bias was introduced to allow the representation of very small numbers, allowing the use of negative powers of two without the need to use a sign bit in the exponent field. Although the floating-point format allows the representation of real numbers, a single floating-point format cannot represent all real numbers in any given interval.

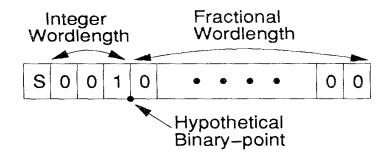

### 2.3.2 Fixed-Point

The Fixed-Point formats store a value in a variable in 2's complement [30]. The name fixed-point stems from the fact that in a word there is a fixed number of bits to represent the integer part of the value and a fixed number of bits to represent the decimal part of the value, creating an imaginary binary-point in the number.

Figure 8 - Word structure of a number in Fixed-Point format [30]

To interpret the true value represented by a fixed-point variable it is necessary to know the scale factor used, as its value will determine the location of the binary-point. The scale factors are usually positive powers of two, enabling the use of bit shift operations as a replacement for multiplications whenever the scale of a variable needs to be adjusted. To store a value in a fixedpoint format the following operation is performed:

$$FixP = Value * Scale Factor;$$

(7)

To interpret the actual value stored in a variable the complementary operation is performed:

$$Value = \frac{FixP}{Scale}Factor;$$

(8)

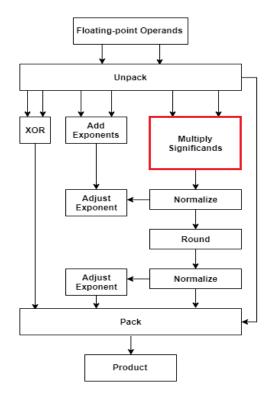

#### 2.3.3 Numeric Format Comparison

This section presents a brief comparison between the two previously described numeric formats. The comparison focuses on the differences between implementations of basic arithmetic operations and the impact they have on hardware implementations. This analysis does not regard precision since the target system chosen for this work supports fixed-point operations with a maximum input size big enough to achieve higher precisions than required.

The multiplication operation will be used to exemplify the differences with greater impact in the choice between the two formats. Figure 9 shows the architecture of a floating-point multiplication which includes chain of operations, starting with the multiplication of the significands and composed of four stages, that is required to maintain the precision of the result. This becomes a critical path in the Datapath.

Figure 9 - Floating-Point Multiplication Architecture [29]

While the entirety of figure 9 represents the blocks needed to perform a floating-point multiplication, only the highlighted block is necessary for a fixed-point multiplication. The designer must, however, be mindful of the increase of the scale of the output. It can be concluded that a fixed-point implementation incurs in less complex operations than a floating-point operation, allowing for a greater performance and lower resource allocation. The scale adjustments in the

fixed point operations do not pose a constraint because they can be performed by bitwise operations that in hardware can be implemented by splitting a bus or concatenating 2 buses (The architecture "performs" the operations, not the logic cells).

### 2.4 Approximate Computing Techniques

In this section the methods studied for alternative implementations of mathematical operations are presented in detail. As stated in the introduction of this chapter, there are operations in the algorithm that do not have a standard implementation in a fixed-point format. To overcome this limitation, new implementations were made using methods capable of producing approximate results. These methods can be implemented in hardware and are resource-effective, albeit producing less precise computations than the standard library implementation of these operations in C language.

Due to the context of this work, the methods are studied with two purposes: the first is to choose a method for software implementation; the second is to choose a method for hardware implementation. The software implementation is not essential but can be useful for the initial studies of the algorithm. The performance of the methods varies greatly with the platform were it is being executed and because software and hardware implementations are fundamentally different in nature, methods chosen for each case can be different.

This section is split into two parts, one regarding the square root operation and the other regarding the trigonometric functions.

#### 2.4.1 Square Root

This section presents the methods studied for the fixed-point implementation of the square root operation.

#### 2.4.1.1. Newton-Raphson

Named after Isaac Newton and Joseph Raphson, the Newton Raphson method is an iterative root-finding algorithm, meaning it is used to solve algebraic equations of the form [31]:

$$F(x) = 0 \tag{9}$$

The method needs an initial guess to produce the first iteration while the successive iterations are calculated using the eq.10:

$$X_{n+1} = X_n - \frac{F(X_n)}{F'(X_n)}$$

(10)

The definition of  $F(X_n)$  chosen to approximate the square root function of *Y* using this method is presented in the following equations:

$$F(X) = Y - X^2 \tag{11}$$

This definition yields the following derivative in *X*:

$$F'(X) = -2X \tag{12}$$

Using eq.11 and 12, the adapted formula for the method results in:

$$X_{n+1} = X_n + \frac{Y - X_n^2}{2X_n}$$

(13)

The resulting formula can now be optimized in terms of the operation composition, to reduce the costs of a hardware implementation (Some optimizations are fixed point exclusive). By application of the distributive property on the division and subtraction, the of eq.13 can be changed to eq.14:

$$X_{n+1} = X_n + \left(\frac{Y}{X_n} - X_n\right)/2$$

(14)

The new form produces the same output but has the advantage of performing no multiplications (1 less than the original formula) and of replacing the division by 2 with an arithmetic shift left (Due to the use of the fixed point format).

The stop criteria used for the method is defined in eq.15:

$$\frac{-F(X_n)}{F'(X_n)} > 0 \tag{15}$$

#### 2.4.1.2 Binary restoring square root extraction

The binary restoring square root extraction algorithm finds the square root x of a nonnegative integer number, R, satisfying the following constraints [32]:

$$x^{2} \le R AND (x+1)^{2} > R$$

(16)

This method takes 2 bits of the Radicand to produce 1 bit of the result in each iteration, resulting in a complexity of O(n/2), with n being the size in bits of the radicand [33]. Below is presented a C language implementation of this algorithm [32]:

```

#define FRACBITS 30;

#define ITERS (15 + (FRACBITS >> 1));

typedef long TFract; /* 2 integer bits, 30 fractional bits */

TFract

FFracSqrt(TFract x)

{

register unsigned long root, remHi, remLo, testDiv, count;

root = 0; /* Clear root */

remHi = 0; /* Clear high part of partial remainder */

remLo = x; /* Get argument into low part of partial remainder */

count = 30; /* Load loop counter */

do {

remHi = (remHi<<2) | (remLo>>30); remLo <<= 2; /* get 2 bits of</pre>

arg */

root <<= 1; /* Get ready for the next bit in the root */

testDiv = (root << 1) + 1; /* Test radical */</pre>

if (remHi >= testDiv) {

remHi -= testDiv;

root++;

}

} while (count-- != 0);

return(root);

}

```

From the code presented it can be deduced that this algorithm does not use any multiplication or division and has a simple loop composed only of shift-add operations that execute quickly in software and especially in digital hardware, making it a competitive solution for the computation of the square root.

## 2.4.2 Trigonometric Functions

This section presents the algorithms studied for the fixed-point implementation of the trigonometric functions.

The Coordinate Rotation Digital Computer algorithm (CORDIC) is a hardware-efficient iterative method especially suitable for solving trigonometric functions and hyperbolic functions [34]. CORDIC's main concept is the usage of a series of optimized rotations to achieve the input rotation. The great advantage of this algorithm is that it belongs to the shift-add family, meaning it does not need multipliers to be implemented. The CORDIC's main working principles are explained in this section.

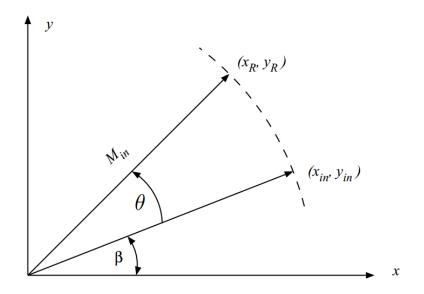

Figure 10 - Rotation of a vector by an arbitrary angle

(https://www.allaboutcircuits.com/technical-articles/an-introduction-to-the-cordic-algorithm/)

A rotation around the origin in the 2-D plane (shown in figure 10) can be defined by eq.17 and 18:

$$X_R = X_{in} * \cos(\theta) - Y_{in} * \sin(\theta)$$

(17)

$$Y_R = X_{in} * \sin(\theta) + Y_{in} * \cos(\theta)$$

(18)

Re-writing eq.17 and 18 into the matrixial form yields eq.19:

$$\begin{bmatrix} X_R \\ Y_R \end{bmatrix} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} X_{in} \\ Y_{in} \end{bmatrix}$$

(19)

Eq.19 can be simplified into eq.20.

$$\begin{bmatrix} X_R \\ Y_R \end{bmatrix} = \cos(\theta) \begin{bmatrix} 1 & -\tan(\theta) \\ \tan(\theta) & 1 \end{bmatrix} \begin{bmatrix} X_{in} \\ Y_{in} \end{bmatrix}$$

(20)

There are two fundamental ideas behind the CORDIC's implementations. The first is that rotating a vector by an arbitrary angle  $\theta$  is the same as rotating the same vector by several smaller angles; the second is that it is possible to compute the rotations by substituting the multiplications by  $\tan(\theta)$  with simple bitwise shift operations, by choosing these smaller angles in a way that eq.21 is satisfied,

$$\tan(\theta_i) = 2^{-X} \tag{21}$$

where X is a positive integer. A CORDIC interpretation of an angle composed by the sum of 3 smaller angles is explained in eq.22:

$$\begin{bmatrix} X_R \\ Y_R \end{bmatrix} = \cos(\theta_0)\cos(\theta_1)\cos(\theta_2) \begin{bmatrix} 1 & -2^0 \\ 2^0 & 1 \end{bmatrix} \begin{bmatrix} 1 & -2^{-1} \\ 2^{-1} & 1 \end{bmatrix} \begin{bmatrix} 1 & -2^{-2} \\ 2^{-2} & 1 \end{bmatrix} \begin{bmatrix} X_{in} \\ Y_{in} \end{bmatrix}$$

(22)

The only multiplication left to perform can be ignored until the end of the process because the product defined by eq.23 converges to the value in eq.24:

$$K(n) = \prod_{k=0}^{n-1} \cos\left(\theta_k\right) \tag{23}$$

$$\lim_{n \to \infty} K(n) = 0.60725293500$$

(24)

Leaving the iterations of the algorithm to be defined by eq.25:

$$\begin{bmatrix} X[i+1]\\ Y[i+1] \end{bmatrix} = \begin{bmatrix} 1 & -\sigma_i 2^{-i}\\ \sigma_i 2^{-i} & 1 \end{bmatrix} \begin{bmatrix} X[i]\\ Y[i] \end{bmatrix}$$

(25)

Where  $\sigma_i$  represents the direction of each rotation,  $\sigma_i = \pm 1$ . As stated before, it is still necessary to perform the final multiplication by the factor *K*.

## 2.4.2.2 Taylor Series

The Taylor Series is a method of approximating functions through an infinite sum of terms that are expressed in terms of the function's derivatives at a single point. The Taylor Series of a function f(t) around point t=tr can be defined by the equations 26 and 27 [35]:

$$f(t) = \sum_{i=0}^{\infty} \frac{f^{(k)}(t_r)}{i!} * (t - t_r)$$

(26)

$$f^{(k)}(t) = \left(\frac{\partial^{(k)} f(t)}{\partial t^{(k)}}\right)$$

(27)

The Taylor series applied to the trigonometric functions cosine and sine takes the forms in eq. 28 and 29 respectively:

$$\cos(x) = \sum_{n=0}^{\infty} (-1)^n * \frac{x^{2n}}{(2n)!}$$

(28)

$$\sin(x) = \sum_{n=0}^{\infty} (-1)^n * \frac{x^{2n+1}}{(2n+1)!}$$

(29)

Although this method can produce precise results, the need for multiplications makes it a less ideal candidate for implementation in FPGA fabric when CORDIC can produce results with the same precision [1], without the use of multiplications.

# **3 Optimization Methodology**

The design of the optimized Hw/Sw system begins with the study of the algorithm as along with the environment of the new implementation to understand what new tools and functionalities are available and how and where they can be used.

This chapter presents the optimization methodology, composed by the studies of the C language implementation of the Backprojection Algorithm, the studies of the target environment and the design decisions they support.

The chapter begins with the profiling study followed by the Hw/Sw partition. The wordlength study is then presented, followed by the hardware resource utilization study guided by the previous study's conclusions. This chapter concludes with the algorithm's re-scheduling that aims to further improve the optimized system's architecture.

# 3.1 Algorithm Profiling

The first step in the optimization of the Backprojection algorithm is to identify the most time-consuming instructions of the algorithm, as these will be the ones with the higher potential for acceleration. To this end a profiling study was developed to quantify the time resources required by each operation.

This section presents the profiling of the C language implementation of the algorithm provided in the PERFECT suite [15]. The first step of this study was performed in a PC to obtain an initial estimate using the already fully functional available materials. Table 2 details the main specifications of the PC used along with relevant configuration options.

| Table 2 - Computer Specifications and Configuration |                |    |         |  |

|-----------------------------------------------------|----------------|----|---------|--|

| CPU Operating system Multi-Threading Compilation    |                |    |         |  |

| Intel 17-7700K                                      | Ubuntu 20.04.1 | No | default |  |

This provided a basis to compare the forthcoming results from the algorithm execution in the target system's CPU. Table 3 details the CPU present in the target device, along with the relevant configuration options.

| CPU           | Operating system | Multi-Threading | Compilation flags |

|---------------|------------------|-----------------|-------------------|

| ARM Cortex-A9 | Bare metal       | No              | -O3               |

The profiling study of the implementation using the PC was made using the gprof tool available in the Ubuntu 20.04.1 LTS release<sup>1</sup>. The profiling was made using an image set that has the sample data of 512 pulses and produces an output image of 512 x 512 pixels.

The next step of the process is the profiling of the algorithm's execution in the target system. The C code used in this stage is the same as the one used in the PC, except for adaptations made regarding the reading operations of the input files. Profiling in the target system was performed using the xil\_time.h library functions. The results obtained are detailed in table 4.

Table 4 - Profiling results of the C language implementation of the Backprojection Algorithm

| Algorithm Operation    | Desktop Computer (-O3) | Zybo Z7-10 (-O3)          |  |

|------------------------|------------------------|---------------------------|--|

| Pythagorean Theorem    | 0.00425 us             | 0.12 us                   |  |

| Pow ^2                 | 0.00365 us             | 0.04 us                   |  |

| Square Root            | 0.00059 us             | 0.06 us                   |  |

| Cos & Sin              | 0.00231 us             | 3.40 us                   |  |

| Complex Multiplication | 0.00618 us             | 0.06 us                   |  |

| Total                  | 6.97 s                 | 480,729,250.04 us (481 s) |  |

The differences observed between the profiling results obtained in the PC and in the target system can be explained by the different architectures used to manufacture the CPU of the two systems. From this point onward the results obtained regarding the target system will be used as reference for future comparisons.

<sup>&</sup>lt;sup>1</sup> <u>https://ubuntu.com/download/desktop</u>

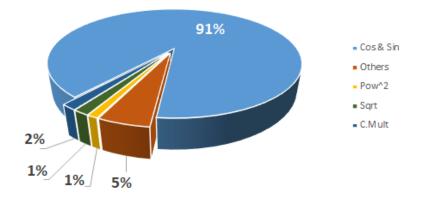

Profiling -O3 (Zybo Z7-10)

Figure 11 - Graphic representation of the profiling results of the zybo board from table 4

From analysis of the results, it can be concluded that the Cosine and Sine operations should be the focus of the optimization process, as these are responsible for 91% of the processing time. These findings correspond to the conclusions of previous works [1][2][6].

A first proposition for the optimized system architecture that can emerge from the conclusion explained above is to have the Cosine and Sine operations implemented in the PL of the SoC while the rest of the algorithm still executes in the CPU. However, this architecture's execution time would still be far from the initial goal defined in the introduction of this work. This is due primarily to the fact that a cycle of the algorithm (instructions comprised in the calculations of a single pulse's contribution to a single pixel) has too many instructions to allow a serial execution in the CPU to be efficient, even if we consider the Cos and Sin execution time is 0 and that the CPU's clock is 4 to 5 times faster than the fastest clock that a circuit implemented in the PL can achieve (CPU frequency = 667MHz; PL frequency = 150MHz). In light of these considerations, it becomes easy to understand that the goal of a total execution time of one second requires the system's architecture to take maximum advantage possible from the pipelining and parallelization opportunities made available by the PL system.

# 3.2 Hardware/Software Partition

The target's system family devices were presented in this work as the fusion of two independent systems. This section is focused on the partition of the system's execution between the PS and PL systems.

To achieve the initial goal of total execution time below the one second mark, the system needs to take advantage of the reconfigurable hardware's characteristics in terms of pipelining and parallelization. In this case it means that most, if not all, of the algorithm should be executed in the PL because of the limitations of the PS system when handling the serial execution of a program with many cycles (134,217,728 cycles in this case). This idea is further supported by the work in [6], that registered a speedup of 7.7x, achieved by implementing the more time consuming operations in reconfigurable hardware.

A system partition is proposed, based on the observations made in the previous paragraph, with the following characteristics:

| PS                              | PL                                           |

|---------------------------------|----------------------------------------------|

| Initialization of AXI-DMA       | Calculus of the Distance between the         |

| modules;                        | Satellite and the pixels;                    |

| • Control of the read and write | Calculus of the matched filter values        |

| operations to the DDR memory.   | relative to the Distances calculated before; |

|                                 | • Sample selection using the calculated      |

|                                 | Distances;                                   |

|                                 | Sample linear interpolation;                 |

|                                 | Complex multiplication between the           |

|                                 | samples and the matched filter;              |

|                                 | • Accumulation of the products of the        |

|                                 | complex multiplication.                      |

#### Table 5 - Hardware / Software partition

This proposal is made assuming the following:

- Due to the size of the input data files, they are initially stored in the DDR memory;

- The hardware accelerator will access the DDR memory in DMA mode, through the HP ports (using a well-known xilinx IP core, the AXI-DMA);

- The PL and PS will also communicate using the GP ports.

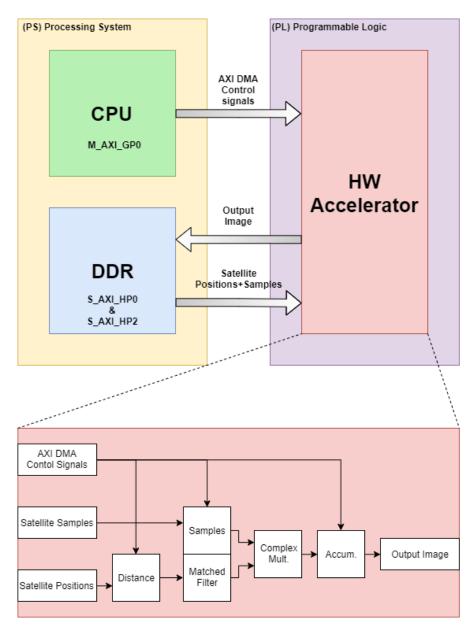

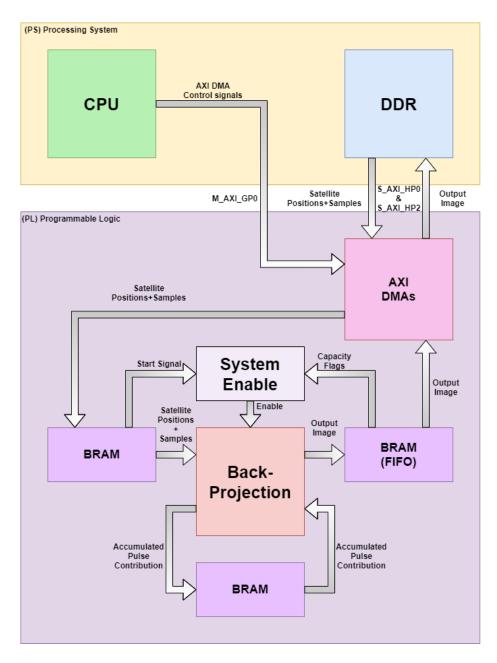

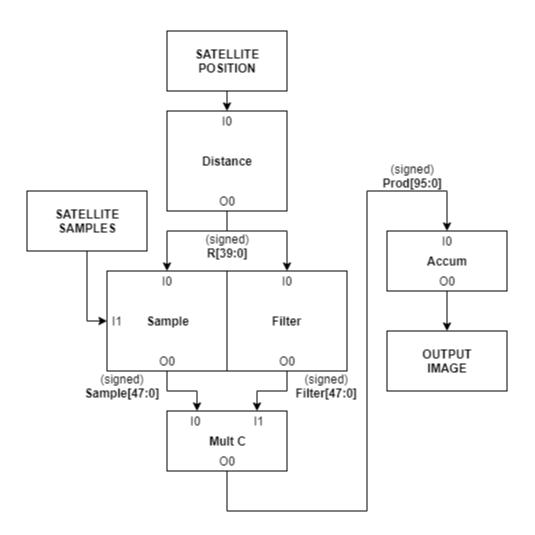

Figure 12 illustrates the proposed partition.

Figure 12 - Overview of the proposed system's partition

With this architecture the optimization can go much further than the first proposal made in the previous section in terms of execution time, because now we can pipeline all the algorithm's operations, achieving a higher throughput. The working frequency was chosen to allow the target system to achieve the desired execution time of 1 second. Solving eq. 30 and 31:

$$Execution Time = (N^{\circ} Pipeline stages + N^{\circ} Cycles) / Frequency$$

(30)

Execution Time =

$$(0^{\prime} + 134\ 217\ 728)/x = 1s$$

(31)

We obtain a minimum frequency of 135 MHz. However, the closest possible clock frequency allowed in the target device is 140 MHz. Although the number of pipeline stages is

unknown at this point, we can consider it almost zero, because the number will always be small when compared with the number of iterations in the algorithm.

Initially, for a clock frequency of 140MHz the circuit did not achieve the timing requirements. In the combinatorial logic part of the circuit, these issues were solved though the placement of pipeline stages, leaving the communications and memory accesses as the potential limiting factors, which are addressed in sections 3.4 and 3.5.

This is only a proposal, as it is still necessary to evaluate its feasibility in terms of resources used and the performance of these resources (not all resources all fully customizable).

# 3.3 Word-Length Optimization

To design an optimized circuit, it is fundamental to choose the right size for its signals as this decision has a great impact over the resources allocated and in achieving the timing requirements of the circuit.

This section presents the word-length study made on the Backprojection Algorithm for implementation of the algorithm using the fixed-point numeric format. This study has two parts: the first aims to provide the length, in bits, that the integer part of every signal needs in order to accommodate its biggest possible absolute value avoiding overflow; the second part aims to provide the length that the decimal part of every signal needs in order to attain precision that will guarantee the overall quality performance of the system of 100dB of SNR [28].

The first part begins by executing the original program while collecting information about the interval of values each variable can take. With these results a final number of bits can be defined for the integer part of each signal, that will be able to hold every value needed and avoid overflow of operations. These results do not consider the bit used for the signal because this is inferred case by case.

The requirements for the word lengths found by this study are presented in the tables in appendix A.

To perform the second part of this study it was necessary to develop a new software implementation of the Backprojection algorithm using fixed point. Due to the complexity of the relation between the attained SNR and the length of the decimal part of the variables, this part of the study was made by trial and error.

The new implementation was developed taking into account that after the loss of precision occurring in the conversion of the input values to the fixed-point format, no other loss of precision is present (meaning all significant bits of the output values of mathematical operations are carried forward). Considering that every variable's fixed-point format can be deducted from the variable's relation to the input variables, the latter were split in two groups:

- Variables belonging to the calculation of the distance between the Satellite and a pixel. (satellite positions, pixel positions, Pythagorean theorem variables, sample selection variables);

- Variables belonging to the Filter and Samples (samples, matched filter, interpolation coefficients, complex multiplication variables, accumulation variables).

Some operations don't have an implementation in the standard libraries for operators bigger than 64 bits and some operations like the square root and the Cosine and Sine don't have an implementation in fixed point. As such, new implementations were made for those cases, implementing the square root and trigonometric functions using the chosen methods among those detailed in section 2.4.2. Although the mathematical operations do not cause loss of precision, the method used for the trigonometric functions does not guarantee precision to the LSB. This new implementation of the algorithm was executed several times using different size combinations for the variables. The integer part of the variables was fixed with the help of the results of the first part of this study while the decimal part was chosen to occupy the remaining bits. The different sizes varied in a 1-byte interval starting at 24 bits and going up to 64. Table 6 shows the SNR (in dB) obtained for each combination. The size of the variables from the Data group vary between lines and the size of the variables from the Distance group vary between columns.

| Data/Distance | 64      | 56      | 48      | 40             | 32     | 24    |

|---------------|---------|---------|---------|----------------|--------|-------|

| 64            | 182.876 | 183.976 | 151.595 | 103.129        | 54.967 | 9.252 |

| 56            | 182.876 | 183.976 | 151.595 | 103.129        | 54.967 | 9.252 |

| 48            | 182.876 | 183.976 | 151.595 | 103.129        | 54.967 | 9.252 |

| 40            | 182.819 | 183.904 | 151.595 | 103.129        | 54.967 | 9.252 |

| 32            | 153.005 | 153.007 | 149.326 | 103.129        | 54.967 | 9.252 |

| -             |         |         |         |                |        |       |

| 24            | 103.609 | 103.609 | 103.610 | <u>100.469</u> | 54.965 | 9.252 |

| Table 6 - SNR | (dB | ) obtained i | for | each | word-lenath | combination | studied |

|---------------|-----|--------------|-----|------|-------------|-------------|---------|

|               |     |              |     |      |             |             |         |

From the results in table 6, it can be concluded that to achieve the quality minimum of 100dB of SNR while minimizing resource utilization, the best size combination is:

- Distance 40 bits.

- Data/Filter 24 bits.

This combination achieves an SNR of 100.469dB and results in the following fixed-point formats:

- Distance [39:0] 15Q25 (signed).

- Data/Filter [23:0] 2Q22 (signed).

To further corroborate the conclusion drawn here, this part of the study was extended by conducting an extra experiment with the chosen sizes and the chosen sizes minus 1 bit. The results yielded by this experiment in terms of SNR (in dB) are presented in table 7.

Table 7 - SNR (dB) obtained for the word-length combinations closest to the threshold

| Data/Distance | 40             | 39     |  |

|---------------|----------------|--------|--|

| 24            | <u>100.469</u> | 96.359 |  |

| 23            | 96.543         | 94.401 |  |

From these results it is concluded that the best possible combination of formats that can be found while using the methodology followed in this work is the previously elected one, highlighted in tables 6 and 7.

It should be noted that in the implementation developed for the second part of this study some operations incurred in precision loss. This loss occurs in the calculation of the argument for the trigonometric operations, where a right shift is executed on the output of a multiplication that converts a value in scaled radians to a value in radians. This operation is performed to reduce the bit width necessary to represent the value of the argument. The CORDIC algorithm performs an iteration for each bit of the input, therefore reducing the input size reduces the number of iterations needed as well.

Figure 13 presents the code that performs the detailed operations, with the operation responsible for the precision loss highlighted.

```

//argument_sr - argument in scaled radians;

//Pi2 - value of 2*pi;

//argument - argument in radians;

argument = multiplication(argument_sr, PI2);

argument >>= (64 -DATA_BITS);

cordic_func(argument, &_sin, &_cos, DATA_BITS);

```

Figure 13 - Snippet of code responsible for performing the error inducing operation.

From the results presented in table 6 it can be concluded that, in the ranges considered for the bit width of the signals, the width of the Distance group variables has a greater impact on the output image quality than the width of the Data group variables. This conclusion further supports the choice of a precise method for the implementation of the square root operation: the Binary restoring square root extraction.

The chosen fixed-point formats all use rounding as the quantization mode. The need for an overflow mode was overcome with the selected choices for the word-lengths. The full list of the fixed points formats for each signal in the circuit will be shown in the next section 4.1.2.

# 3.4 Resource Utilization Study

The Zybo Z7-10 board used in this work has limited resources and the use of those resources adds complexity to the circuit and has an associated power consumption. From an optimization perspective, the possibility of freeing unnecessary resources that could otherwise have a very negative impact in the efforts to meet the timing constraints offers room for improvements. The goal of this study is to provide a relation between the size of the operators (inputs and output) and the resources allocated for that IP core to obtain the information needed to identify potentially expensive areas and make estimates on the values of the resources allocated by the future design. Although this work was developed with a specific target system in mind, the results from this type of study can inform the choice of a suited device when working in projects that start with an undefined target system.

The study was developed by making a synthesized design in Vivado 2019.2 of the main IP cores used, with varying operator sizes, varying pipeline stages and with the clock frequency set to 140MHz (estimate frequency needed to achieve final timing goal). The variations in pipeline stages only occur until the design meets the timing requirements. The results are presented in the tables in appendix B.

The number of IP cores needed to implement the circuit that performs the mathematical operations described in the C language implementation of the Backprojection algorithm can be estimated to further assess the total resources of the top-level modules.

Since the use of extra IP cores and their configurations in this project was expected, some were studied to get better estimates. The referred IP cores are the AXI DMA, the AXI Interconnect and the AXI Data FIFO. Table 8 shows the resources used in the implementation of these support IP cores.

| IP core                     | Quantity | Unit Cost    | Total Cost   |

|-----------------------------|----------|--------------|--------------|

| AXI DMA                     | 2        | LUT: 1954    | LUT: 3908    |

|                             |          | Reg: 2570    | Reg: 5140    |

|                             |          | F7 MUX:5     | F7 MUX: 10   |

|                             |          | BRAM 36Kb: 3 | BRAM 36Kb: 6 |

| AXI Interconnect (HP ports) | 2        | LUT: 684     | LUT: 1368    |

|                             |          | Reg: 783     | Reg: 1566    |

| AXI Interconnect (GP port)  | 1        | LUT: 551     | LUT: 551     |

|                             |          | Reg: 694     | Reg: 694     |

| AXI Data FIFO               | 2        | LUT: 61      | LUT: 122     |

|                             |          | Reg: 89      | Reg: 178     |

|                             |          | BRAM 36Kb: 4 | BRAM 36Kb: 8 |

## Table 8 - Resources used by support IP cores\*

\* The configurations of these IP cores are detailed in chapter 4.

With the information needed to make the circuit estimates gathered, two estimations were, one for the circuit made using the formats chosen in the previous section (Estimate A) and other for a hypothetical circuit made based on 64 bit wide input variables (Estimate B). The estimates include only the circuit responsible for performing the mathematical operations of the Backprojection algorithm, excluding control, support and memory related IP cores. The estimates also exclude the square root operation due to the fact that this operation is implemented by a custom module with fixed input size. Tables 9 and 11 compile all the basic arithmetic IP cores that need to be used to compute the algorithm

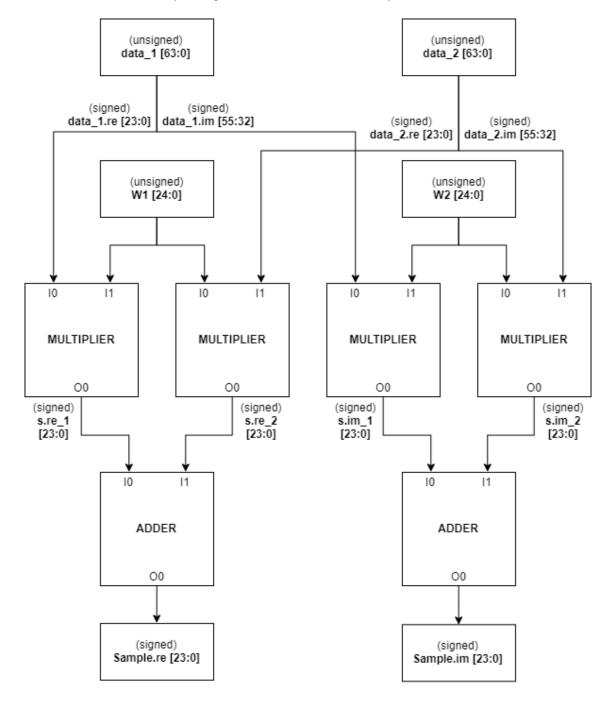

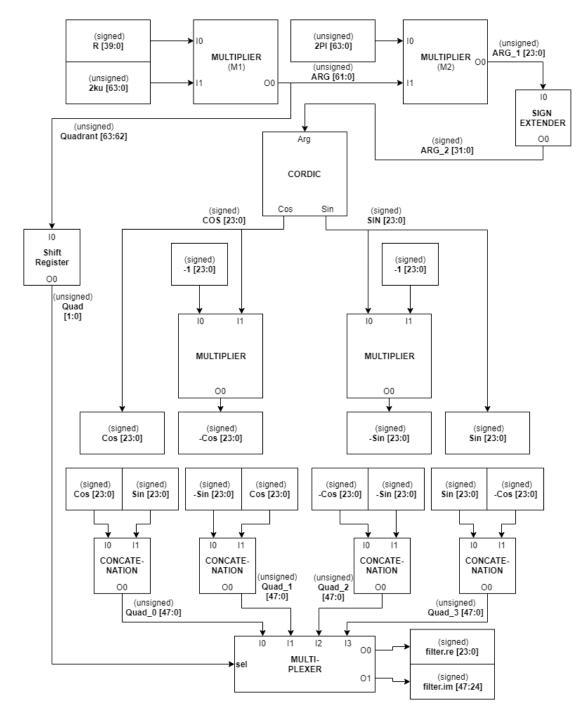

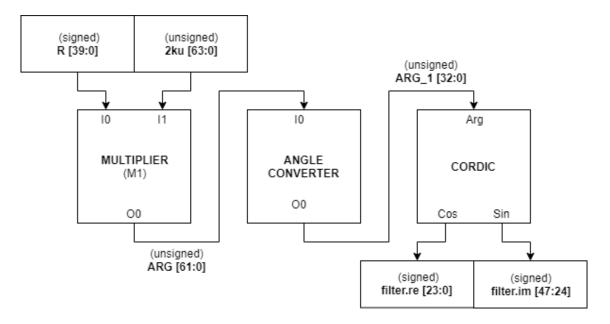

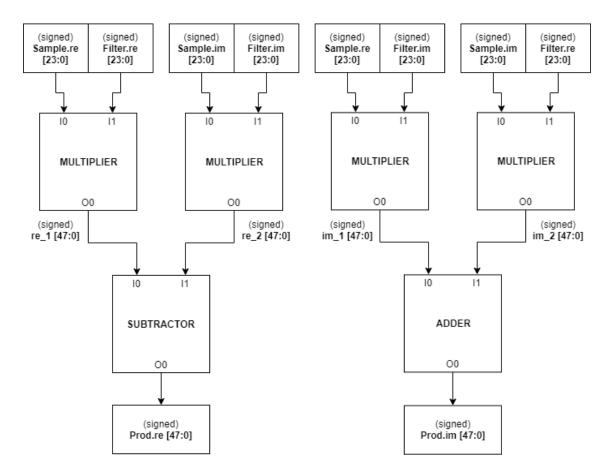

## Estimate A