# **Evolution of the Communications Processor Board** for the ISTnanosat

## João Carlos Fonseca Pinto

Thesis to obtain the Master of Science Degree in

# **Electronics Engineering**

Supervisors: Prof. Rui Manuel Rodrigues Rocha Prof. Moisés Simões Piedade

## **Examination Committee**

Chairperson: Prof. Pedro Miguel Pinto Ramos Supervisor: Prof. Rui Manuel Rodrigues Rocha Member of the Committee: Prof. António Joaquim dos Santos Romão Serralheiro

November 2019

# Declaração

Declaro que o presente documento é um trabalho original da minha autoria e que cumpre todos os requisitos do Código de Conduta e Boas Práticas da Universidade de Lisboa.

#### **Declaration**

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

#### **Agradecimentos**

Em primeiro lugar, uma palavra de agradecimento aos meus orientadores, professor Rui Rocha e professor Moisés Piedade, por todo o suporte, dedicação, ensinamentos e conhecimentos transmitidos, bem como pelas críticas e revisões necessárias ao trabalho realizado nesta dissertação de mestrado.

À equipa ISTnanosat, um obrigado pelos conselhos, apoio e companheirismo durante esta etapa, cuja progressão se deve muito a vocês.

Aos meus pais, Manuela e Fernando Pinto, e aos meus irmãos, Pedro e António Pinto, por me ajudarem a crescer cientificamente e suportarem a minha vida, bem como pela motivação e sacrifício dedicados a mim. Sem vocês nada disto seria possível.

Ao Leite, Tomázio, Tiago, Luís, António e Guilherme, pelo apoio e camaradagem durante todo o meu percurso universitário. Convosco tudo ficou bem mais fácil.

À minha namorada, Joana Chumbo, pela paciência e compaixão que dedicaste a mim durante o nosso tempo. Obrigado pelo respeito, carinho e por acreditares comigo.

# **Abstract**

Since the launch of the first man-made object placed into space orbit, the use of artificial satellites has increased, specially in the last years. These satellites have been used in several applications with different sizes and orbits. The ISTsat-1 is the first nanosatellite developed by the ISTnanosat team, having a 10 cm cubic shape that respects the cubesat standard. This satellite is intended to orbit in the Low Earth Orbit in order to test the reliability of an aircraft tracking system, being its scientific payload, plus collecting information about the space environment.

This master thesis focuses on the evolution of the Communications Processor Board subsystem for the ISTnanosat team, which is divided into two distinct versions. While the first version will be integrated in the aforementioned ISTsat-1, the second version is designed for the integration in future ISTnanosat satellites, being an evolution based on two subsystems flying in the first satellite. As the name implies, these subsystems are designed to support the satellite communications, although they may also be considered for the satellite command and data handling and attitude determination and control. Therefore, possible architectures for them are discussed in this master thesis report, describing the final hardware and software architectures. These architectures take into account the harsh space environment that these subsystems will be subjected to, being some radiation mitigation and subsystem level redundancy techniques addressed as well. Finally, some validation tests are implemented for the acceptance of the developed subsystems, confronting the expected results and the obtained ones.

#### **Keywords**

ISTsat-1, space environment, cubesat, communications, command and data handling, attitude determination and control, high power processor, memory unit, data storage, sensors, actuators, radiation mitigation.

# Resumo

Desde o lançamento do primeiro objecto criado pelo Homem e colocado em órbita espacial, o uso de satélites artificiais tem aumentado, especialmente nos últimos anos. Estes satélites são utilizados em várias aplicações com diferentes tamanhos e órbitas. O ISTsat-1 é o primeiro nanosatélite desenvolvido pela equipa ISTnanosat, tendo uma forma cúbica de 10 cm que respeita o *standard* definido para *cubesats*. Pretende-se que este satélite orbite numa órbita terrestre baixa, tendo como missão científica o teste da fiabilidade de um sistema de rastreamento de aeronaves, além de recolher diversas informações sobre o ambiente espacial.

Esta dissertação foca-se na evolução da Placa do Processador de Comunicações, subsistema pertencente à equipa ISTnanosat que se encontra dividido em duas versões. Enquanto a primeira versão será integrada no satélite ISTsat-1, a segunda versão é desenvolvida para a integração em futuros satélites construídos pela equipa ISTnanosat, sendo uma evolução baseada em dois subsistemas pertencentes ao primeiro satélite. Como o nome indica, estes subsistemas são desenhados para suportar as comunicações do satélite, apesar de poderem ser também considerados para o tratamento de dados e comandos do satélite e para a determinação e controlo da sua atitude. Portanto, neste relatório de dissertação são discutidas possíveis arquitecturas para estes subsistemas, descrevendo as arquitecturas finais de *hardware* e *software*. Estas têm em consideração o ambiente espacial severo no qual estes subsistemas vão operar, sendo por isso abordadas algumas técnicas de mitigação de radiação e de redundância a nível do subsistema. Para concluir, alguns testes de validação são implementados para a aprovação dos subsistemas desenvolvidos, confrontando os resultados esperados com os resultados obtidos.

#### **Palavras Chave**

ISTsat-1, ambiente espacial, *cubesat*, comunicações, tratamento de dados e comandos, determinação e controlo de atitude, unidade de alto processamento, unidade de memória, armazenamento de dados, sensores, actuadores, mitigação de radiação.

# **Contents**

| 1 | Intro | oductio   | on                                                      | 2  |

|---|-------|-----------|---------------------------------------------------------|----|

|   | 1.1   | Motiva    | ation                                                   | 3  |

|   | 1.2   | Object    | tives                                                   | 4  |

|   | 1.3   | Repor     | t organization                                          | 5  |

| 2 | Sate  | ellite Cl | assification and Space Environment. ISTsat-1 Case Study | 6  |

|   | 2.1   | Satelli   | te Categorization                                       | 6  |

|   | 2.2   | The gr    | rowth of small satellites launches                      | 8  |

|   | 2.3   | ISTsat    | t-1 and the Fly Your Satellite! programme               | 9  |

|   | 2.4   | Space     | radiation environment                                   | 11 |

|   |       | 2.4.1     | Radiation mitigation                                    | 12 |

| 3 | Stat  | e of the  | e Art                                                   | 14 |

|   | 3.1   | Comm      | nunication Systems                                      | 15 |

|   | 3.2   | Comm      | nand and Data Handling                                  | 16 |

|   |       | 3.2.1     | High power processing units                             | 16 |

|   |       | 3.2.2     | Memory unit components                                  | 16 |

|   | 3.3   | Attitud   | le Determination and Control System                     | 17 |

|   |       | 3.3.1     | ADCS sensors                                            | 19 |

|   |       | 3.3.2     | ADCS actuators                                          | 20 |

|   | 3.4   | Comm      | nercial OBC and communication modules for cubesats      | 21 |

| 4 | Sys   | tem Ar    | chitecture                                              | 26 |

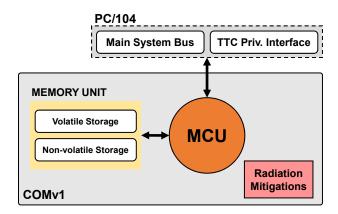

|   | 4.1   | COMv      | 1.1 Architecture                                        | 26 |

|   |       | 4.1.1     | Communication and C&DH requirements                     | 26 |

|   |       | 4.1.2     | Subsystem IO requirements                               | 27 |

|   | 4.2   | COMv      | 2 Architecture                                          | 28 |

|   |       | 4.2.1     | ADCS requirements                                       | 28 |

|   |       | 4.2.2     | Communication and C&DH requirements                     | 29 |

|   |       | 4.2.3     | Subsystem IO requirements                               | 29 |

|   |       | 424       | Architecture solutions                                  | 30 |

| 5 | Sys | stem Implementation 32                      |                                                              |    |  |  |  |  |  |

|---|-----|---------------------------------------------|--------------------------------------------------------------|----|--|--|--|--|--|

|   | 5.1 | COMv                                        | 1.1 Hardware project                                         | 32 |  |  |  |  |  |

|   |     | 5.1.1                                       | High-power processing unit selection                         | 33 |  |  |  |  |  |

|   |     | 5.1.2                                       | Subsystem Power and PCB design                               | 34 |  |  |  |  |  |

|   |     | 5.1.3 External Watchdog Timer               |                                                              |    |  |  |  |  |  |

|   |     | 5.1.4                                       | External memory unit                                         | 35 |  |  |  |  |  |

|   |     | 5.1.5                                       | Radiation protections for the external memory unit           | 39 |  |  |  |  |  |

|   |     | 5.1.6                                       | Communication peripherals                                    | 42 |  |  |  |  |  |

|   |     | 5.1.7                                       | COMv1.1 subsystem flight model board                         | 44 |  |  |  |  |  |

|   | 5.2 | COMv                                        | <sup>7</sup> 2 Hardware project                              | 45 |  |  |  |  |  |

|   |     | 5.2.1                                       | High-power processing unit selection                         | 46 |  |  |  |  |  |

|   |     | 5.2.2                                       | External memory unit                                         | 48 |  |  |  |  |  |

|   |     | 5.2.3                                       | Subsystem power regulation                                   | 50 |  |  |  |  |  |

|   |     | 5.2.4                                       | Power cut-off and current measurement circuits               | 52 |  |  |  |  |  |

|   |     | 5.2.5                                       | Capacitor bank for the time reference                        | 54 |  |  |  |  |  |

|   |     | 5.2.6                                       | Solar panels interface                                       | 56 |  |  |  |  |  |

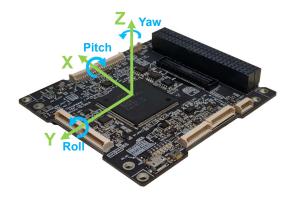

|   |     | 5.2.7                                       | Attitude determination sensors                               | 56 |  |  |  |  |  |

|   |     | 5.2.8                                       | Attitude determination actuators                             | 60 |  |  |  |  |  |

|   |     | 5.2.9                                       | External Watchdog Timer                                      | 60 |  |  |  |  |  |

|   |     | 5.2.10                                      | Communication peripherals                                    | 61 |  |  |  |  |  |

|   |     | 5.2.11                                      | Power distribution and protections for the subsystem modules | 62 |  |  |  |  |  |

|   |     | 5.2.12                                      | COMv2 subsystem and memory daughterboard prototype boards    | 63 |  |  |  |  |  |

|   | 5.3 | Softwa                                      | are Implementation                                           | 65 |  |  |  |  |  |

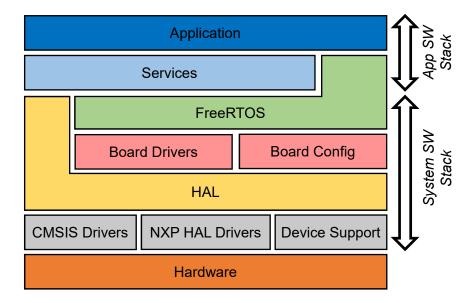

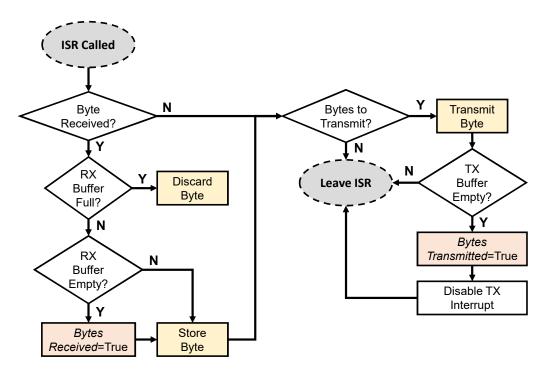

|   |     | 5.3.1                                       | Hardware Abstraction Layer                                   | 66 |  |  |  |  |  |

|   |     | 5.3.2                                       | Board hardware drivers                                       | 69 |  |  |  |  |  |

|   |     | 5.3.3                                       | Real-Time Operating System                                   | 70 |  |  |  |  |  |

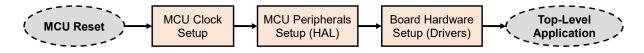

|   |     | 5.3.4                                       | Board configuration files                                    | 71 |  |  |  |  |  |

|   |     | 5.3.5                                       | Boot sequence for top-level application                      | 71 |  |  |  |  |  |

| 6 | Sys | tem Va                                      | lidation                                                     | 73 |  |  |  |  |  |

|   | 6.1 | Memo                                        | ry units validation                                          | 73 |  |  |  |  |  |

|   | 6.2 | Validation of the communication peripherals |                                                              |    |  |  |  |  |  |

|   | 6.3 | ADCS                                        | modules validation                                           | 77 |  |  |  |  |  |

| 7 | Con | clusio                                      | n and Future Work                                            | 87 |  |  |  |  |  |

| ٨ | ICT | ISTeet 1 ORC architecture                   |                                                              |    |  |  |  |  |  |

# **List of Figures**

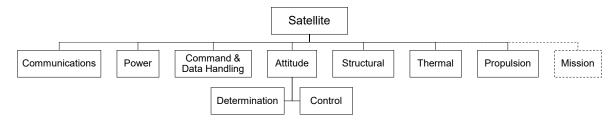

| 2.1  | Satellite functions and subsystems                  | 8  |

|------|-----------------------------------------------------|----|

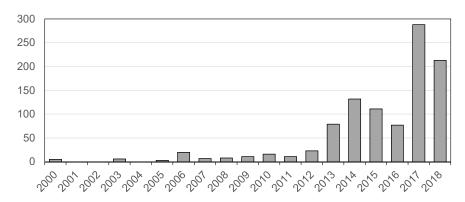

| 2.2  | Evolution of cubesat nanosatellite launches         | 9  |

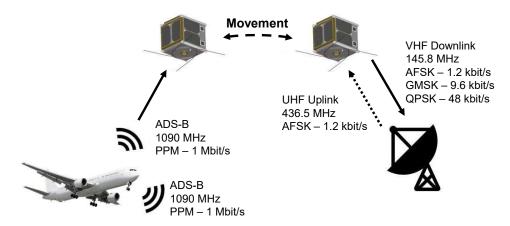

| 2.3  | ADS-B store and forward mechanism                   | 10 |

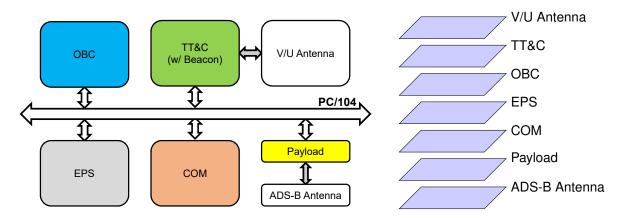

| 2.4  | ISTsat-1 architecture and subsystem stacking layout | 11 |

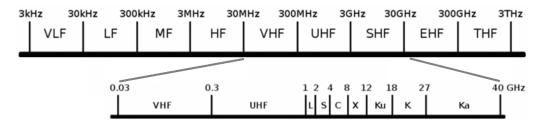

| 3.1  | Satellite radio frequency spectrum                  | 15 |

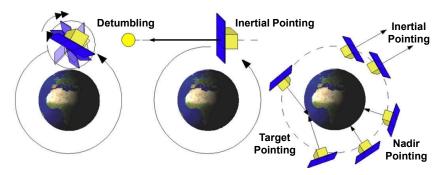

| 3.2  | Satellite orientation modes                         | 18 |

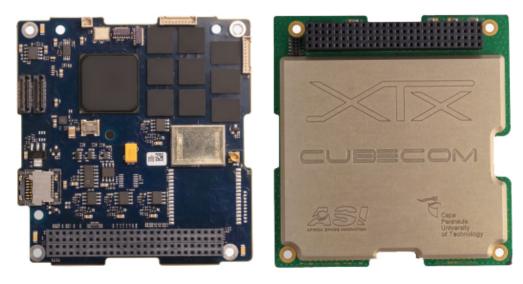

| 3.3  | GOMspace SDR integrated module                      | 21 |

| 3.4  | GOMspace OBC and V/U integrated module              | 22 |

| 3.5  | ISIS OBC and S-band transmitter modules             | 23 |

| 3.6  | AAC Clyde Space OBC and X-band transmitter modules  | 24 |

| 4.1  | COMv1.1 architecture                                | 28 |

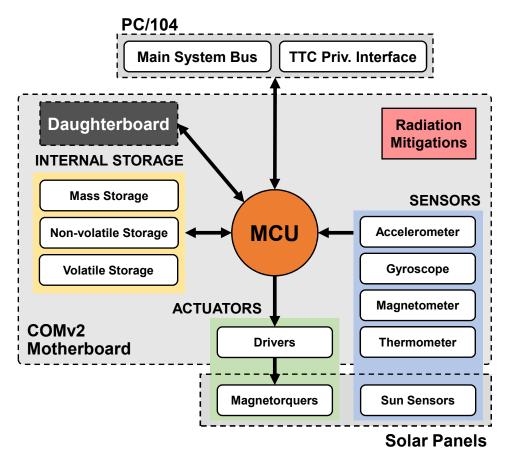

| 4.2  | COMv2 architecture                                  | 31 |

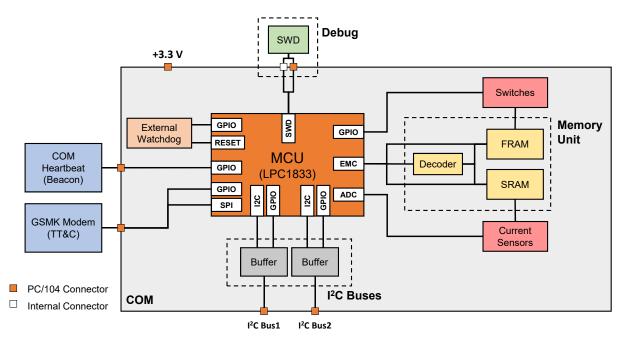

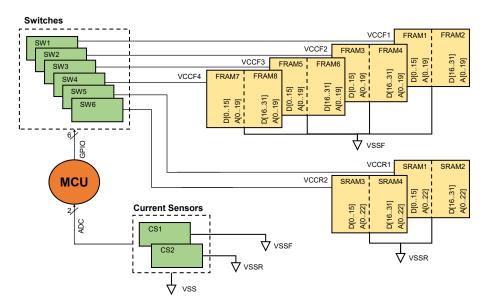

| 5.1  | COMv1.1 hardware architecture                       | 33 |

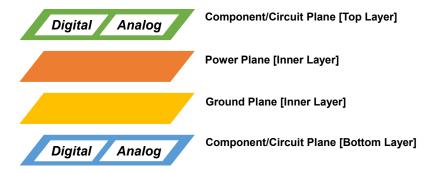

| 5.2  | PCB layer design scheme                             | 34 |

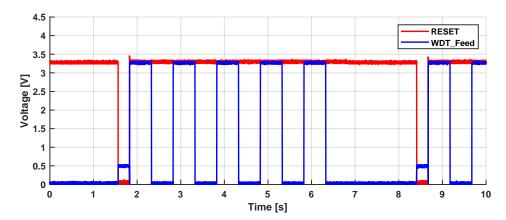

| 5.3  | COM external watchdog timer operation               | 35 |

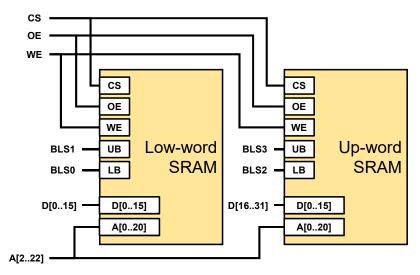

| 5.4  | ExtMC 32-bit to 16-bit memory interface             | 36 |

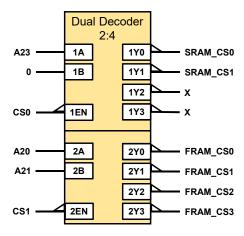

| 5.5  | COMv1.1 memory decoding unit                        | 37 |

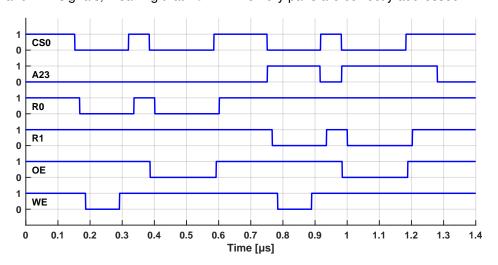

| 5.6  | COMv1.1 SRAM memory decoding operation              | 38 |

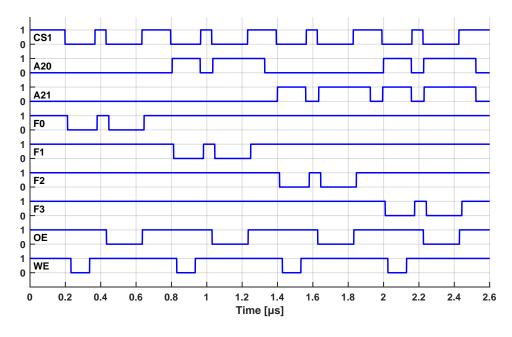

| 5.7  | COMv1.1 FeRAM memory decoding operation             | 38 |

| 5.8  | COMv1.1 radiation protections for the memory unit.  | 39 |

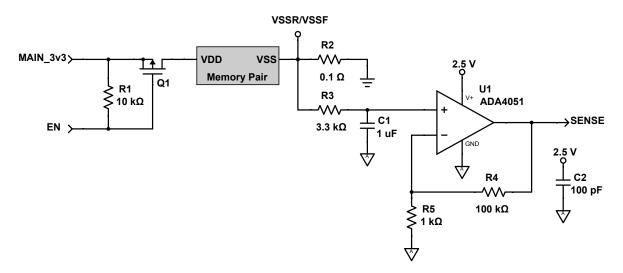

| 5.9  | COMv1.1 current sensing and power cut-off           | 40 |

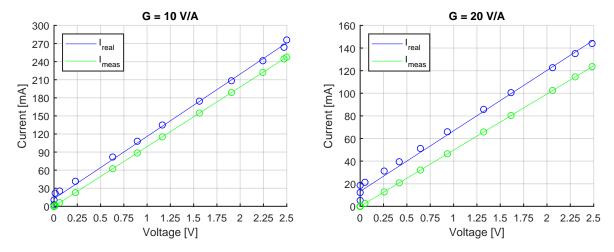

| 5.10 | COMv1.1 current sensors operation                   | 42 |

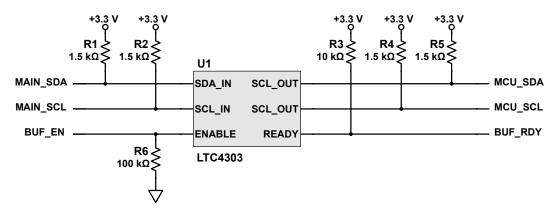

| 5.11 | I <sup>2</sup> C bus buffer implementation          | 43 |

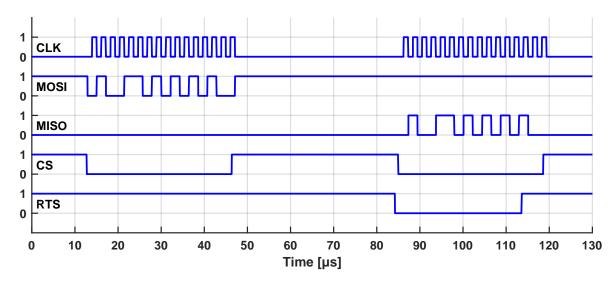

| 5.12 | Operation of the dedicated SPI interface            | 44 |

| 5.13 | COMv1.1 final board modules                         | 45 |

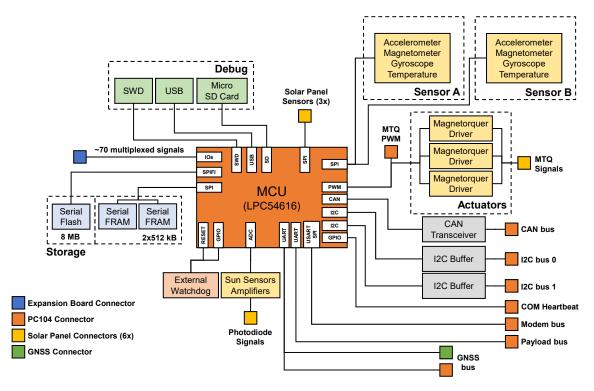

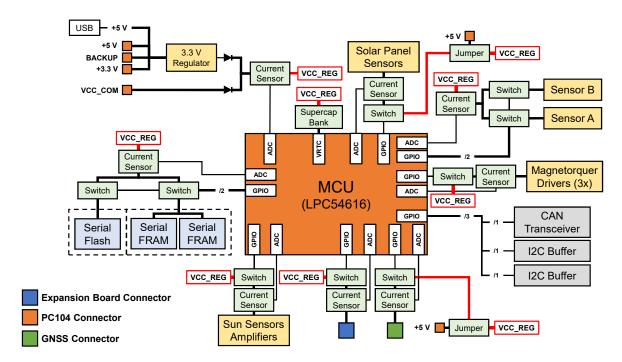

| 5.14 | COMv2 hardware architecture                          | 46 |

|------|------------------------------------------------------|----|

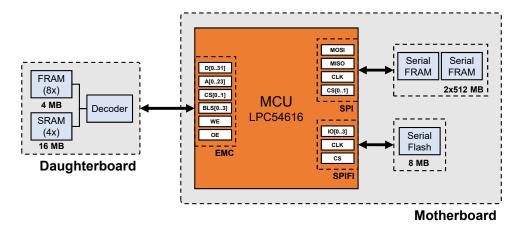

| 5.15 | COMv2 memory unit diagram                            | 50 |

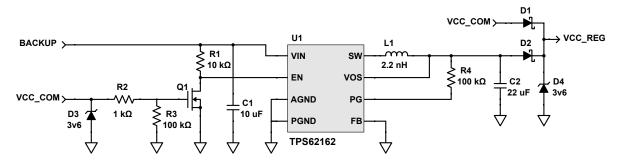

| 5.16 | COMv2 power supply regulation circuit                | 51 |

| 5.17 | COMv2 backup power supply operation                  | 51 |

| 5.18 | COMv2 power switch and current sensing circuit       | 52 |

| 5.19 | COMv2 current sensors operation                      | 54 |

| 5.20 | COMv2 RTC capacitor bank circuit                     | 55 |

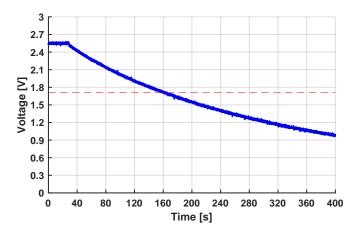

| 5.21 | COMv2 RTC capacitor bank operation                   | 56 |

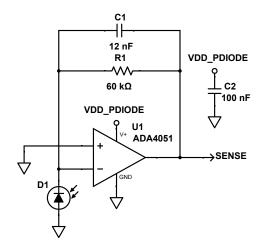

| 5.22 | COMv2 sun sensor amplifying circuit                  | 59 |

| 5.23 | COMv2 power distribution                             | 63 |

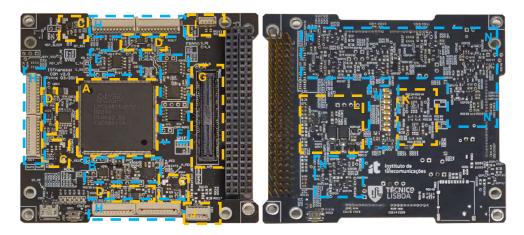

| 5.24 | COMv2 prototype board modules                        | 64 |

| 5.25 | COMv2 memory expansion daughterboard modules         | 64 |

| 5.26 | COM software stack                                   | 66 |

| 5.27 | COM byte reception and transmission Flowchart        | 68 |

| 5.28 | COM boot sequence                                    | 71 |

| 6.1  | COMv2 referential axis system                        | 78 |

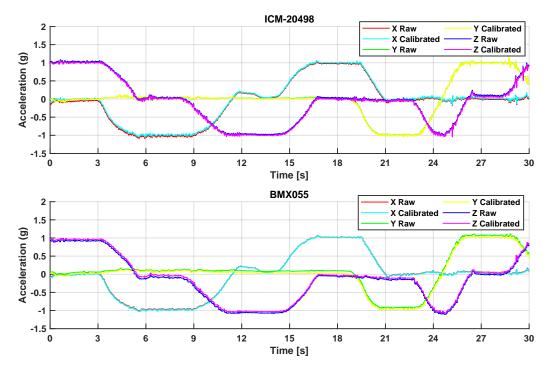

| 6.2  |                                                      | 79 |

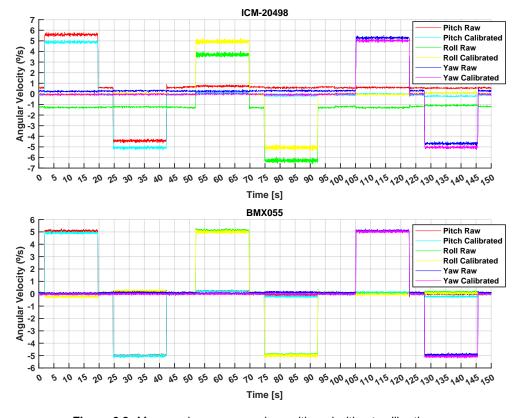

| 6.3  | COMv2 gyroscope calibration results                  | 80 |

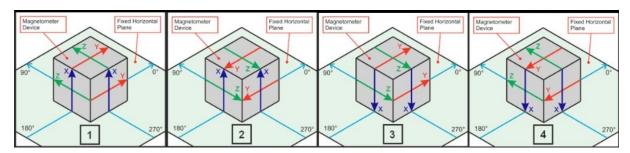

| 6.4  | Magnetometer calibration orientations                | 82 |

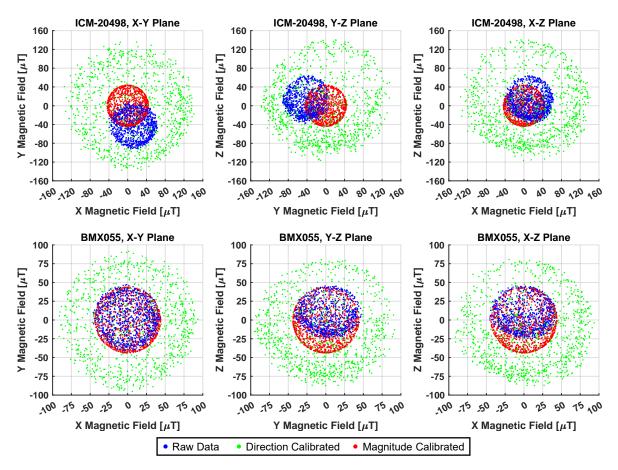

| 6.5  | COMv2 magnetometer calibration results               | 83 |

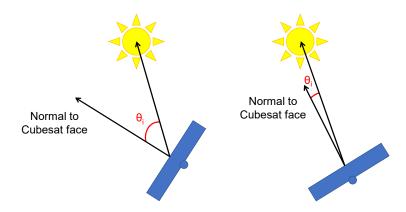

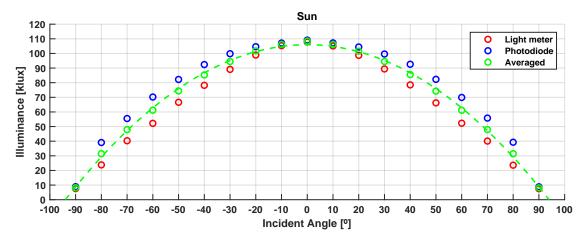

| 6.6  | Light incidence angles based on a rotating stand     | 83 |

| 6.7  | COMv2 sun sensor amplifiers performance              | 84 |

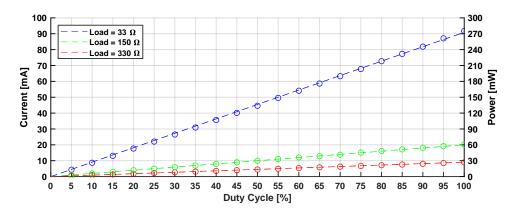

| 6.8  | COMv2 magnetorquer drivers performance               | 85 |

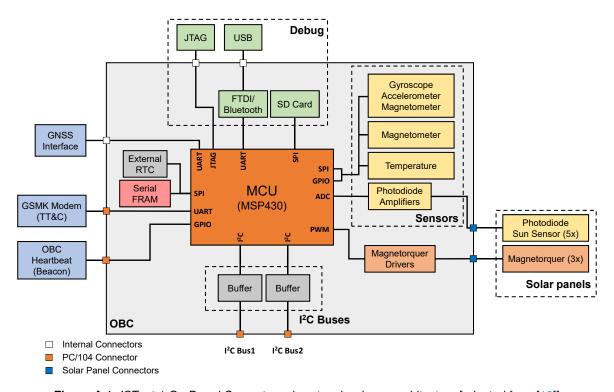

| A.1  | ISTsat-1 OBC hardware architecture                   | 92 |

| A.2  | ISTsat-1 OBC RTC capacitor bank circuit              | 94 |

|      | ISTsat-1 OBC time reference capacitor bank operation | 94 |

# **List of Tables**

| 2.1  | Summary of single event effects                          | 12 |

|------|----------------------------------------------------------|----|

| 3.1  | Comparison of memory technologies                        | 17 |

| 3.2  | Attitude sensors comparison                              | 20 |

| 3.3  | Attitude actuators comparison                            | 20 |

| 3.4  | Summary of studied commercial modules                    | 25 |

| 5.1  | COMv1.1 microcontroller requirements                     | 33 |

| 5.2  | ExtMC BLS logic table                                    | 36 |

| 5.3  | COMv1.1 memory decoding logic                            | 37 |

| 5.4  | COMv2 microcontroller requirements                       | 46 |

| 5.5  | Comparison of available microcontrollers for the COMv2   | 47 |

| 5.6  | COMv2 current sensor values                              | 53 |

| 5.7  | Magnetometer MEMS comparison                             | 57 |

| 5.8  | Accelerometer MEMS comparison                            | 57 |

| 5.9  | Gyroscope MEMS comparison                                | 57 |

| 5.10 | Electrical specifications of the COMv2 ADCS sensors      | 58 |

| 5.11 | Comparison of I <sup>2</sup> C and CAN                   | 61 |

| 6.1  | Incremental test example                                 | 74 |

| 6.2  | Performance comparison between memory units              | 76 |

| 6.3  | Performance comparison between communication peripherals | 77 |

| 6.4  | Expected values for different accelerometer orientations | 78 |

| 6.5  | Expected values for different gyroscope orientations     | 80 |

# **Acronyms**

ADCS Attitude Determination and Control System

ADC Analog-to-Digital Converter

**ADM** Antenna Deployment Mechanism

ADS-B Automatic Dependent Surveillance-Broadcast

AFSK Audio Frequency-Shift Keying

**AIS** Automatic Identification System

API Application Programming Interface

**BGA** Ball Grid Array

**BLS** Byte Lane Select

**CAN** Controller Area Network

**C&DH** Command and Data Handling

**CMSIS** Cortex Microcontroller Software Interface Standard

**COM** Communications Processor Board

**COTS** commercial off-the-shelf

**CS** Chip Select

DAC Digital-to-Analog Converter

**DoF** Degrees of Freedom

**DRAM** Dynamic Random Access Memory

**DSP** Digital Signal Processor

**EMC** Electromagnetic Compatibility

**ExtMC** External Memory Controller

eMMC Embedded Multimedia Card

**EPS** Electrical Power System

ESA European Space Agency

FeRAM Ferro-electric Random Access Memory

FPGA Field Programmable Gate Array

FPU Floating-Point Unit

FYS Fly Your Satellite!

GCR Galactic Cosmic Rays

**GNSS** Global Navigation Satellite System

**GPIO** General Purpose Input/Output

**GPS** Global Positioning System

**GSMK** Gaussian Minimum Shift Keying

**GS** Ground Segment

**HAL** Hardware Abstraction Layer

I<sup>2</sup>C Inter-Integrated Circuit

IC integrated circuit

**IDE** Integrated Development Environment

**IMU** Inertial Measurement Unit

IO I/Oinput/output

**IPC** Inter-Process Communication

ISIS Innovative Solutions in Space

ISR Interrupt Service Routine

**ISS** International Space Station

IST Instituto Superior Técnico

JTAG Joint Test Action Group

**LEO** Low Earth Orbit

LQFP Low Profile Quad Flat Pack

MBM motherboard module

**MCU** microcontroller

**MEMS** microelectromechanical systems

**MEO** Medium Earth Orbit

MISO Master In Slave Out

MOSFET metal-oxide-semiconductor field-effect transistor

MOSI Master Out Slave In

MRAM Magnetoresistive Random Access Memory

**OBC** On-Board Computer

**OE** Output Enable

PCB Printed Circuit Board

**PPM** Pulse Position Modulation

PWM Pulse Width Modulation

**QPSK** Quadrature Phase-Shift Keying

**RAM** Random Access Memory

RTC Real-Time Clock

RTOS Real-Time Operating System

RTS Request to Send

SCL Serial Clock Line

SDA Serial Data Line

SDRAM Synchronous Dynamic Random Access Memory

SDR Software Defined Radio

SD Secure Digital

**SEE** Single Event Effect

SEL Single Event Latchup

SLC single-level cell

SoC system-on-a-chip

SOI Silicon on Insulator

SPI Serial Peripheral Interface

SPIFI Serial Peripheral Interface Flash Interface

**SRAM** Static Random Access Memory

SWD Serial Wire Debug

**TID** Total Ionising Dose

TRL Technology Readiness Level

TT&C Tracking, Telemetry and Control

**UART** Universal Asynchronous Receiver Transmitter

**UHF** Ultra High Frequency

**USART** Universal Synchronous Asynchronous Receiver Transmitter

**USB** Universal Serial Bus

VHF Very High Frequency

V/U Very High and Ultra High Frequency

WDT Watchdog Timer

**WE** Write Enable

WMM World Magnetic Model

# **Chapter 1**

# Introduction

Since the launch of the first artificial Earth satellite into an elliptical Low Earth Orbit, the Sputnik 1 from the Soviet Union in October 1957, the use of artificial satellites has increased, specially in the last years. These satellites have been used in several applications, mainly for communications, scientific, educational and military purposes. Due to the harsh space environment, the manufacturing and the necessary quality assurance and expertise to ensure a high-reliability system that does not fail in orbit is highly expensive. However, due to the technology evolution and to the increase of satellite standardisation, the cost of producing a satellite has decreased, enabling universities to increasingly launch small satellites into space.

One of these standardisations is the Cubesat<sup>1</sup>. This small and low cost satellite is a 10 cm cube unit with a maximum mass of 1.33 kg, which can be stacked to form larger satellites. The use of these satellites was initially intended for Low Earth Orbits, performing scientific researches and exploring new space technologies when the use of larger satellites was not plausible due to their cost. Therefore, a cubesat can be launched into space to test the feasibility of new technologies before deploying bigger satellites. Furthermore, this miniaturised satellite also allows educational studies to be done without a great expense. Nowadays, cubesats are starting to be also considered for deep space missions.

To aid some of these educational space activities, the Fly Your Satellite! (FYS) programme, which is designed and managed by the European Space Agency (ESA) Education Office in collaboration with European universities, has the objective of complementing the academic education of university students, inspiring and preparing them for a more effective introduction to a future work in the space sector. Between 2008 and 2019, this Education Office has enabled more than 10 cubesats to be launched into space, three of them in the first FYS edition: the e-st@r1 from Italy, the AAUSAT-4 from Denmark and the OUTTI-1 from Belgium [1].

<sup>&</sup>lt;sup>1</sup>The Cubesat standard design was firstly proposed in 1999 by professors Jordi Puig-Suari of California Polytechnic State University and Bob Twiggs of Stanford University [2].

Currently participating in the FYS programme, the ISTsat-1 is an 1U cubesat being developed by the ISTnanosat team, formed by students, professors and radioamateurs settled at Instituto Superior Técnico (IST). This satellite is one of the six educational space projects currently participating in the second edition of the FYS programme.

In addition to the educational purpose that builds on the enthusiasm of the students for space science and technology, complementing their education, the ISTsat-1 mission carries out a feasibility study of the use of nanosatellites to receive the signals of the Automatic Dependent Surveillance-Broadcast (ADS-B) system, which is used in the monitoring of aircraft specially in areas not covered by terrestrial stations. Therefore, the ISTsat-1 main mission is to collect relevant data from several aircraft about their flight status, temporally store it to be further forwarded to a ground station.

The nanosatellite that is being developed in-house is composed of four main subsystems plus the required structure and communication antennas, with the correspondent Antenna Deployment Mechanism (ADM), plus an additional subsystem dedicated to its specific payload. This satellite also follows a typical system structure of a cubesat, whose architecture is explained in Chapter 2.

#### 1.1 Motivation

Nowadays, the existence of specialised companies that build and sell cubesat subsystem modules brings some advantages, as these modules have a guaranteed flight heritage, meaning that they have been successfully used in space and assuring their correct operation with low chance of failure during a mission. However, these commercial modules are highly expensive and inflexible, as they may not be reconfigured or remodulated into a custom mission. Three examples of these companies are *GOMspace*<sup>2</sup>, *Pumpkin Space Systems*<sup>3</sup> and *AAC Clyde Space*<sup>4</sup>.

However, in the ISTsat-1, the first cubesat built by the ISTnanosat team, all subsystems are designed in-house, only with the purchase of some specialised space components like the V/U antenna and its ADM used for the communication with the Ground Segment (GS), and the solar panels used in the energy harvesting. This means that the creation of the majority of the satellite modules brings some independence upon external implementations and increases the educational purpose of building a custom satellite rather than using a commercial one. These implementations become then more adaptable to the ISTsat-1 specifications as its components can be criteriously chosen, taking advantage of the small satellite space and reducing the power consumption. Because the system is built from scratch, the knowledge of the entire system is persistent during all phases of the satellite engineering, which could not be possible with a commercial module.

<sup>&</sup>lt;sup>2</sup>GOMspace website: https://gomspace.com/home.aspx

<sup>&</sup>lt;sup>3</sup>Pumpkin Space Systems website: https://www.pumpkinspace.com/

<sup>&</sup>lt;sup>4</sup>AAC Clyde Space website: https://www.aac-clyde.space

Considering the Communications Processor Board (COM) that is one of the subsystems present in the ISTsat-1, an unfinished COMv1.0 iteration was done by the former IST student Tiago Carvalho, whose work is detailed in [3]. This iteration, which had some design issues in its external memory unit that needed to be solved for the COMv1 integration in the ISTsat-1 in order to fulfil its data storage requirements, served also as a motivation and starting point for this master thesis. Furthermore, the idea of an evolution of this subsystem to be integrated in future ISTnanosat cubesats also gives an extra motivation to accomplish the objectives set for this master thesis, which are further described.

## 1.2 Objectives

The purpose of this master thesis report is to describe the evolution of the Communications Processor Board subsystem developed for the ISTnanosat team. The work developed throughout this evolution focuses on the implementation and validation of two versions of this subsystem. The first objective of this master thesis is to detail the finished design of the COM first version (from now on referred to as **COMv1.1**), which integrates on the ISTsat-1 satellite and already had an unfinished iteration as aforementioned.

The COMv1.1 is mainly responsible for the ISTsat-1 communication stack handling and for the satellite data storage when the satellite is in its normal operational mode. In detail, this subsystem must:

- Be able to process the communication stack transceived between the satellite and the Ground Segment.

- Manage and report the correct operation of the various modules integrated in the subsystem itself.

- Handle the storage of telemetry data that reports the operation of the various modules from the satellite subsystems, plus the storage of payload data related with the satellite mission.

- Resort to well-defined interfaces to communicate with the remaining subsystems in the spacecraft.

Additionally to these requirements, the COMv1.1 may also assume the satellite control in its backup operational mode, when the On-Board Computer (OBC) subsystem has failed.

The second objective of this master thesis report is to describe a prototype design of the COM second version (from now on referred to as **COMv2**), being designed for an integration in the next generation of ISTnanosat team cubesats. The COMv2 may be considered as a merge of two subsystems existent on the ISTsat-1, namely the aforementioned COMv1.1 and its On-Board Computer, being an evolution of both. Therefore, additionally to the requirements already defined for the COMv1.1, this subsystem must:

- Determine the satellite attitude through the use of a system of inertial sensors.

- Control this attitude through control signals set on satellite actuators.

Control the satellite operation, requesting telemetry data from the remaining subsystems and reporting hazardous events to the Ground Segment whenever possible through the subsystem dealing with the communication radio link.

Both COM subsystems described in this master thesis must also fulfil the cubesat standards, which restrains their dimension and the size of the modules used. Furthermore, due to the reduced energy budget, which is shared with the remaining subsystems in the satellite, the power consumption of this system must also be minimised as much as possible.

## 1.3 Report organization

This report is divided into 7 chapters.

Chapter 1 introduces this document, with a motivation and the objectives of this master thesis.

Chapter 2 describes the main subsystems and functions existent in common satellites, focusing on the increase of small satellite launches. Furthermore, a description of the aforementioned ISTsat-1 cubesat is done as an example of these small satellites. Finally, a brief explanation of the space radiation environment is done with the most significant radiation effects that may harm a satellite.

Chapter 3 provides a state of the art of communication systems, Command and Data Handling systems and Attitude Determination and Control Systems, which are the foundation for both subsystems developed in this master thesis. A comparison between some commercial On-Board Computers and communication modules is also done.

Chapter 4 details the architecture chosen for both COMv1.1 and COMv2 subsystems, listing all the requirements set for them.

Chapter 5 characterises the hardware and software implementations done on both subsystems, detailing the hardware and circuitry choices and the software designed to meet the requirements and architectures previously set.

Chapter 6 outlines the validation of the various modules implemented in these subsystems, evaluating their performance through specific tests and measurements.

Chapter 7 compares the systems developed to the objectives initially set, describing all achievements and problems experienced throughout the work developed in this master thesis. Finally, some future work is also detailed in this chapter.

# **Chapter 2**

# Satellite Classification and Space Environment. ISTsat-1 Case Study

Since the early times, mankind has dreamed about how life beyond planet Earth could be, deep into space. The first satellite built by mankind that successfully reached space was the *Sputnik* 1<sup>1</sup>, launched on 4 October 1957. This satellite was a polished metal sphere with 58 cm of diameter and four radio antennas that broadcasted beacons (radio pulses transmitted periodically) detected by radio amateurs. This satellite orbited on a Low Earth Orbit, which extends between 160 km and 1 000 km of altitude.

Months later, on 31 January 1958, the American *Explorer 1*<sup>2</sup> was launched, with a missile format with 200 cm of length, 15 cm of diameter and 14 kg of weight, discovering the Van Allen radiation belt. This satellite got into higher Medium Earth Orbits, which extend between 1 000 km and 22 000 km.

These satellites were the first man made objects that were launched into space, starting the Space Race. Since then, the space industry has evolved with different satellite missions and into different standardisations. This chapter serves the purpose of categorising the satellite classification and their several subsystems, focusing on the increase of nanosatellite launches and describing the ISTsat-1 satellite in detail. A brief description of the space radiation environment is also done, as well as its impact in these nanosatellites.

# 2.1 Satellite Categorization

In the last years, size and weight of artificial satellites has steadily being reduced as technologies evolved, bringing the idea of classifying general satellites by their size.

<sup>&</sup>lt;sup>1</sup>https://en.wikipedia.org/wiki/Sputnik\_1 - Accessed on 23/12/2017.

<sup>&</sup>lt;sup>2</sup>https://en.wikipedia.org/wiki/Explorer\_1 - Accessed on 23/12/2017.

Therefore, according to [4], satellites can be categorised by their weight as:

- Large satellites Mass bigger than 1000 kg;

- Medium satellites Mass between 500 kg and 1000 kg;

- Minisatellites Mass between 100 kg and 500 kg;

- Microsatellites Mass between 10 kg and 100 kg;

- Nanosatellites Mass between 1 kg and 10 kg;

- Picosatellites Mass between 0.1 kg and 1 kg;

- Femtosatellites Mass lower than 0.1 kg.

Although the various satellites built throughout the years may vary significantly in their size, their systems share common functionalities that can be pointed out. According to [5] and [6], the main functions and subsystems that can be found in a satellite are:

- Communications A communication system allows the spacecraft to transmit data and telemetry to Earth and receive commands from it using transceivers. This communication is usually based in the radio frequency spectrum, with frequencies ranging from 30 MHz to 40 GHz, although laser based optical communications are also used. Depending on the satellite purpose and mission, this may be a heavy portion of the satellite.

- Power A system is responsible for the power management and energy harvesting. Solar panels

are used in combination with batteries to provide a constant source of electrical power on the

satellite, even when the satellite is in eclipse without direct sunlight.

- Command and Data Handling Several subsystems of a satellite are managed and controlled, dealing also with the data storage, filtering and compression.

- Attitude A system monitors (Determination) and acts (Control) on the satellite attitude, positioning it constantly in its orbit, minimising perturbations like the solar radiation pressure, the interaction of the Earth's magnetic field and the gravity gradient.

- **Structural** A satellite structure supports and mechanically connects all the subsystems of the spacecraft. However, the structural design must take into account the violent shocks and vibrations that a satellite faces during the rocket launch, being designed to withstand these forces.

- **Thermal** As many satellite components have rigid temperature ranges in which they operate correctly, specially electronic components, the thermal subsystem regulates the temperature of the various components in a satellite so that they can operate correctly, maintaining their temperature within their specific range, either at eclipse or at direct sunlight.

- Propulsion A system aids the satellite to get or stay in orbit, through chemical or electrical motors

used to move the satellite back into the correct orbit when either atmospheric drag, magnetic fields

or solar winds deflect the satellite out of its correct trajectory. The propulsion subsystem may also

be considered as an active part of the satellite attitude control.

In addition to these subsystems, additional ones can be added according to each satellite developer, commonly related with the its mission, whether it is a commercial, scientific or military mission. In Figure 2.1, a summarised typical satellite structure is shown.

Figure 2.1: Typical satellite structure and their correspondent functions and subsystems.

## 2.2 The growth of small satellites launches

The use of many small satellites with specific functionalities or missions has increased, rather than using a single and bigger satellite with the same functionalities embedded together in it. This approach has allowed to reduce the cost of the missions, as satellites are built easier, cheaper and faster. Due to their small size, these satellites can also be launched in groups simultaneously from a single spacecraft, something that can not be done with a bigger satellite.

However, some limitations to the use of small satellites can be pointed out. Due to their size, these satellites stay less time in lower orbits than bigger satellites, being in operation for less time. Since the implementation of a propulsion subsystem is challenging due to the lack of space in a small satellite, this subsystem is usually not implemented and the satellite operational time in orbit is not expanded, as this subsystem could be useful to help a satellite keep itself in orbit. Beyond that, the use of less electronic components in small satellites reduces their processing power, energy storage and, consequently, causes less over-the-air data transmission.

Nevertheless, with this decrease in the satellite size, the creation of commercial models brought both cost and time reduction in the satellite manufacturing, as the access to space technology became easier. With similar satellite modules and structures, space deployers also became standardised, increasing the usage of standard satellites and their launches. According to [7], almost 1000 cubesat nanosatellites were launched to space between 2000 and 2018, as shown in Figure 2.2 depicting the evolution of launches per year. Their main missions can be divided into:

- **Communications**, as the primary mission is to relay communications point-to-point, being amateur radio service and Automatic Identification System (AIS) tracking some examples.

- **Educational**, as the main mission is the educational or professional training of the participants in the spacecraft design. Any science returns or technology demonstrations are of secondary value.

- Earth Imaging, as the mission returns images of the Earth for commercial and research purposes.

- **Science**, as the mission collects data for scientific research, including Earth science, atmospheric science or space weather.

- **Technology Demonstration**, as the mission involves the first flight of a new technology or design, advancing one or more Technology Readiness Levels<sup>3</sup>.

- Military, when the mission has military relevance that does not fit in the aforementioned categories.

Figure 2.2: Evolution of the cubesat nanosatellite launches between 2000 and 2018 [Adapted from [7]].

## 2.3 ISTsat-1 and the Fly Your Satellite! programme

With the increased use of low-cost small satellites, the number of educational space studies made by worldwide universities has been increasing in the last years. Allied to that, some specialised space organisations have created programmes to help the launch of these studies and thus introduce university students to the space sector. One of these space organisations is the European Space Agency, whose Education Office has created the Fly Your Satellite! programme. In collaboration with several European universities, this programme has the objective of complementing the academic education of university students, inspiring and preparing them for a more effective introduction to a future work in the space sector [1].

Since 2008, this Education Office has enabled more than 10 cubesats to be launched into space. In the first FYS edition occurring between 2013 and 2016, three 1U cubesat satellites were launched into space. The current second FYS edition consists of four programme phases, where the cubesat teams have to achieve pre-defined objectives and must undergo reviews conducted by ESA specialists [1].

Being one of the educational space projects participating in the current second edition of the Fly Your Satellite! programme, the ISTsat-1 is an 1U cubesat being developed by the ISTnanosat team at Insti-

<sup>&</sup>lt;sup>3</sup>Technology Readiness Level (TRL) is a type of measurement system used to assess the maturity level of a particular technology, which is evaluated against the parameters of different increasing levels of requirements [6].

tuto Superior Técnico, formed by students, professors and radioamateurs from the Portuguese AMRAD (Associação Portuguesa de Amadores de Rádio para a Investigação, Educação e Desenvolvimento).

In addition to the educational purpose that builds the enthusiasm of students for space science and that complements their education, the ISTsat-1 mission carries out a feasibility study of the use of low-cost planar antennas in nanosatellites to receive the signals of the ADS-B system, as these nanosatellites may be used in the monitoring of aircraft in areas not covered by terrestrial stations. Therefore, the ISTsat-1 will collect relevant data from several aircraft about their status, temporally store it to be forwarded further to a ground station, as shown in Figure 2.3.

Figure 2.3: ADS-B message reception and storage, followed by the forwarding to the GS when possible.

The nanosatellite being developed is composed of four main subsystems plus an additional one dedicated to its specific mission, following a typical structure of a cubesat. These subsystems are:

- The **Tracking**, **Telemetry and Control** (**TT&C**), responsible for the data uplink and downlink between the satellite and several ground stations, using a UHF frequency of 436.5 MHz and data rate of 1.2 kbit/s for uplink, and a VHF frequency of 145.8 MHz and data rate varying from 1.2 kbit/s up to 48 kbit/s for downlink, as shown in Figure 2.3. Additionally, it has a **Beacon**, which is used to identify and locate the spacecraft, being independent from the rest of the satellite communication system, broadcasting a Morse message with its identifier and some satellite telemetry regarding the remaining subsystems operation. Both TT&C and Beacon share the same V/U antenna for communication.

- The On-Board Computer (OBC), combining two different functionalities:

- The Attitude Determination and Control System (ADCS), responsible of keeping the satellite well-positioned and in orbit, while collecting data about its space location.

- The Command and Data Handling (C&DH), responsible for the monitor and control of the other subsystems and for the satellite housekeeping, being considered the satellite main controller.

- The Electrical Power System (EPS), responsible of providing the power to the satellite and managing the energy harvest from the solar panels, storing it in batteries and regulating the power necessary to supply the satellite subsystems.

- The **Communications Processor Board (COM)**, cooperating with the OBC subsystem, is responsible for the satellite communication stack handling and for the satellite data storage, when the spacecraft is in its normal operational mode. In case of OBC failure, the COM subsystem assumes the aforementioned C&DH functionality but not ADCS one, becoming the satellite house-keeper<sup>4</sup> in a backup operational mode.

- The ADS-B Payload, being the only scientific payload subsystem, is responsible for receiving the ADS-B signals broadcasted by commercial aircraft and translate them into ADS-B messages to be downloaded to Earth when possible, being connected to the ADS-B antenna.

All these subsystems are being developed and produced by the ISTnanosat team, being the ISTsat-1 cubesat in the *Test Your Satellite!* phase that will last until December 2019 [1]. In Figure 2.4 is shown an overview of the ISTsat-1 architecture and the stacking layout of its subsystems.

Figure 2.4: ISTsat-1 architecture (left) and subsystem stacking layout (right).

# 2.4 Space radiation environment

Unlike the protected environment in the Earth's atmosphere, the space environment stresses spacecraft components with many hazardous types of cosmic radiation. This radiation may come from a variety of emission sources in the solar system, like the Galactic Cosmic Rays and the Sun radiation. The former are mainly composed of energetic protons and heavier ions with around 2 % of electrons and positrons, with a relative constant presence over time. The latter is composed mostly of low energy particles like protons, being also known as solar wind [8].

<sup>&</sup>lt;sup>4</sup>The satellite housekeeper subsystems is responsible for the operation of the satellite and, consequently, the operation of the remaining subsystems.

Within space applications, these radiation types can damage electronic components in a satellite. Total Ionising Dose (TID) and Single Event Effects (SEE) are two ways of characterising the impact of this radiation. The TID is measured as the cumulative radiation received by the spacecraft, mostly due to electrons and protons. Some consequences of long term exposure to radiation are the increase of device leakage and power consumption, shifts in component thresholds and clock changes, making the device work out of its specifications or even cease its operation [8].

A Single Event Effect results from high energy particles like cosmic rays and high energy protons that hit the spacecraft electronic components. These disturbances, which result from the ionisation caused by these particles, are considered as *destructive* (D), if a device function is interrupted or permanently damaged, and *non-destructive* (ND), if the state of a device is momentarily changed with no affect to its functionality [8], [9]. A brief description of the most important SEEs is shown in Table 2.1, with the components affected in each case.

Table 2.1: Description of the main Single Event Effects that affect a spacecraft [adapted from [9]].

| Single Event Effect                  | D/ND                                     | Affected Components                                                         | Description                                                                                                   |  |

|--------------------------------------|------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| Single Event Upset                   | ND                                       | Memories<br>Latches in logic devices                                        | Corruption of the information stored in a memory element.                                                     |  |

| Multiple Bit Upset                   | ND                                       | Memories<br>Latches in logic devices                                        | Several memory elements corrupted by a single strike.                                                         |  |

| Single Event Functional<br>Interrupt | ND                                       | State Machines<br>Control Sections                                          | Complex devices with built-in corruption of a data path leading to temporal loss of the device functionality. |  |

| Single Event Transient               | ND                                       | Analog and Mixed<br>Signal circuits                                         | Impulse response on external/internal signals of certain amplitude and duration.                              |  |

| Single Event Disturb                 | ND                                       | Combinational logic<br>Latches in logic devices                             | Momentary corruption of the information stored in a bit.                                                      |  |

| Single Event Latchup                 | D                                        | CMOS<br>BiCMOS devices                                                      | High-current conditions due to short circuits.                                                                |  |

| Single Event Snapback                | Single Event Snapback D N-channel SOI do |                                                                             | High-current conditions due to short circuits.                                                                |  |

| Single Event Burnout                 | Single Event Burnout D N-chann           |                                                                             | Destructive burnout due to high-current conditions.                                                           |  |

| Single Event Gate<br>Rupture         | D                                        | Power MOSFET<br>Non-volatile NMOS                                           | Rupture of gate dielectric due to high electrical field conditions.                                           |  |

| Single Hard Error                    | D                                        | Memories Latches in logic devices Unalterable change of state in a element. |                                                                                                               |  |

## 2.4.1 Radiation mitigation

Radiation mitigation is important in the design of space satellites to reduce the severity of the radiation effects into the satellite electronics. Therefore, due to the aforementioned effects, space missions require satellite developers to implement radiation mitigation techniques in their designs.

Although many satellite designers use commercial off-the-shelf (COTS) devices as easy ready-made and sale-available components to build their custom cubesats, this low cost option may not be viable in terms of radiation mitigation since these components are not designed to withstand the space radiation environment. However, some component vendors also provide radiation hardened devices with the same functionalities, although these devices bring an impact not only to the cost budget of the spacecraft, as they are more expensive, but also to the mass budget and system design, as these components are usually bigger and heavier. However, using radiation hardened components is not the only measure taken into account in the satellite radiation mitigation. According to [6], additional measures are:

- The use of monitor circuits like a Watchdog Timer (WDT), which is used to check the state of a processing unit. This device resets the processor if its timer is not reset periodically after becoming non-operational due to a SEE. Although most microcontrollers have a WDT, using an external integrated circuit with the same functionality is also a good practice, as a redundant measure.

- The use of **overcurrent protections** that detect and reset components or the whole subsystem before an high current, caused mainly by Single Event Latchups, causes permanent damage.

- **Powering off** some modules within a subsystem separately when these are not required, as many components are more prone to radiation effects when powered on.

- The use of **communication protections** in peripherals like I<sup>2</sup>C to prevent hazardous situations when an individual device locks up the communication bus after a SEE or a software glitch. Here, a master controller can monitor and reset the device to restore the bus for all the subsystems. The decouple of both clock and data lines from the main bus is another viable solution, so that each subsystem may isolate its bus from the main bus in a hazardous situation.

Although the aforementioned implementations may also seem important for non-space electronic circuitry, these mitigation techniques are mandatory in a space-based system to increase its robust-ness and making it fail-proof even in a radiation environment, since the cost and technology used in an in-orbit satellite repair easily outnumbers the cost of the satellite itself, specially in low-cost small satellites, making the repair itself worthless most of the times. Therefore, a satellite and its subsystems must be prepared to prevent and withstand as many fail-cases as possible during their lifetime.

In this Chapter 2, the main structure and functions existent in satellites were introduced, focusing on the increase of nanosatellites launches in the last years and their correspondent missions. As an example of these small satellites, a description of the ISTsat-1 cubesat is done, which supports the development of this master thesis. Additionally, a description of the space radiation environment was done with the most significant radiation effects that may harm a satellite, specially small satellites like cubesats. To prevent a subsystem level failure, some radiation mitigation techniques are detailed, whose implementation is crucial in the electronics design of the several subsystems.

# **Chapter 3**

# State of the Art

In Chapter 2, the main functionalities existent in satellites are introduced. Concerning the objectives of this master thesis described in Section 1.2, three of these functionalities prevail, which may take part of the Communications Processor Board in the ISTnanosat nanosatellites:

- The satellite communications.

- The command and data handling:

- The attitude determination and control.

As the COM subsystems designed throughout this master thesis must only process the communication stack transferred between the satellite and the Ground Segment, the design of a radio transceiver used for the communication with the Ground Segment is done in another communication subsystem like a TT&C. The communication stack is then transferred between this subsystem and the COM using a dedicated serial communication interface and protocol defined by the ISTnanosat team. Therefore, the COM subsystem must only process and transfer between the TT&C the protocols inherent to the communication stack. Nevertheless, a brief analysis of communication systems used in nanosatellites is done in this Chapter 3, along with both C&DH and ADCS modules, since their functionalities are also considered for the subsystems designed in this master thesis, specially for the COMv2.

Due to the small form factor imposed by the cubesat standard, these three functionalities are hard to be implemented in a single subsystem, being commonly divided into two separated subsystems: one focused on the satellite communications and the other dedicated to the C&DH and ADCS, being called as an On-Board Computer module. The latter module requires a high power processing and memory units along with determination and control modules for the satellite attitude. Nevertheless, another commercial solutions may separate these functionalities into three correspondent subsystems. Due to this ambiguity, a study regarding different combinations of subsystems that combine these functionalities is done, considering commercial systems developed by companies well-known in the cubesat market. Finally, a comparison between these combined solutions is done, with their pros and cons.

## 3.1 Communication Systems

The communication system is an essential part of a satellite that enables the transmission of both telemetry and payload data to the Ground Segment, while receiving commands from these stations. The communication between Earth and a satellite is commonly based in the radio frequency spectrum, using frequencies from 30 MHz up to 40 GHz, as shown in Figure 3.1. Additionally, laser based optical communications are also used, which are not considered in the current state of the art.

Figure 3.1: Radio frequency spectrum used for satellite communications [adapted from [6]].

Nowadays, many nanosatellites resort to radio frequencies in the VHF and UHF bands to communicate, as many communication modules based on these bands already have flight heritage. However, the use of higher frequency bands in small satellites has been increasing in the past years, with frequencies up to the Ka-band, enabling the use of higher bandwidths and resultant higher data rates [6].

Although the use of nanosatellites is being considered for deep space missions in the future, these satellites still have not been launched to orbits beyond the LEO. Therefore, small satellites launched to these orbits mainly use low gain antennas, like whip or patch antennas, for their communication systems, taking advantage of the short orbit distance. Due to their monopole antenna polarisation, these antennas can also maintain a communication link even when the spacecraft is tumbling, which is also an advantage for nanosatellites that commonly do not have an accurate attitude control. While whip antennas are commonly used for VHF and UHF communications, small patch antennas are used from UHF up to S-bands [6].

Another development that is improving radio frequency based communication systems used in small satellites is the implementation of a Software Defined Radio (SDR). This device is usually based on Field Programmable Gate Array (FPGA) hardware that offers great flexibility, allowing the use of multiple radio frequency bands with different filtering and modulation schemes without hardware changes. Furthermore, since the radio configuration is mostly based on software, the correspondent changes can be done during flight by uploading new software from the Ground Segment, improving the modularity of the communications system. As SDRs are becoming increasingly small and power efficient, their use is also becoming a trend in nanosatellites like cubesats [6].

## 3.2 Command and Data Handling

Like in any other embedded system, a satellite must rely at least on one system that controls its operation, managing its features and other secondary subsystems, in order to meet its requirements and correct operation. In a cubesat, the main objective of a Command and Data Handling (C&DH) module is to manage and control the other subsystems in the satellite and manage the storage of relevant data to be sent to the Ground Segment. Additionally, this module can also process this data into a well-defined communication protocol stack before sending it to the GS through the satellite transceiver. On the opposite radio link direction, this subsystem may also process the data received from the GS. Therefore, being the satellite main controller, the C&DH subsystem requires high power processing and storage capabilities, being commonly designed with a high power processing unit plus a memory unit to ensure that the data storage of the satellite is not compromised.

#### 3.2.1 High power processing units

Among the recently cubesat implementations, the use of low power microcontrollers and FPGAs can be seen, supporting different processor cores. Nowadays FPGAs provide high levels of integration in small satellite implementations, supplying peripherals, on-chip memories and having an improved performance with low power consumptions. These processing units built a successfull legacy in space as they became one choice on the on-board computing needed in cubesat subsystems [6].

On the other hand, the use of processor-based microcontrollers, like the ARM or the MSP430 product lines, is a trend in cubesats, as they offer a low power solution with fast code executions and the typical on-chip peripherals that are used for the serial communication between the several subsystems within the satellite, like the Controller Area Network (CAN), as well as the Inter-Integrated Circuit (I<sup>2</sup>C) interfaces and the Serial Peripheral Interface (SPI). Another feature considered by cubesat developers are microcontrollers that integrate internal memory, which can be programmed more easily [6]. In Section 3.4 a detailed study is done regarding the performance and power efficiency of microcontrollers used in C&DH modules, which are developed by cubesat specialised manufacturers and that have successfully flown in space missions, becoming modules with flight heritage.

### 3.2.2 Memory unit components

Regarding the selection of memory components to be used in cubesats, many different technology types are available due to their wide ranges, typically starting at 32 kB. However, the main requirement of memory units for satellite systems is reliability, which can be achieved with different types of memory and with different costs, depending on their purpose. Nowadays, the most used memory technologies are the Static Random Access Memory (SRAM) and the Dynamic Random Access Memory (DRAM) for

volatile memory data, and the Flash memory, the Magnetoresistive Random Access Memory (MRAM) and the Ferro-electric Random Access Memory (FeRAM) for persistent memory data. A comparison of these memory types and their performances is shown in Table 3.1.

Table 3.1: Comparison of different memory technologies [adapted from [6]].

| Feature                 | SRAM      | DRAM       | Flash                  | MRAM                    | FeRAM                   |

|-------------------------|-----------|------------|------------------------|-------------------------|-------------------------|

| Volatile                | Yes       | Yes        | No                     | No                      | No                      |

| Data Retention          | None      | None       | >10 years              | >10 years               | >10 years               |

| Write/Read Cycles       | Unlimited | Unlimited  | 10 <sup>6</sup> cycles | 10 <sup>13</sup> cycles | 10 <sup>13</sup> cycles |

| Radiation (TID)         | 1 Mrad    | 50 krad    | 30 krad                | 1 Mrad                  | 1 Mrad                  |

| Single event upset rate | Low       | High       | Low-med                | Nil                     | Nil                     |

| Temperature Range       | Military  | Industrial | Commercial             | Military                | Military                |

| Power                   | 500 mW    | 300 mW     | 30 mW                  | 900 mW                  | 270 mW                  |

| Package                 | 4 MB      | 128 MB     | 128-256 MB             | 1 MB                    | 1.5 MB                  |

| Price                   | Medium    | Medium     | Low                    | High                    | High                    |

For cubesat missions, which usually last no more than 5 years due to their low orbit, factors like the retention time of a memory and its data operation cycles are of low importance. However, the radiation effects on these electronic components are of great importance as they can cease their normal operation, as explained in Section 2.4. Therefore, the selection of memory units must be taken into consideration regarding these factors. Like in any other satellite, the power consumption is another important factor to be considered due to the reduced energy harvesting in small satellites like cubesats.

# 3.3 Attitude Determination and Control System

Depending on its mission, a satellite is placed into a specific orbit. However, its position can deviate from this orbit commonly due to perturbations like the solar radiation pressure, the interaction of the Earth magnetic field and gravity gradient, and the atmospheric drag. These factors also affect cubesats that orbit at Low Earth Orbits.

The main objective of the Attitude Determination and Control System (ADCS) module is to monitor and act in the satellite attitude, positioning it constantly in its orbit and, therefore, minimising the aforementioned perturbations. The correct attitude of a satellite depends on its status and purpose at a specific time, as a satellite can move itself in orbit. For example, a different positioning may be recommended when radio transmissions are being done to Earth rather than when the satellite is harvesting energy from the sun. Therefore, depending on the situation and objective, an ADCS module can be in one of the following modes, which are normally executed in a specific sequence depending of each spacecraft [10]:

- Detumbling The system measures the speed of rotation and acts on the satellite to reduce it. As

the angular momentum is reduced, the determination algorithm can successfully work.

- Target Pointing The satellite focuses on a specific point on the Earth's surface, even with the change of its orbit position.

- Manoeuvring or Nadir Pointing Normal operating mode. The system points the satellite to the spherical centre of the Earth, also known as Earth nadir point.

- Stabilisation or Inertial Pointing The satellite is oriented so that its attitude becomes stabilised to, for example, harvest energy from the Sun by pointing the solar panels directly to it.

- **Desaturation** As the satellite magnetic sensors and actuators reach their saturation and become unreliable for operation, a magnetic field is forced to overcome this effect and desaturate them.

- Offline The satellite orientation correction system is switched off, having no attitude control to save energy.

Figure 3.2: Different orientation modes during the satellite attitude determination and control<sup>1</sup>.

Allied to these orientation modes, several stabilisation techniques are used, also depending on the satellite mission and its requirements [10]:

- Gravity Gradient The satellite releases a spherical mass connected by a cable and, due to the Newton's law of universal gravitation, the closest mass to Earth will be more attracted and the satellite will line up with the Earth nadir point.

- Magnetic Controllable inductors are used to create magnetic fields that will interact with the Earth's magnetic field.

- **Rotational** The satellite is rotated on a single axis with a fixed angular momentum vector, making the satellite more resistant to external disturbances.

- **Double rotational** Using two different angular speeds on the same axis, one is in favour of the angular momentum and the other is against it, stabilising the on-board instruments.

- Bias Momentum With a reaction wheel<sup>2</sup> aligned with an axis, a speed change of that wheel provides a satellite rotation variation in this axis and in the opposite direction, based on Newton's

http://www.kleinsatelliten.de/flying\_laptop/systeme/lageregelung.en.html - Adapted on 17/02/2018.

<sup>&</sup>lt;sup>2</sup>A reaction wheel is a type of flywheel used by spacecraft for three axis attitude control that does not require external torque.

Third Law.

Momentum Cancellation - With reaction wheels in the three axes of the spacecraft, these are

accelerated slowly in the same direction of the external perturbation until they reach their maximum

speed. Then, with other actuators, the desaturation of these wheels is done.

Among these stabilisation techniques, the accuracy of passive control systems like the gravitational and magnetic gradients is lower than the other active systems, being only an option to consider when the satellite resources are limited, like in a cubesat. However, momentum cancellation is the most used technique because it allows to manoeuvre all three axes of the satellite with 1° of precision [10].

As the name implies, an Attitude Determination and Control System module can be divided into two groups with different functionalities:

- Attitude Determination, which relies on sensors to check the satellite position.

- Attitude Control, which relies on actuators to intentionally manipulate the satellite, achieving the

desired attitude.

The interconnection between these two groups is done using a processing unit, which collects the data from the sensors through an electronic interface, processes and stores it. After that, the necessary corrections to the satellite attitude are calculated and sent to the actuator drivers.

## 3.3.1 ADCS sensors

A set of sensors is a major requirement in the spacecraft attitude determination, obtaining continuously accurate angular velocities of the satellite and their correspondent variations. Among the existent sensors, two types prevail: the reference sensors, which provide a value against a reference, like the direction of the sun, and the inertial sensors, which provide continuous attitude readings. To improve the performance and redundancy of the system, the two types are usually used together, having implications on the cost, energy consumption and mass of the spacecraft. However, the information processing of both sensor types when working together is essential to create a system that obtains reliable data for the satellite control [10].

The technology of sensor components has evolved significantly over the last years, making electronic devices more reliable and with less size and becoming available in microelectromechanical systems (MEMS) devices. Some sensors used in the satellite orientation are shown in Table 3.2, as well as their purpose, accuracy, advantages and disadvantages.

Among these sensors, the star orientation using a camera is the most accurate method, although it requires a complex processing power to determine the satellite position. Although MEMS magnetometers and gyroscopes are less accurate than other sensors, they are viable options for small satellites due to their size and reduced cost. Moreover, because the gyroscope accuracy changes with its running

**Table 3.2:** Comparison of different attitude sensors [adapted from [10]].

| Sensor                    | Accuracy<br>[°] | Axis  | Pros                                      | Cons                               | Brief Definition                                                                          |

|---------------------------|-----------------|-------|-------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------|

| Sun Sensor                | 0.1             | 2     | Reduced cost,<br>Simple,<br>Viable        | Unusable in solar eclipse          | Determines the satellite position relative to the Sun.                                    |

| Camera<br>(star-oriented) | 0.001           | 3     | High accuracy,<br>Absolute<br>positioning | Cost,<br>High mass,<br>Complex use | Uses an internal database and compares it with the observed stars.                        |

| Magnetometer (MEMS)       | 0.5 - 5         | 1 - 3 | Reduced cost,<br>Compact                  | Only for<br>LEO                    | Measures the Earth's magnetic field intensity.                                            |

| Gyroscope<br>(MEMS)       | 0.01/hour       | 3     | Accuracy                                  | Cost,<br>Changeable<br>accuracy    | Expresses the angular changes suffered by the satellite.                                  |

| GPS                       | 0.1 - 1         | -     | Easy to use,<br>Absolute<br>positioning   | Licensed                           | Determines the exact position of the satellite with information sent by other satellites. |

time, and because accelerometers and magnetometers require gravitational and magnetic fields, they can only work in LEO, where these fields are reasonably felt. Finally, the simplest way to get the absolute position of a satellite is using a GPS, but it requires a license for altitudes higher than 18 km.

#### 3.3.2 ADCS actuators

Similarly to the attitude determination, the satellite attitude control requires a set of actuators to control and impose forces to it. The power consumption, size and lifetime of a satellite are important factors to take into account when choosing actuators, as the attitude control of a small satellite is usually done with a single actuator due to these factors, unlike the attitude determination which may use different sensors.

Each actuator is designed to compensate a specific effect, being divided into inertial actuators that generate torques to modify the angular momentum of the spacecraft, and non-inertial actuators that use favourable external disturbances to achieve the desired attitude control [10]. Table 3.3 lists some of the actuators that can be used in satellites, along with their advantages and disadvantages, range of action and a brief description.

**Table 3.3:** Comparison of different attitude actuators [adapted from [10]].

| Actuator             | Range                                   | Pros                         | Cons                | Brief Definition                                                  |

|----------------------|-----------------------------------------|------------------------------|---------------------|-------------------------------------------------------------------|

| Gas<br>Propulsion    | 0.1 – 5 N (cold)<br>0.5 – 9 000 N (hot) | High accuracy,<br>High range | Size<br>Ceasing Gas | Release of a gas generating a reaction force from the satellite.  |

| Magnetic<br>Inductor | 10 μNm – 0.04 Nm                        | Low mass,<br>No mobile parts | Only in LEO         | Creates a magnetic field that interacts with an external field.   |

| Reaction<br>Wheel    | 0.001 – 1 Nm                            | High precision               | Size, cost          | The speed of rotation changes the torque created on a given axis. |

## 3.4 Commercial OBC and communication modules for cubesats

In this Section 3.4, some combinations of both communication and On-Board Computer solutions developed by specialised companies are shown, which are built for cubesat integration. These systems may implement the previously described functionalities, focusing separately or together on communications, C&DH or ADCS purposes. Therefore, factors like the communication frequency band and bandwidths/data rates, the architecture of the processing and memory units, the availability of sensors and actuators and the power consumption are detailed. Please note that the presented combinations are not the only ones available in the market, as other products and companies exist.

#### GOMspace Software Defined Radio - NanoMind Z7000 and NanoCom TR-600

Being one of the trending companies in the small satellite market, GOMspace designs many different subsystems to be integrated in cubesats. One of them is its integrated SDR composed of two main systems that are interconnected through a docking board following the cubesat standard.

The first system is the *NanoMind Z7000* shown in Figure 3.3, being a high processing power module with flight heritage used for communication and signal and image processing systems. This module has an efficient system-on-a-chip (SoC) with the software programmability of a dual core 800 MHz ARM processor, capable of running a Linux operating system, plus the hardware programmability of an FPGA. For storage, 1 GB of DDR3 RAM and 32 GB of eMMC storage are used. As this product is built to work as a SDR, it does not feature ADCS modules. Regarding its serial communication peripherals, this module can communicate through USB, SPI, I<sup>2</sup>C, UART and CAN interfaces. According to its datasheet information, the power consumption of this module is 2.3 W with a 3.3 V power supply [11].

Connected to this module is the *NanoCom TR-600*, also shown in Figure 3.3. This communication module is based on an Analog Devices AD9361 transceiver operating from 70 MHz up to 6 GHz, capable of providing a bandwidth from 200 kHz up to 56 MHz with its integrated 12-bit DACs and ADCs. According to its datasheet information, the maximum current consumption rated for this module is 4.0 A with a 3.6 V power supply [11].

Figure 3.3: NanoMind Z7000 (left), NanoCom TR600 (centre) and NanoDock SDR (right) [adapted from [11]].

Both modules do not comply with the cubesat standard due to their miniaturised form-factor, requiring the use of a docking board like the *NanoDock SDR* shown in Figure 3.3 for cubesat compatibility, being pluggable modules.

#### GOMspace OBC and V/U communications module - NanoMind A3200 and NanoCom AX100

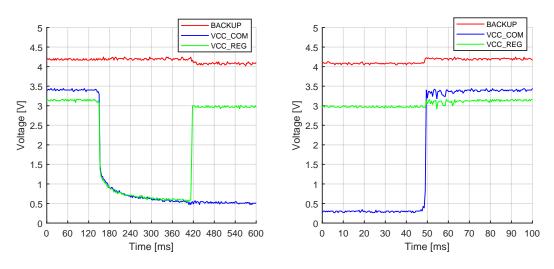

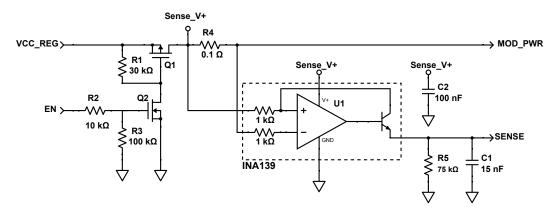

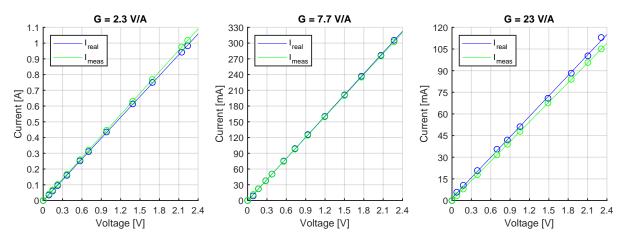

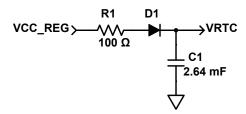

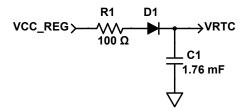

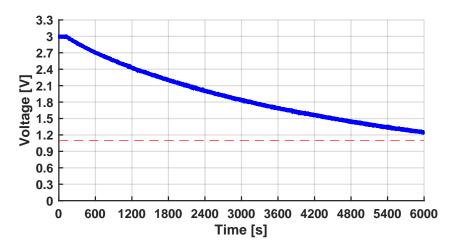

Another integrated option designed by GOMspace is the association of its OBC module with a V/U communication module, again interconnected through a docking board following the cubesat standard.