## Integrated Eddy Current based Non-destructive Testing System for High-end Applications

A Capacitively Coupled Chopper Instrumentation Amplifier

## João Gonçalo Neto Silva

## Thesis to obtain the Master of Science Degree in Electrical and Computer Engineering

Supervisor(s): Professor Jorge Manuel dos Santos Ribeiro Fernandes Eng. Diogo Miguel Bárbara Coroas Prista Caetano

## **Examination Committee**

Chairperson: Professor Gonçalo Nuno Gomes Tavares Supervisor: Professor Jorge Manuel dos Santos Ribeiro Fernandes Member of the Committee: Professor Marcelino Bicho dos Santos

### November 2016

## Acknowledgments

First of all, I'd like to thank Prof. Jorge Fernandes for all the support, for all the help and contributions given to this work and for all the great discussions during coffee breaks. To Diogo Caetano, my sincere thanks for the tireless help, guidance and great contributions that allowed me to conclude this thesis and this very important milestone of my life. I'd also like to thank to all the work team at INESC-ID for all the laughter and funny moments, for all the tips and shared knowledge.

I could not forget all friends I made during these 5 years at Instituto Superior Técnico, friends that will stay for life. I also thank my family for never doubting me, to push me forward and to allow me to get to where I am today. To my grandparents, António and Celeste, for providing me the best moments of my life and for making me the person I am today, thank you very much. I can not forget my childhood friends, that since my early days have always been by my side.

# Abstract

This work addresses an Eddy-Current (EC) Non-Destructive Testing (NDT) system that makes use of Magneto-Resistive (MR) sensors to characterize metallic samples under test. A system with MR sensors can work with low-frequency magnetic signals to allow higher penetration depths. The resultant signals are processed by an Application Specific Integrated Circuit (ASIC), that includes a pre-amplifier, which is the focus of this work.

The pre-amplifier presents a very significant flicker noise contribution that impairs measurements. To reduce flicker noise, Chopper Stabilization is implemented. The pre-amplifier has a Folded Cascode topology and implements a capacitive feedback, which allows superior gain precision, when compared with resistive feedback configurations.

The action of chopper modulators results in the modulation of input DC components that are not blocked by the input capacitors. When amplified, these DC components can cause the saturation of the pre-amplifier. For this reason, a DC Servo Loop (DSL) is added, as it extracts the output DC component and, by means of negative feedback, subtracts it from the amplifier input, achieving its cancellation.

The pre-amplifier was designed in AMS 0.35  $\mu$ m CMOS technology and has a simulated gain of 20 dB, while presenting an Input-Referred Noise (IRN) of 6  $nV/\sqrt{Hz}$  at 100 Hz and noise floor of 4  $nV/\sqrt{Hz}$ . The pre-amplifier also presents an attenuation of 60 dB for the DC signals, allowing the attenuation of DC components up to 200 mV.

## Keywords

Non-destructive Testing, Folded Cascode Pre-Amplifier, Capacitive Feedback, Flicker Noise, Chopper Stabilization, DC Suppression

## Resumo

O presente trabalho foca um sistema de Testes Não Destrutivos baseado em Correntes de Foucault, que utiliza sensores Magneto-resistivos (MR) para caracterizar amostras metálicas sob teste. Um sistema com sensores MR pode funcionar com sinais magnéticos de baixa frequência para permitir maiores profundidades de penetração. Os sinais resultantes são processados por um *Application Specific Integrated Circuit* (ASIC), que inclui um pré-amplificador, que constitui o foco deste trabalho.

O pré-amplificador apresenta uma contribuição de ruído de *flicker* bastante significativa que corrompe as medições. Para reduzir o ruído de *flicker*, *Chopper Stabilization* é implementado. O pré-amplificador tem uma topologia *Folded Cascode* e implementa um *feedback* capacitivo que permite uma precisão de ganho superior, aquando comparado com uma configuração de *feedback* resistivo.

A acção dos moduladores de *chopper* resulta na modulação das componentes DC de entrada que não são bloqueadas pelos respectivos condensadores. Quando amplificadas, estas componentes podem causar a saturação do pré-amplificador. Por esta razão, o *DC Servo Loop* (DSL) é adicionado, já que este extrai a componente DC de saída e, através de um *feedback* negativo, subtrai-a da entrada do pré-amplificador, atingindo assim o seu cancelamento.

O pré-amplificador foi projectado numa tecnologia AMS 0.35  $\mu$ m CMOS e possui um ganho simulado de 20 dB, enquanto demonstra um IRN de 6  $nV/\sqrt{Hz}$  a 100 Hz e um patamar de ruído de 4  $nV/\sqrt{Hz}$ . O pré-amplificador apresenta ainda uma atenuação de 60 dB para sinais DC, permitindo a atenuação destas componentes DC até 200 mV.

## **Palavras Chave**

Testes Não Destrutivos, Pré-Amplificador *Folded Cascode*, *Feedback* Capacitivo, Ruído de *Flicker, Chopper Stabilization*, Supressão de DC

# Contents

| 1 | Intro | oduction                                                                | 1  |

|---|-------|-------------------------------------------------------------------------|----|

|   | 1.1   | Motivation                                                              | 2  |

|   | 1.2   | Objectives                                                              | 2  |

|   | 1.3   | Main contributions                                                      | 3  |

|   | 1.4   | Dissertation outline                                                    | 3  |

| 2 | Stat  | te-of-the-art                                                           | 5  |

|   | 2.1   | Introduction                                                            | 6  |

|   | 2.2   | Eddy-current Non-destructive Testing System                             | 6  |

|   | 2.3   | Noise Analysis                                                          | 9  |

|   |       | 2.3.1 Noise in MOSFET Transistors and Single Stage Amplifiers           | 9  |

|   |       | 2.3.2 Noise in Operational Transconductance Amplifiers                  | 2  |

|   | 2.4   | Flicker Noise Suppression    1                                          | 6  |

|   |       | 2.4.1 Autozero                                                          | 6  |

|   |       | 2.4.2 Chopper Stabilization                                             | 7  |

|   | 2.5   | Fully-differential Amplifiers and Common-mode Feedback                  | 24 |

|   | 2.6   | DC Suppression                                                          | 29 |

|   | 2.7   | Summary                                                                 | 32 |

| 3 | Sys   | tem Overview and Pre-amplifier Implementation 3                         | 85 |

|   | 3.1   | Introduction                                                            | 86 |

|   | 3.2   | The ASIC                                                                | 86 |

|   |       | 3.2.1 Current Source and Sensor Addressing                              | 37 |

|   |       | 3.2.2 Cancellation Block                                                | 88 |

|   | 3.3   | Pre-amplifier and Typical Chopper Implementations                       | 39 |

|   |       | 3.3.1 Characterization of the Amplifiers                                | 10 |

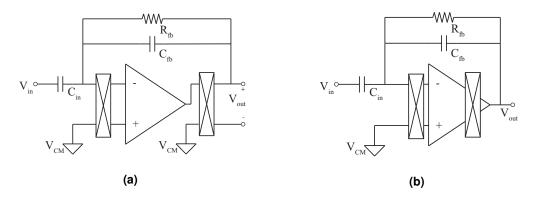

|   |       | 3.3.2 Typical Chopper Stabilization Implementation                      | 12 |

|   | 3.4   | Capacitively Coupled Chopper Instrumentation Amplifier                  | 15 |

|   |       | 3.4.1 Feedback Configuration                                            | 16 |

|   |       | 3.4.2 Single-ended to Fully-differential Conversion of the Amplifiers 4 | 8  |

|   |     | 3.4.3 Fully-differential Amplifiers Comparison         | 53 |

|---|-----|--------------------------------------------------------|----|

|   | 3.5 | DC Servo Loop                                          | 54 |

|   | 3.6 | Summary                                                | 57 |

| 4 | Res | ults                                                   | 59 |

|   | 4.1 |                                                        | 60 |

|   | 4.2 | Amplifier Comparison                                   | 60 |

|   | 4.3 | Capacitively Coupled Chopper Instrumentation Amplifier | 63 |

|   |     | 4.3.1 CCCIA Characterization                           | 63 |

|   |     | 4.3.2 The DC Servo Loop                                | 65 |

|   | 4.4 | Monte Carlo Simulations                                | 70 |

|   | 4.5 | Circuit Layout                                         | 72 |

|   | 4.6 | Summary                                                | 74 |

| 5 | Con | clusions                                               | 75 |

# **List of Figures**

| 2.1  | Eddy current NDT illustration.                                                          | 6  |

|------|-----------------------------------------------------------------------------------------|----|

| 2.2  | System characteristics: (a) excitation frequency for several materials and depths;      |    |

|      | (b) signal bandwidth for several scanning speeds and depths                             | 8  |

| 2.3  | Top-level diagram of the system.                                                        | 8  |

| 2.4  | MOS noise models: (a) as a current source; (b) as a voltage source                      | 9  |

| 2.5  | Common-source stage noise: (a) without noise sources; (b) with noise sources.           | 10 |

| 2.6  | Cascode stage noise: (a) Cascode stage; (b) Noise modeled by voltage source.            | 11 |

| 2.7  | A differential pair: (a) without noise sources; (b) with noise sources.                 | 12 |

| 2.8  | Telescopic OTA.                                                                         | 13 |

| 2.9  | Mirrored OTA                                                                            | 14 |

| 2.10 | Folded Cascode OTA.                                                                     | 15 |

| 2.11 | Basic Autozero implementation                                                           | 17 |

| 2.12 | Diagram of chopper stabilization.                                                       | 18 |

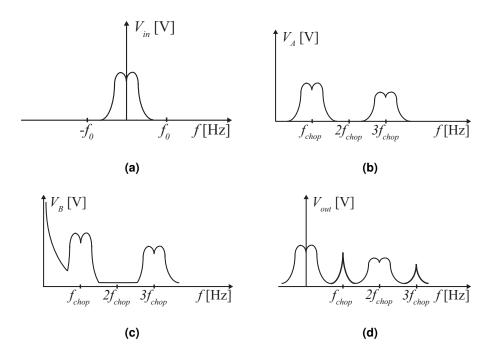

| 2.13 | Signals along the Chopper Stabilization circuit diagram (Figure 2.12): (a) $V_{in}$ and |    |

|      | $V_A$ ; (b) $V_B$ and $V_{out}$                                                         | 18 |

| 2.14 | Spectra of signals at several stages of chopper stabilization process: (a) input sig-   |    |

|      | nal; (b) signal after the first modulation; (c) signal after amplification; (d) output  |    |

|      | signal                                                                                  | 19 |

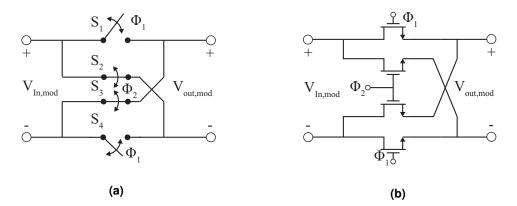

| 2.15 | Representation of a chopper modulator: (a) ideal switches; (b) switches imple-          |    |

|      | mented as NMOS transistors.                                                             | 21 |

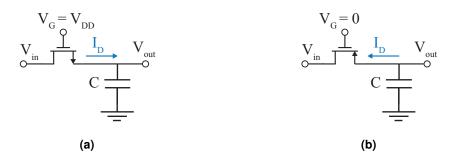

| 2.16 | Circuits for determining the dynamic range of switches: (a) NMOS switch; (b)            |    |

|      | PMOS switch.                                                                            | 22 |

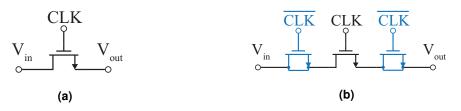

| 2.17 | Modulator switch implemented as a: (a) NMOS transistor; (b) NMOS transistor with        |    |

|      | half-sized dummies.                                                                     | 22 |

| 2.18 | Transmission Gate: (a) circuit; (b) symbol.                                             | 23 |

| 2.19 | "ON" resistance of a NMOS, PMOS and a TG. Both NMOS and PMOS results                    |    |

|      | were simulated for $W/L = 10/0.35$ . The TG results were calculated using data of       |    |

|      | the other two curves                                                                    | 23 |

| 2.20 | TG with half-sized dummy transistors.                                                   | 24 |

| 2.21 | Example of: a) an inverting fully-differential amplifier with resistive feedback; b)   |    |

|------|----------------------------------------------------------------------------------------|----|

|      | transistor level implementation of the amplifier.                                      | 24 |

| 2.22 | Fully-differential amplifier with CM noise                                             | 25 |

| 2.23 | Small-signal model of a fully-differential amplifier: (a) open-loop configuration; (b) |    |

|      | close-loop configuration                                                               | 26 |

| 2.24 | CMFB: (a) the top-level diagram; (b) the main amplifier circuit.                       | 27 |

| 2.25 | A CMFB scheme: (a) complete circuit; (b) the amplifier.                                | 28 |

| 2.26 | A top-level CMFB diagram.                                                              | 28 |

| 2.27 | Block diagram of a CCCIA.                                                              | 30 |

| 2.28 | The DSL: (a) in the CCCIA; (b) integrator implementation.                              | 30 |

| 2.29 | A VLTC-SC integrator.                                                                  | 32 |

| 2.30 | A pseudo-resistor.                                                                     | 32 |

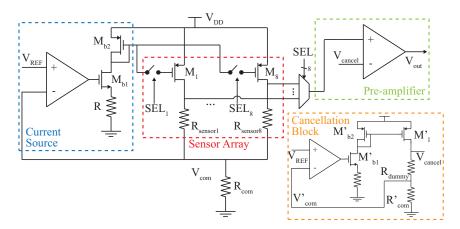

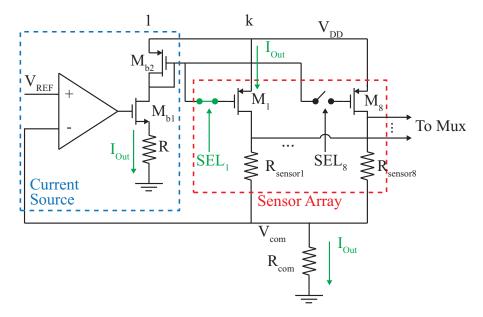

| 3.1  | Full circuit schematic.                                                                | 36 |

| 3.2  | Full circuit schematic.                                                                | 37 |

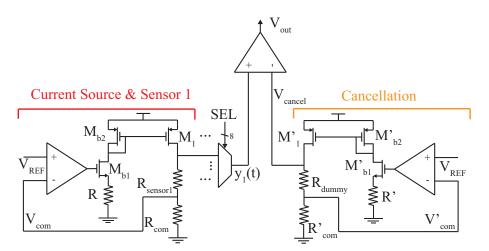

| 3.3  | Cancellation block working principle.                                                  | 39 |

| 3.4  | Pre-amplifier circuit.                                                                 | 40 |

| 3.5  | Pre-amplifier feedback configuration.                                                  | 41 |

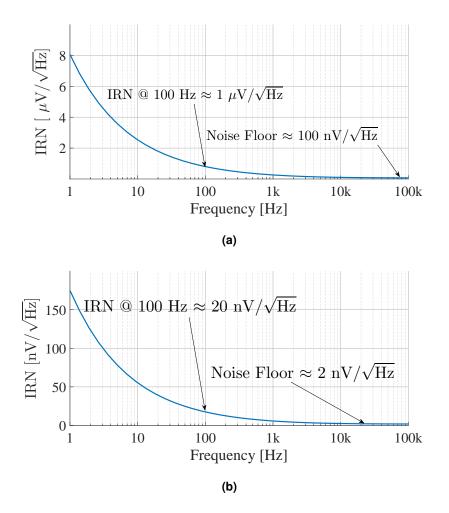

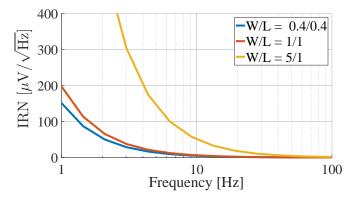

| 3.6  | Pre-amplifier IRN: (a) test amplifier; (b) final amplifier.                            | 42 |

| 3.7  | Implementations of Chopper Stabilization: (a) typical implementation; (b) imple-       |    |

|      | mentation with modulators in the cascode stages of the amplifier.                      | 43 |

| 3.8  | Simulated IRN for the different input modulator transistor area.                       | 44 |

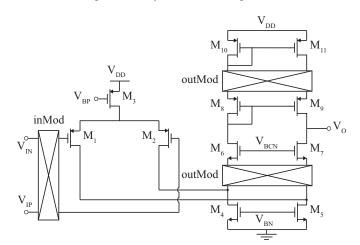

| 3.9  | Schematic of a chopped folded cascode with modulators in the low impedance             |    |

|      | cascode nodes                                                                          | 44 |

| 3.10 | Top-level diagram of the proposed CCCIA                                                | 46 |

| 3.11 | Feedback paths of the CCCIA.                                                           | 46 |

| 3.12 | CCCIA block diagram: signal components along the feedback paths                        | 47 |

| 3.13 | Single-ended to fully-differential conversion.                                         | 49 |

| 3.14 | Biasing circuits: (a) original; (b) added                                              | 50 |

| 3.15 | CMFB circuit implemented.                                                              | 51 |

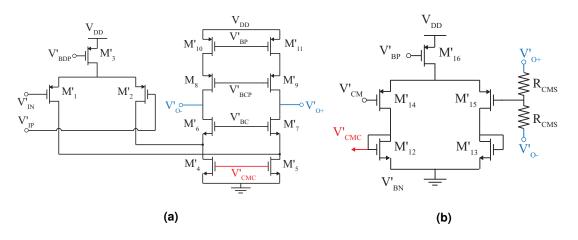

| 3.16 | Test amplifier: (a) folded cascode circuit; (a) CMFB circuit                           | 52 |

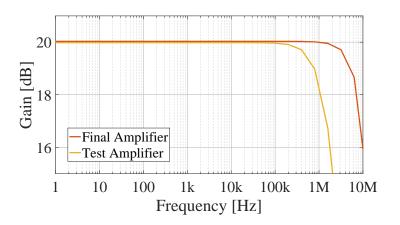

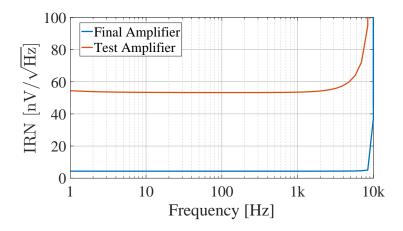

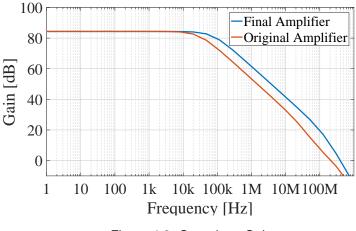

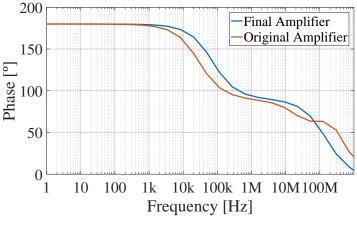

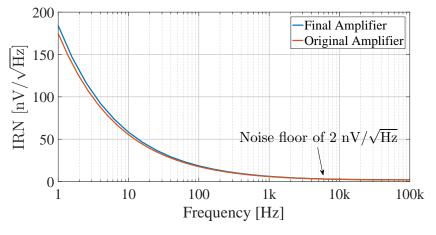

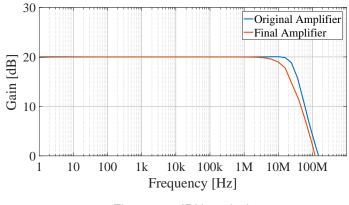

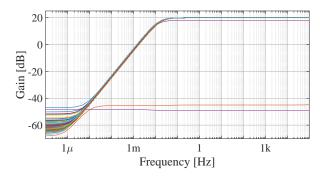

| 3.17 | Gain of the CCCIA with the test and final amplifiers.                                  | 53 |

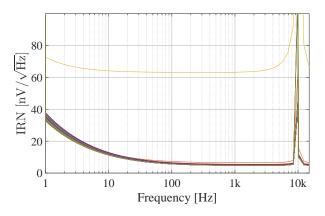

| 3.18 | IRN of the CCCIA with the test and final amplifiers.                                   | 54 |

| 3.19 | Inclusion of the DSL                                                                   | 54 |

| 3.20 | Integrator: (a) schematic; (b) frequency response.                                     | 55 |

| 3.21 | Component frequency matching to achieve DC cancellation                                | 55 |

| 3.22 | Feedback path formed by the DSL                                                        | 56 |

| 4.1  | Feedback configuration used in simulations.                                        | 60 |

|------|------------------------------------------------------------------------------------|----|

| 4.2  | Open-loop Gain.                                                                    | 61 |

| 4.3  | Open-loop phase.                                                                   | 61 |

| 4.4  | IRN analysis.                                                                      | 62 |

| 4.5  | IRN analysis.                                                                      | 62 |

| 4.6  | CCCIA test setup: (a) input signal generation; (b) Circuit of the without the DSL. | 63 |

| 4.7  | Gain and IRN of the CCCIA without the DSL                                          | 64 |

| 4.8  | Inclusion of the DSL in the CCCIA                                                  | 65 |

| 4.9  | Schematic of a fully-differential Miller integrator.                               | 66 |

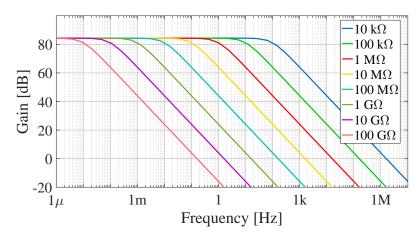

| 4.10 | Variation of the cut-off frequency of the integrator with the input resistance     | 66 |

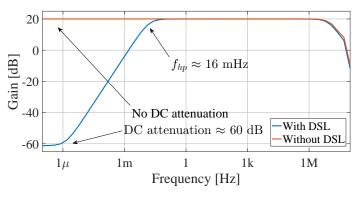

| 4.11 | Gain of the CCCIA with the DSL                                                     | 67 |

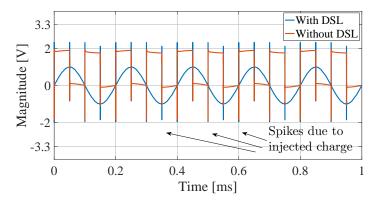

| 4.12 | Transient response the output $V_{out}$ of the CCCIA                               | 68 |

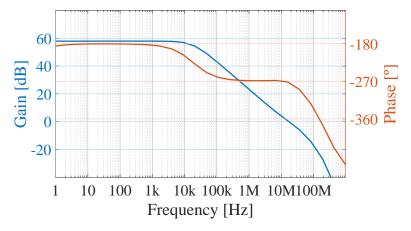

| 4.13 | Stability analysis results: loop gain and phase.                                   | 69 |

| 4.14 | IRN analysis of the CCCIA with the DSL.                                            | 69 |

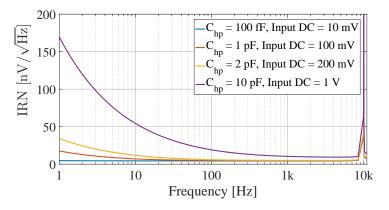

| 4.15 | Impact of the variation of $C_{hp}$ on IRN                                         | 70 |

| 4.16 | Monte Carlo simulations: CCCIA gain                                                | 71 |

| 4.17 | Monte Carlo simulations: IRN of the CCCIA                                          | 71 |

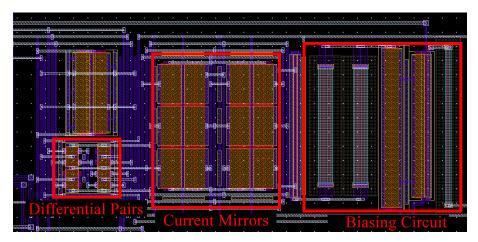

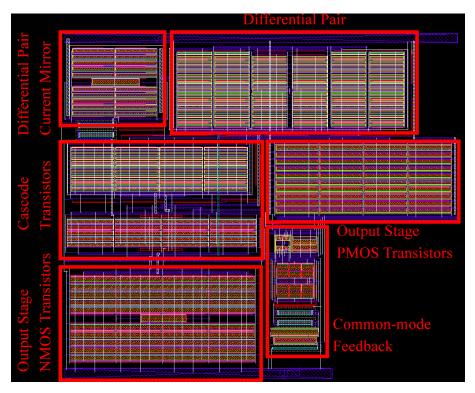

| 4.18 | Layout of the CMFB circuit of the final amplifier                                  | 72 |

| 4.19 | Layout of the final amplifier.                                                     | 72 |

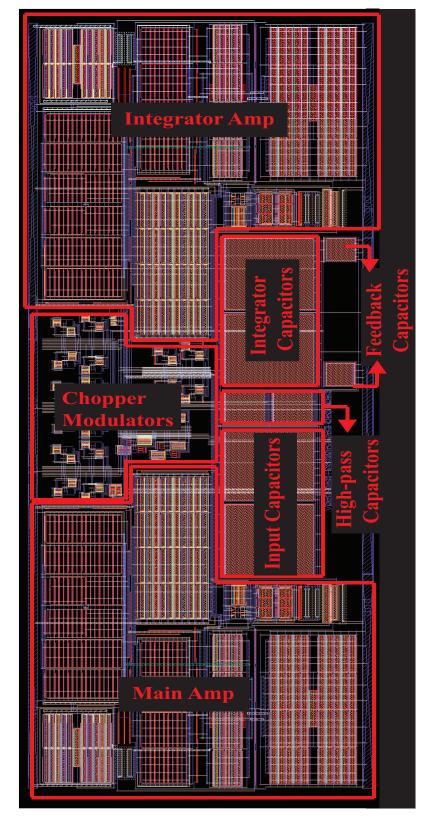

| 4.20 | Layout of the CCCIA                                                                | 73 |

# **List of Tables**

| 1.1 | Circuit Specifications                                           | 3  |

|-----|------------------------------------------------------------------|----|

| 2.1 | OTA comparison.                                                  | 16 |

| 3.1 | Test amplifier's specifications                                  | 40 |

| 3.2 | Final amplifier's specifications.                                | 41 |

| 3.3 | Transistor parameters of the final amplifier.                    | 41 |

| 3.4 | Transistor parameters of the biasing circuit.                    | 50 |

| 3.5 | Transistor parameters of the final fully-differential amplifier. | 52 |

| 3.6 | Transistor parameters of the biasing circuit.                    | 53 |

| 3.7 | DSL dimensioning parameters.                                     | 57 |

| 4.1 | Circuit specifications and results.                              | 74 |

# **List of Acronyms**

AC Alternating Current ADC Analog to Digital Converter ASIC Application Specific Integrated Circuit **CCCIA** Capacitively Couple Chopper Instrumentation Amplifier **CMFB** Common-Mode Feedback **CM** Common-Mode CS Common-Source DAC Digital to Analog Converter **DC** Direct Current **DM** Differential-Mode DSL DC Servo Loop EC Eddy-Current **IRN** Input-Referred Noise MOS Metal-Oxide-Semiconductor MR Magneto-Resistive NDT Non-Destructive Testing NMOS N-type MOS **OTA** Operational Transconductance Amplifier PAC Periodically AC PMOS P-type MOS **PNOISE** Periodically Noise

- **PSD** Power Spectral Density

- PSS Periodically Steady-State

- SC Switched Capacitor

- S&H Sample & Hold

- SNR Signal-to-Noise Ratio

- TG Transmission Gate

VLTC-SC Very Large Time Constant Switched Capacitor

#

# Introduction

#### Contents

| 1.1 | Motivation           |

|-----|----------------------|

| 1.2 | Objectives 2         |

| 1.3 | Main contributions   |

| 1.4 | Dissertation outline |

#### 1.1 Motivation

Nowadays, worldwide industry has been more and more dependent on electronics that provide cheaper, faster and safer ways for production of goods. From designing, to production and testing, society is aided, in the process of creating new products and services, by all kind of electronic devices. The increasing autonomy and processing power of these devices has allowed the development of testing techniques that rely on measuring physical attributes of the manufactured goods without compromising their integrity, that is Non-Destructive Testing (NDT). NDT provides a way to diagnose defects and imperfections on the test subject without compromising its characteristics. This evaluation of the condition of an object can be done via X-ray, ultrasounds, Eddy-Currents (ECs) and other means [1], [2], [3]. EC NDT, specifically, is used to assess the condition of conductive materials, by inducing electric currents on them, generated by magnetic fields. The presence of defects will, consequently, modify the magnetic field that is picked up and used to characterize the test subject. This kind of testing is extremely important in areas such aeronautics, aerospace, electric energy production, automotive and many others where human inspection is not practical and/or is dangerous [2]. The conventional EC NDT probes usually implement one or more sensing coils [3]. Other probes rely on sensors, which can be integrated in a chip, but their reduced number usually result in low resolutions.

This work is inserted in the project described in [4] and focus an EC NDT system, in which an array of Magneto-Resistive (MR) sensors is used. The number of sensors in the array can be scaled to allow increased resolution and inspection speed. The sensors present variations in resistance with the applied magnetic field, which are picked up and processed by an Application Specific Integrated Circuit (ASIC), that amplifies signals and filters out the unwanted components.

The EC NDT system, for higher penetration depths, requires lower frequencies. At such frequencies, the transistors of the pre-amplifier included in the ASIC add a high flicker (or lowfrequency) noise contribution, which is a type of noise inversely proportional to the frequency. Also, the sensors are biased by a DC signal that, when amplified, is capable of saturating the output pre-amplifier. In this work, solutions to these two problems are addressed by exploring flicker noise reduction and DC cancellation techniques to produce an improved pre-amplifier for the NDT system.

#### 1.2 Objectives

The focus of this work is the output pre-amplifier of the ASIC and the main goal is to reduce its flicker noise, while blocking input DC signals. For this reason, noise reduction and DC cancellation techniques are studied and applied to this amplifier. The following objectives were established:

study the performance of Autozero and Chopper Stabilization as flicker noise cancellation techniques;

- apply the most suitable technique for this kind of application to the amplifier;

- achieve DC sensor biasing signal cancellation;

- produce the final layout of the amplifier.

Following the presented qualitative objectives, a set of circuit specifications is determined. Notice that since the developing circuit is integrated in a large industrial equipment, the power consumption is not a tight restrain to this project.

| Technology           | AMS 0.35 µm CMOS |

|----------------------|------------------|

| Power Supply [V]     | 3.3              |

| Open Loop Gain [dB]  | 70               |

| Close Loop Gain [dB] | 20               |

| Bandwidth [MHz]      | 10               |

| Phase Margin [°]     | 60               |

| IRN @ 100Hz [nV/√Hz] | <20              |

| DC Attenuation [dB]  | 40               |

Table 1.1: Circuit Specifications

#### 1.3 Main contributions

This thesis aims the production of an amplifier with reduced flicker noise and DC attenuation to be included in an EC NDT system being developed by the working team at INESC-ID, Lisboa. A Chopper Stabilization technique is implemented to reduce flicker noise and a DC Servo Loop (DSL) is used to cancel DC components. These techniques are explored in this thesis to provide useful information for future implementations. A two page abstract ([5]) and a poster for the conference ENDE 2016 on NDT systems were produced. A full paper for inclusion in "Electromagnetic Nondestructive Evaluation" series, to be published by IOS Press, has been delivered.

#### 1.4 Dissertation outline

This thesis is organized in 5 chapters. In this chapter, an introduction to the context of the work and proposed objectives are presented. Chapter 2 introduces and describes in more detail the EC NDT system. It also makes a theoretical review on flicker noise reduction techniques and DC cancellation. Chapter 3 makes a technical overview of this system, describing the sensor biasing and reading, as well as the considerations regarding the amplifier in focus. It also describes the designing process of the circuits proposed. Chapter 4 presents the circuit simulation results obtained and a comment on them. In Chapter 5, conclusions are drawn and future work is proposed.

# State-of-the-art

#### Contents

| 2.1 | Introduction                                           |

|-----|--------------------------------------------------------|

| 2.2 | Eddy-current Non-destructive Testing System            |

| 2.3 | Noise Analysis                                         |

| 2.4 | Flicker Noise Suppression                              |

| 2.5 | Fully-differential Amplifiers and Common-mode Feedback |

| 2.6 | DC Suppression                                         |

| 2.7 | Summary                                                |

#### 2.1 Introduction

In this chapter, the theoretical background of this work is presented and possible solutions for the problems of the pre-amplifier of the ASIC are explored. First, the EC NDT system conceptual way of working is described, followed by a noise analysis of the devices that compose the elementary blocks of the system. Then, the techniques for flicker noise reduction are presented and an introduction to fully-differential amplifiers is made. Finally, a state-of-the-art DC suppression technique is discussed.

#### 2.2 Eddy-current Non-destructive Testing System

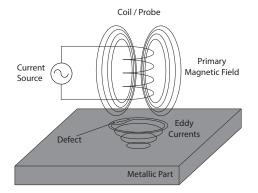

An Eddy-Current (EC) Non-Destructive Testing (NDT) is an efficient metallic body inspection method used in a variety of industries to assure the quality of aircraft fuselage, welds and molds, as an example. This inspection method uses a coil conducting a current, which induces a magnetic field according to Ampère's Law [6]. For a coil, like the one used in EC NDTs, the magnitude of the magnetic field *B* is given by

$$B = \mu n I \tag{2.1}$$

where *n* is the number of turns of the coil,  $\mu$  is the magnetic permeability and *I* the current that travels through the coil. If the current *I* is time-variant, the magnetic field, from now on named primary magnetic field, will also vary in time. As a consequence, a voltage is induced in the conductor material, as stated by Faraday's Law [6]. If there are any closed paths on the material, electric currents appear [7]. These currents will induce a secondary magnetic field, again according to Ampère's Law. In the presence of defects on the conductive material, the magnetic permeability  $\mu$  is changed, altering the characteristics of the secondary magnetic field. If picked up by a device, using a sensing coil, these changes on the secondary magnetic field may indicate flaws on the material.

In the case of the EC NDT system of this work, the changes in the secondary magnetic field are used to detect buried or superficial defects. Figure 2.1 illustrates the process described.

Figure 2.1: Eddy current NDT illustration.

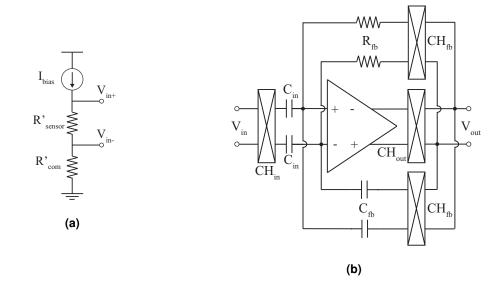

The system of this work generates a primary magnetic field with frequency  $f_1$ , using an emitter coil. Instead of using a sensing coil, the system comprises an array of Magneto-Resistive (MR) sensors, used for defect detection, which are biased by a current of frequency  $f_2$ . These sensors present a variation in their characteristic resistance with the magnetic field applied, producing an electric signal y(t) that carries the information regarding that variation. When operating in their linear region, the total sensor resistance, which is a function of the sensed magnetic field, is given by

$$R_H(t) = R_0 + \Delta R(H(f_1))$$

(2.2)

where  $R_0$  is the nominal resistance and  $\Delta R(H(f_1))$  is the resistance variation as a function of the sensed magnetic field created by the ECs. Given the sensors biasing current as

$$i(t) = I_0 + I_m \sin(2\pi f_2 t), \tag{2.3}$$

the signal y(t) can be written as

$$y(t) = i(t).R_{H}(t) = R_{0}I_{0} + R_{0}I_{m}\sin(2\pi f_{2}t) + R_{m}(f_{b})I_{0}\sin(2\pi f_{1}t) + \frac{R_{m}(f_{b})I_{m}}{2}\sin(2\pi (f_{1} - f_{2})t) + \frac{R_{m}(f_{b})I_{m}}{2}\sin(2\pi (f_{1} + f_{2})t)$$

(2.4)

where  $f_b$  is the signal bandwidth required for a given inspection speed,  $R_m$  and  $I_m$  are the resistance and current variation produced by the MR sensors, respectively. This signal is the processed by an Application Specific Integrated Circuit (ASIC), which is also responsible for the biasing and multiplexing of the sensors [4]. From (2.4), the terms containing the current and resistance variation,  $R_m$  and  $I_m$ , respectively, are the ones that hold useful information regarding the presence of defects and are present at frequencies  $f_1 - f_2$  and  $f_1 + f_2$ .

The frequencies  $f_1$ ,  $f_2$  are set by the user and they depend on the type of material under test and the speed of inspection v. The frequency of the primary magnetic field  $f_1$  is set to achieve a desired depth of penetration  $\delta$ , which is given by

$$\delta = \sqrt{\frac{2}{\omega\mu\sigma}} \tag{2.5}$$

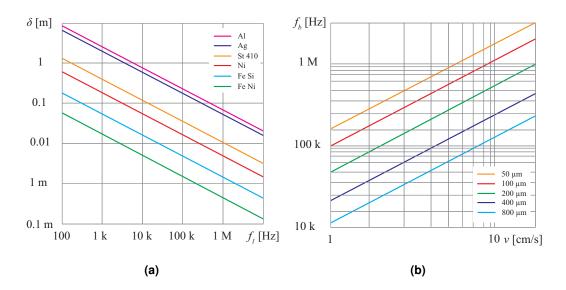

where  $\omega = 2\pi f_1$ ,  $\mu$  and  $\sigma$  are the magnetic permeability and electric conductivity of the material under test, respectively. From (2.5), to achieve the same depth across multiple materials,  $\omega$  must change accordingly. Figure 2.2(a) shows the required primary magnetic field frequency to achieve multiple depths of penetration in some metals [4]. The sensor biasing signal can be a DC, a sine or square wave signal of frequency  $f_2$ , which is also set by the user. It is chosen in such a way that  $f_1 - f_2$  must be within the pre-amplifier bandwidth, so that the information regarding defects can be preserved and the signal amplified. For this work, the sensor biasing signal will be a DC signal. The signal bandwidth  $f_b$  is related to the speed of scanning v and the flaw depth, as shown in Figure 2.2(b). As an example, for a scanning speed v of 10 cm/s, to be able to detect a defect of 800  $\mu$ m, a signal bandwidth  $f_b$  of about 150 kHz is required.

Figure 2.2: System characteristics: (a) excitation frequency for several materials and depths; (b) signal bandwidth for several scanning speeds and depths.

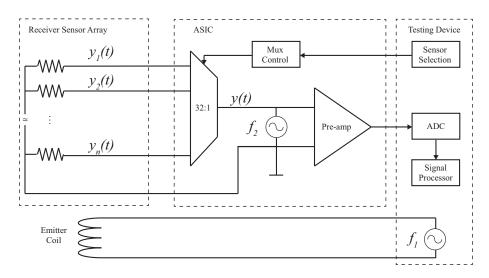

Figure 2.3 shows a top-level diagram of the system. It is composed by a sensor array with up to 32 MR sensors, each one producing a signal that is selected by the ASIC and then read. This selection is accomplished by a multiplexer controlled by the testing device, such as a computer. The multiplexer outputs the signal y(t), described in (2.4), being amplified by the pre-amplifier included in the ASIC and fed to an Analog to Digital Converter (ADC) for digital signal processing.

Figure 2.3: Top-level diagram of the system.

As shown in Figure 2.5, for deeper penetration on the testing material, it is required a lowfrequency magnetic field, resulting in low-frequency output signals, where flicker noise is also present and can impair readings. The pre-amplifier will be addressed to tackle this problem and to block the DC biasing signal coming from the sensors that can easily saturate it.

#### 2.3 Noise Analysis

To understand how noise can corrupt readings, there is the need to know how noise behaves and how it can be modeled, so that it can be predicted and dealt with in the design phase. First, a noise model of the Metal–Oxide–Semiconductor (MOS) transistor is defined, followed by the characterization of the noise of a Common-Source (CS) stage. The CS stage will be used as a basic block to define the noise of more complex circuits, such as the cascode stage and the differential pair. To finish, three typical Operational Transconductance Amplifier (OTA) topologies are analyzed and compared.

#### 2.3.1 Noise in MOSFET Transistors and Single Stage Amplifiers

As the MOS transistor is the main building block of circuits in integrated electronics, it is important to define its noise model, concerning the two main noise types: thermal (white) noise and flicker (pink) noise, also called low-frequency or 1/f noise.

Thermal noise is caused by voltage fluctuations, originated by the random motion of electrons in a conductor. This type of noise is proportional to the absolute temperature [8], since temperature elevations cause an increase in kinetic energy of electrons, leading to an even more erratic motion, increasing the voltage fluctuations, thus increasing thermal noise. In MOS transistors, the most significant source of thermal noise is the channel. The thermal noise can be modeled as a current source connected between drain and source or as a voltage source connected to the gate, as shown if Figure 2.4.

Figure 2.4: MOS noise models: (a) as a current source; (b) as a voltage source.

According to [8] the thermal noise current  $\overline{I_n^2}$  and the thermal noise voltage  $\overline{V_n^2}$  are, respectively, given by

$$\overline{I_{n,thermal}}^2 = \frac{2}{3}g_m(4k_BT) \tag{2.6}$$

and

$$\overline{V_{n,thermal}}^2 = \frac{2}{3}g_m(4k_BT)r_o^2$$

(2.7)

where  $k_B$  is the Boltzmann constant, T is the temperature in Kelvin,  $g_m$  and  $r_o$  are the transconductance and output impedance of the transistor, respectively.

Flicker noise is another important type of noise and occurs due to trapping of charges in the interface between the silicon substrate and the gate oxide. When these charges are released, they add a contribution to the drain current in the form of noise. This phenomenon happens more often at low frequencies, therefore being also called 1/f noise [8]. The flicker noise current  $\overline{I_{n,flicker}}^2$  and flicker noise voltage  $\overline{V_{n,flicker}}^2$  are respectively given by

$$\overline{I_{n,flicker}}^2 = \frac{K}{C_{OX}WL} \frac{1}{f} g_m^2$$

(2.8)

and

$$\overline{V_{n,flicker}}^2 = \frac{K}{C_{OX}WL} \frac{1}{f}$$

(2.9)

where *K* is the flicker noise parameter, that depends on the process and the type of transistor (p-type or n-type),  $C_{OX}$  is the capacitance per unit area of the gate oxide, *W* and *L* are the width and length of the channel, respectively.

#### Noise of a Common-source Stage

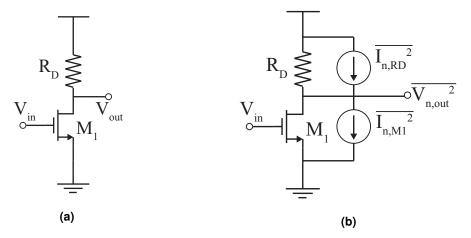

Given the noise model for a MOS transistor, it is important to analyze a basic and common circuit used in amplifiers. It is the case of the CS stage of Figure 2.5(a).

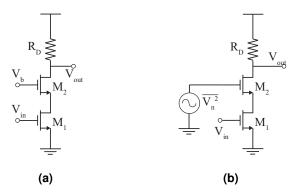

Figure 2.5: Common-source stage noise: (a) without noise sources; (b) with noise sources.

From Figure 2.5(b) the total output noise current can be written as the sum of the individual noise contributions of the components:

$$\overline{I_{n,out}}^2 = \frac{2}{3}g_m(4k_BT) + \frac{K}{C_{OX}WL}\frac{1}{f}g_m^2 + \frac{4k_BT}{R_D},$$

(2.10)

where  $R_D$  is the drain resistor. Consequently, the total output noise voltage  $\overline{V_{n,out}}^2$  is found by multiplying the output noise current  $\overline{I_{n,out}}^2$  by  $R_D^2$ . As the output noise depends on the gain of the circuit, a normalization to noise is appropriate for better comparison between different circuits. For this reason the concept of Input-Referred Noise (IRN) is introduced. The IRN allows the effects of all noise sources of a circuit to be represented as a single noise voltage source at the input of the

circuit. In order to be independent of the gain of the circuit, the IRN is found by taking the output noise voltage and divide it by the gain, which in this case is given by

$$\overline{V_{n,in}^{2}} = \frac{\overline{V_{n,out}}^{2}}{A_{v}^{2}}$$

$$= \left(\frac{2}{3}g_{m}(4k_{B}T) + \frac{K}{C_{OX}WL}\frac{1}{f}g_{m}^{2} + \frac{4k_{B}T}{R_{D}}\right)R_{D}^{2}\frac{1}{g_{m}^{2}R_{D}^{2}}$$

$$= \frac{2}{3g_{m}}(4k_{B}T) + \frac{K}{C_{OX}WL}\frac{1}{f} + \frac{4k_{B}T}{g_{m}^{2}R_{D}}$$

(2.11)

From (2.11) it is noticeable that to reduce the overall IRN, the dimensions of the transistor should be increased, as well as its transconductance. As can be noticed, the last term of the sum is the noise contribution of the resistor  $R_D$ .

#### Noise of a Cascode Stage

As for the cascode stage, in Figure 2.6(a), the noise contribution of  $M_2$  can be modeled as a voltage source (Figure 2.6(b)). In this view, the circuit can be seen as a CS with a source resistor  $r_{o1}$ , which is the output resistance of  $M_1$ . Thus, the gain of  $M_2$  is given by  $g_{m2}R_D/(1+g_{m2}r_{o1})$  [9]. If the output resistance of  $M_1$  is large, then the gain of  $M_2$  is reduced and is much smaller than the gain seen from the gate of  $M_1$ . Since the noise voltage  $\overline{V_n^2}$  is much less amplified than the actual input signal  $V_{in}$ , noise contributions of cascode transistors are neglected.

Figure 2.6: Cascode stage noise: (a) Cascode stage; (b) Noise modeled by voltage source.

#### Noise of a Differential Pair

Another important circuit in this study is the differential pair with resistive load (Figure 2.7). In Figure 2.7(b) the noises of  $M_1$  and  $M_2$  are modeled by two voltage sources placed at the gate of each transistor. The resistors are also modeled by two voltage sources. Notice that each branch of the differential pair can be seen as a CS stage with a total IRN given by (2.11). Therefore, for matched transistors, the total IRN of the differential pair is twice the IRN of a CM stage:

$$\overline{V_{n,in,total}^2} = 2\left(4k_BT\left(\frac{2}{3g_m} + \frac{1}{g_m^2R_D}\right) + \frac{K}{C_{OX}WL}\frac{1}{f}\right).$$

(2.12)

Figure 2.7: A differential pair: (a) without noise sources; (b) with noise sources.

As seen in CS stages, to reduce thermal noise in a differential pair, the transconductance  $g_m$  of the transistors should be increased. Since

$$g_m = \frac{2I_D}{V_{OD}} = \sqrt{2K_{N,P}\frac{W}{L}I_D},$$

(2.13)

where  $K_{N,P}$  is the gain factor and  $V_{OD}$  is the overdrive voltage of the transistor, for the same transistor area and current, the choice of an NMOS transistor over a PMOS transistor leads to smaller thermal noise. As  $K_N$  has a value of 170  $\mu$ A/V<sup>2</sup> and  $K_P$  has a value of 58  $\mu$ A/V<sup>2</sup> in the AMS 0.35  $\mu$ m CMOS process, the relation between the thermal noise contribution of an NMOS and the thermal noise contribution of a PMOS is given by

$$\frac{V_{n,NMOS}^2}{V_{n,PMOS}^2} = \sqrt{\frac{K_P}{K_N}} \approx \frac{1}{\sqrt{3}}.$$

(2.14)

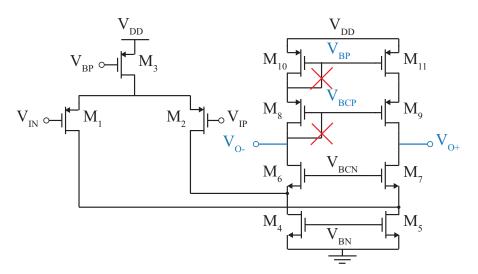

In spite of having a smaller thermal noise contribution, NMOS transistors have a higher flicker noise corner frequency  $f_k$ , which is defined as the frequency where the flicker Power Spectral Density (PSD) equals the thermal noise PSD. This is a problem, since for the same frequency, the flicker noise contribution of an NMOS is higher. As the goal of this work is to mitigate flicker noise, a PMOS differential pair for the amplifier will be implemented, because the flicker noise contribution is smaller, despite having an higher thermal noise contribution, which can be managed by careful design, as described in the following subsection.

#### 2.3.2 Noise in Operational Transconductance Amplifiers

Operational Transconductance Amplifiers (OTAs) are widely used amplifiers as they provide very high gains, large bandwidths and can achieve good noise performances. For these reasons, an OTA will be implemented as the pre-amplifier of the ASIC. Here the three main topologies are analyzed, namely telescopic, mirrored and folded cascode, regarding their noise. In this analysis, only thermal noise is taken into account, as flicker noise mitigation will be covered ahead.

#### **Telescopic OTA**

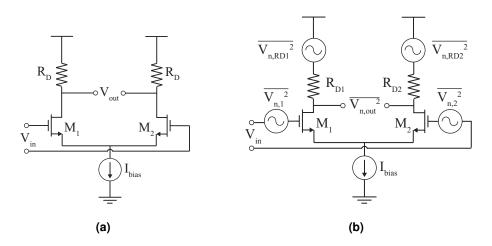

The IRN of the telescopic OTA (Figure 2.8) can be found by summing the thermal noise current contributions of each transistor to the output [10]. The total thermal noise current contribution to the output is given by

$$\overline{I_{n,out}^2} = 4k_B T \left[ 2\left(\frac{2}{3}g_{m1,2}\right) + 2\left(\frac{2}{3}g_{m9,10}\right) \right]$$

(2.15)

where  $k_B$  is the Boltzmann constant, T is the temperature in Kelvin and  $g_m$  is the transconductance of the transistor. Notice that transistors  $M_{5-8}$  have a negligible contribution to the thermal noise, since they are cascode stages (subsection 2.3.1). As for transistors  $M_{3,4}$ , the noise current generated by them is seen by the differential pair as a Common-Mode (CM) signal, hence is greatly attenuated, giving the differential nature of the amplifier. The IRN voltage of the amplifier is

Figure 2.8: Telescopic OTA.

obtained by dividing the total noise current contribution, (2.15), by the squared transconductance of  $M_{1,2}$ :

$$\overline{V_{n,in}^2} = \frac{\overline{I_{n,out}^2}}{g_{m1,2}^2} = 16 \frac{k_B T}{3g_{m1,2}} \left(1 + \frac{g_{m9,10}}{g_{m1,2}}\right).$$

(2.16)

Since the transconductance of a transistor is given by

$$g_m = \frac{2I_D}{V_{OD}},\tag{2.17}$$

where  $I_D$  is its drain current and  $V_{OD}$  is its overdrive voltage, (2.16) is rewritten as

$$\overline{V_{n,in}^2} = 16 \frac{k_B T \, V_{OD1,2}}{3I_{D3}} \left(1 + \frac{1}{A_1}\right),\tag{2.18}$$

where  $A_1$  is given by

$$A_1 = \frac{V_{OD9,10}}{V_{OD1,2}}.$$

(2.19)

From (2.18) and (2.19), to reduce the IRN, the overdrive voltage of transistors  $M_{1,2}$ ,  $V_{OD1,2}$ , should be lower than the overdrive voltage of  $M_{9,10}$ ,  $V_{OD9,10}$ .

#### **Mirrored OTA**

By applying the same principles to the mirrored OTA (Figure 2.9), its total noise current contribution to the output of is given by

$$\overline{I_{n,out}^2} = 4k_B T \left[ 2\left(\frac{2}{3}g_{m1,2}n^2\right) + 2\left(\frac{2}{3}g_{m5,6}n^2\right) + 2\left(\frac{2}{3}g_{m7,8}\right) + \left(\frac{2}{3}g_{m13,14}\right) \right]$$

(2.20)

where *n* is the current gain of the current mirrors formed by  $M_{5-8}$ . Once again, cascode transistors ( $M_{9-12}$ ) have a negligible noise contribution. Transistors  $M_{3,4}$  also do not contribute to the noise because the noise current they generate is seen as a CM signal by the differential pair.

Figure 2.9: Mirrored OTA.

The total IRN is then given by

$$\overline{V_{n,i}^{2}} = \frac{\overline{I_{n,out}^{2}}}{g_{m1,2}^{2}n^{2}} = \frac{16k_{B}T}{3g_{m1,2}} \left( 1 + \frac{g_{m5,6}}{g_{m1,2}} + \frac{g_{m7,8}}{g_{m1,2}^{2}n^{2}} + \frac{g_{m13,14}}{g_{m1,2}^{2}n^{2}} \right)$$

$$= \frac{16k_{B}TV_{OD1,2}}{3I_{D3}} \left( 1 + \frac{1}{A_{2}} + \frac{1}{B_{2}n} + \frac{1}{C_{2}n} \right)$$

(2.21)

where  $A_2$ ,  $B_2$  and  $C_2$  are, respectively, given by

$$A_2 = \frac{V_{OD5,6}}{V_{OD1,2}} \qquad B_2 = \frac{V_{OD7,8}}{V_{OD1,2}} \qquad C_2 = \frac{V_{OD13,14}}{V_{OD1,2}}$$

(2.22)

To reduce the total IRN, parameters  $A_2$ ,  $B_2$  and  $C_2$  should be increased, that is the overdrive voltage of the transistors  $M_{1,2}$ ,  $V_{OD1,2}$ , should be lower than  $V_{OD5,6}$ ,  $V_{OD7,8}$  and  $V_{OD13,14}$ , respectively. Also the current gain n can be increased to reduce the noise, implicating a higher power consumption.

#### **Folded Cascode OTA**

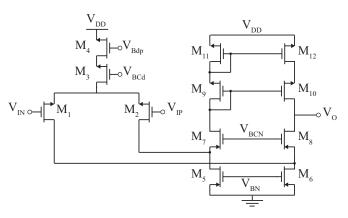

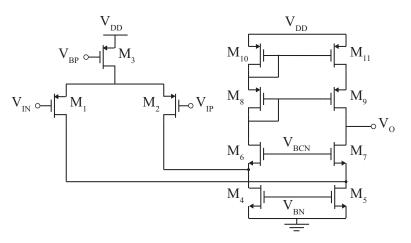

Figure 2.10 shows the schematic of a folded cascode OTA, the last of the three topologies to be analyzed. In a similar manner, its total noise current contribution to the output is found by summing the individual noise current contributions of each transistor, therefore

Figure 2.10: Folded Cascode OTA.

$$\overline{I_{n,out}^2} = 4k_B T \left[ 2\left(\frac{2}{3}g_{m1,2}\right) + 2\left(\frac{2}{3}g_{m5,6}\right) + \left(2\frac{2}{3}g_{m1,12}\right) \right].$$

(2.23)

Noise, the IRN is given by

$$\overline{V_{n,i}^2} = \frac{\overline{I_{n,out}^2}}{g_{m1,2}^2} = \frac{16k_BT}{3g_{m1,2}} \left( 1 + \frac{g_{m5,6}}{g_{m1,2}} + \frac{g_{m11,12}}{g_{m1,2}} \right)$$

$$= \frac{16k_BT V_{OD1,2}}{3I_{D3}} \left( 1 + \frac{C_3 - 1}{A_3} + \frac{C_3}{B_3} \right)$$

(2.24)

where  $A_3$ ,  $B_3$  and  $C_3$  are, respectively, given by

$$A_3 = \frac{V_{OD5,6}}{V_{OD1,2}} \qquad B_3 = \frac{V_{OD11,12}}{V_{OD1,2}} \qquad C_3 = \frac{2I_{D11}}{I_{D3}}.$$

(2.25)

From (2.24) and (2.25) it is clear that to minimize the noise  $A_3$  and  $B_3$  must be maximized. The current flowing through the cascode transistors should be lower than the current flowing through the differential pair, making  $C_3$  slightly higher than unity.

#### **OTA Comparison**

In [10] the same analysis is made and values are added to the parameters  $A_{1,2,3}$ ,  $B_{2,3}$  and  $C_{2,3}$ , in order to quantify the IRN and total current of the three topologies. The same supply voltages and amplifier tail current  $I_{D3}$  are used.

As seen, in the telescopic amplifier,  $V_{OD1,2}$  must be lower than  $V_{OD9,10}$ , making  $A_1$  larger than unity. In [10] is set to five. For the mirrored amplifier,  $A_2$ ,  $B_2$  and  $C_2$  follow the same principle as for  $A_1$ , and they also set to five. In order not to penalize the total current relatively to the other topologies, the current gain n is set to one. As for the folded cascode,  $A_3$  is set to three,  $B_3$  is set to five and  $C_3$  is set to 5/4, making the tail current four times larger than the one of the cascode transistors, that is  $I_{D3} = 4I_{D9}$ .

As seen, the differential pairs of the amplifiers reviewed have a thermal noise contribution of

$$\overline{V_{n,dpair}^2} = \frac{16k_B T \, V_{OD1,2}}{3I_{D3}} \tag{2.26}$$

and, in order to compare the three topologies, the normalized thermal noise in respect to  $V_{n,dpair}^2$  is introduced as

$$\overline{V_{n,normalised}^2} = \frac{\overline{V_{n,OTA}^2}}{\overline{V_{n,dpair}^2}}$$

(2.27)

where  $\overline{V_{n,OTA}^2}$  is the total thermal noise of each OTA topology. Table 2.1 presents the comparison of the three topologies, made in [10], in terms of normalized noise and total current, for the same technology and power supply.

|                | Normalized Noise | Total Current |

|----------------|------------------|---------------|

| Telescopic     | 1.2              | $I_{D3}$      |

| Mirrored       | 1.6              | $2I_{D3}$     |

| Folded Cascode | 1.3(3)           | $1.25I_{D3}$  |

Table 2.1: OTA comparison.

The telescopic OTA achieves the best performance, having the lowest noise and total current, while the mirrored OTA has the worst noise performance and the highest power consumption. Although the folded cascode achieves worse noise performance and has a higher power consumption than the telescopic OTA, it will be the chosen amplifier to implement in the NDT system, since its noise performance is just slightly worse and, in order to polarize the transistors in the output rail into saturation region, a higher voltage is needed in the telescopic, leaving a smaller headroom voltage. Also, the power consumption for this work is not a major concern.

#### 2.4 Flicker Noise Suppression

In the previous section, it was shown that the thermal noise of three main OTA topologies can be mitigated by increasing the overdrive voltages of the differential pairs and by increasing the tail currents. However, this approach does not reduce flicker noise. As seen, flicker noise is inversely proportional to the frequency f, meaning that when there is the need to process weak and lowfrequency signals, these are greatly affected by flicker. To suppress flicker noise two widely used techniques may be employed: Autozero and Chopper Stabilization. Both of them will be described in the following subsections.

#### 2.4.1 Autozero

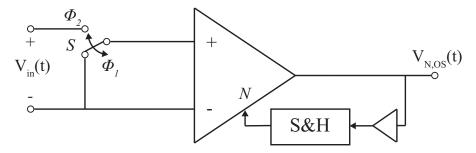

The basic principle behind the Autozero is to sample the noise and/or offset at the output of the amplifier and subtract it from the signal [11]. As seen in Figure 2.11, this method contemplates two phases. In the first phase,  $\phi_1$ , switch *S* short-circuits the input of the amplifier and by doing so, the only quantities appearing at its output are the noise and offset,  $V_{N,OS}(t)$ . Then, this offset and noise are sampled by the Sample & Hold (S&H) block. In phase  $\phi_2$ , *S* switches back to the signal and the voltage stored in the S&H is applied to the amplifier (*N*), thus subtracting it to the signal.

Figure 2.11: Basic Autozero implementation.

Following the principle described, during phase  $\phi_1$ , the output of the circuit in Figure 2.11 only contains a near DC signal component,  $V_{N,OS}(t)$ , that describes the output flicker noise and offset. At the sampling instant,  $t_1$ ,  $V_{N,OS}(t_1)$  is stored in the S&H and applied to the amplifier in the instant  $t_2$ , to subtract it from  $V_{N,OS}(t_2)$ . As the component  $V_{N,OS}(t)$  is near DC, during an infinitesimal time interval  $\Delta t = t_2 - t_1$ , the voltage  $V_{N,OS}$  will approximately keep a constant value  $(V_{N,OS}(t_1) \approx V_{N,OS}(t_2))$ , which means that when the sampled voltage is applied to the amplifier, a near perfect noise and offset cancellation is achieved, theoretically.

However, real amplifiers have a larger bandwidth flicker noise component  $V_{N,OS}(t)$ , thus the quantity sampled by the S&H block ( $V_{N,OS}(t_1)$ ) and the quantity to be subtracted ( $V_{N,OS}(t_2)$ ) can be different. This results in an imperfect noise cancellation. In addition, real amplifiers also have a thermal noise (or white noise) component that is constant across the spectrum and a low-pass characteristic with a cut-off frequency  $f_{-3dB}$ . Since the sampling frequency  $f_S$  is lower than the amplifier cut-off frequency  $f_{-3dB}$ , the system suffers from undersampling leading to aliasing that increases the overall noise of the amplifier [11].

The efficiency of this process is as high as the correlation between the quantity sampled by the S&H,  $V_{N,OS}(t_1)$ , and the instantaneous noise value to be subtracted,  $V_{N,OS}(t_2)$ . As this correlation between two samples of flicker noise/offset, separated by a time interval  $\Delta t$ , decreases slower for an increasing  $\Delta t$  than it does for thermal noise [11], for time-varying random noise, Autozero has an high-passing effect over the noise, resulting in a flicker noise attenuation. However, since Autozero is a sampling-based technique, it introduces aliasing which increases the noise floor of the signal. Also, the voltage stored in the S&H block may suffer from errors, namely quantization errors (when the sampling block is implemented using ADCs and/or Digital to Analog Converters (DACs)) or leakage currents (when using capacitors for sampling).

#### 2.4.2 Chopper Stabilization

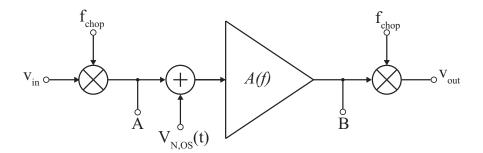

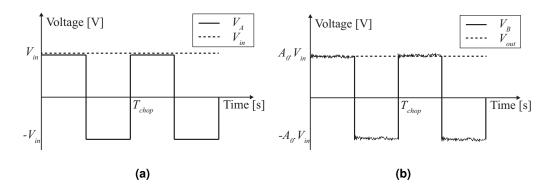

Chopper Stabilization is a flicker noise reduction technique that uses modulation to shift the spectrum of the signal to high frequencies, where the flicker noise contribution is negligible, and then, after amplification, the signal is demodulated back to its baseband, while flicker is up-modulated. Figure 2.12 shows a diagram describing the general Chopper Stabilization process.

Figure 2.12: Diagram of chopper stabilization.

Let the input signal be a DC voltage,  $V_{in}$  (Figure 2.13(a)). This signal is modulated by a square wave carrier of frequency  $f_{chop}$  and unitary amplitude, that results in a square wave of the same frequency and amplitude  $V_{in}$  (Figure 2.13(a)). After modulation, the IRN and offset of the amplifier (represented by  $V_{N,OS}(t)$ ) are added. After being amplified, the output of the amplifier (Figure 2.13(b)) is, a square wave with amplitude  $A_0.V_{in}$  (if the amplifier is ideal, i.e. with infinite bandwidth and DC gain  $A_0$ ).

Figure 2.13: Signals along the Chopper Stabilization circuit diagram (Figure 2.12): (a)  $V_{in}$  and  $V_A$ ; (b)  $V_B$  and  $V_{out}$

Figure 2.14 shows the spectra of the signals along the signal path of the chopper circuit (Figure 2.12). Suppose the signal  $V_{in}$ , which has a spectrum represented on Figure 2.14(a), is modulated by the referred carrier. The resulting signal,  $V_A$ , (Figure 2.13(a)) has a spectrum that is composed by replicas of the spectrum of the input signal  $V_{in}$ , centered on odd multiples of the carrier frequency  $f_{chop}$  (Figure 2.14(b)), since the carrier is a square wave, with only odd harmonics. The modulated signal is then exposed to noise and amplified, before it is demodulated, resulting in signal  $V_B$  (Figure 2.13(b)), with a spectrum represented in Figure (2.14(c)). Demodulation is accomplished by using the same carrier wave, as before. This time, the flicker noise component is shifted to the odd harmonics of the carrier and the spectrum of the signal returns to its baseband (Figure 2.14(d)). The resulting signal can be, afterwards, low-pass filtered in order to eliminate the unwanted quantities present at the odd multiples of the chopper frequency  $f_{chop}$ , if necessary.

Figure 2.14: Spectra of signals at several stages of chopper stabilization process: (a) input signal; (b) signal after the first modulation; (c) signal after amplification; (d) output signal.

As seen, Chopper Stabilization is a fully-analog technique that uses modulation to shift flicker noise to an high frequency, where it does not overlap with signal spectral components, thus it can be filtered out afterwards. Unlike Autozero, that is a sampling-based technique, Chopper Stabilization does not introduce aliasing that increases the noise floor [11] and does not need complex sampling circuits. For these reasons, Chopper Stabilization is the technique chosen to implement on the folded cascode amplifier, that will compose the pre-amplifier block of the ASIC. Therefore, a further analysis on this technique is made, regarding its effects on baseband noise and how the modulations are performed.

#### Effect of Chopper in Baseband Noise

Chopper Stabilization does not introduce aliasing, however, it has important effects on the noise Power Spectral Density (PSD), in baseband. The PSD of the chopped output signal  $V_{out}$  can be written as

$$S_{out}(f) = \left(\frac{2}{\pi}\right)^2 \sum_{\substack{n=-\infty\\n \text{ odd}}}^{+\infty} \frac{1}{n^2} S_N\left(f - \frac{n}{T_{chop}}\right)$$

(2.28)

where *n* is the number of the signal harmonic,  $S_N$  is the PSD of a stationary random noise and  $T_{chop}$  is the period of the chopper carrier, according to [11]. For the sum of the replicas of the spectrum shifted to the harmonics n = -3, -1, 1, 3 and for an amplifier with cut-off frequency  $f_{-3dB}$  equal to five times the chopper frequency  $f_{chop} = 1/T_{chop}$ , (2.28) can be approximated in

the baseband ( $|f| \le 0.5 f_{chop}$ ) by a white noise PSD

$$S_{out-white}(f) \cong S_{out-white}(f=0)$$

=  $S_0 \left[ 1 - \frac{\tanh\left(\frac{\pi}{2}f_{-3dB}T_{chop}\right)}{\frac{\pi}{2}f_{-3dB}T_{chop}} \right],$  (2.29)

which simplifies in

$$S_{out-white} \cong S_0 \quad \text{ for } |f| \le 0.5 f_{chop} \text{ and } f_{-3dB} \gg f_{chop},$$

(2.30)

where  $S_0$  is the input thermal noise PSD [11]. The effect of Chopper Stabilization on flicker noise can be derived from (2.28), considering  $f_{-3dB} \gg f_{chop}$  and an input PSD given by

$$S_{N-flicker}(f) = S_0 \frac{f_k}{|f|},$$

(2.31)

where  $f_k$  is the flicker noise corner frequency defined as the frequency where the flicker PSD equals the white noise PSD. Again, the output flicker noise contribution PSD can be approximated by a white noise component:

$$S_{out-flicker}(f) \cong 0.8525 S_0 f_k T.$$

(2.32)

Hence, the total noise contribution is found by summing (2.30) and (2.32):

$$S_{out}(f) \cong S_0(1 + 0.8525 f_k T_{chop})$$

for  $|f| \le 0.5 f_{chop}$  and  $f_{-3dB} \gg f_{chop}$ . (2.33)

Chopper Stabilization is used to shift most of the flicker noise PSD out of baseband. However, it slightly increases the noise PSD in baseband. From (2.33), it can be noticed that the output noise PSD, in baseband, is approximated by a constant white noise, proportional to the input PSD  $S_0$ . It also has a contribution proportional to the flicker corner frequency  $f_k$  and inversely proportional to the chopper frequency  $f_{chop}$ , which means that if  $f_{chop}$  is made, for example, equal to the flicker noise corner frequency  $f_k$ , the output noise PSD, in baseband, is approximately equal to twice the input PSD  $S_0$ . For this reason,  $f_k$  should be reduced and  $f_{chop}$  increased, which will result in an almost constant output PSD, with a value approximately equal to the input PSD  $S_0$ .

#### **Chopper Modulation**

After analyzing how Chopper Stabilization works and its effects on noise in baseband, the way modulation is performed in practice is explained and important concerns regarding this process are presented.

As referred, for Chopper Stabilization to work, the input and output signals of the amplifier must be modulated in amplitude. This is accomplished by chopper modulators that use a square wave, of frequency  $f_{chop}$  and unitary amplitude, as a carrier, which is shaped by the input signal. The modulator output signal is then the multiplication of the input signal by the carrier, which,

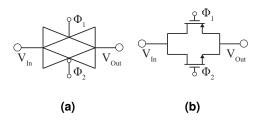

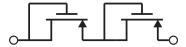

from Figure 2.13, can be seen as a periodical inversion of the input signal, with frequency  $f_{chop}$ . Internally, chopper modulators are simple circuits composed by two pairs of switches, triggered by opposite clock phases (Figure 2.15(a)). They also have two input and two output terminals that allow differential signals to be switched, creating the referred periodical inversion of the input signal, to achieve its modulation.

Figure 2.15: Representation of a chopper modulator: (a) ideal switches; (b) switches implemented as NMOS transistors.

Consider the input,  $V_{in,mod}$ , and the output,  $V_{out,mod}$  signals to be differential ones, that is  $V_{in,mod} = V_{in,mod+} - V_{in,mod-}$  and  $V_{out,mod} = V_{out,mod+} - V_{out,mod-}$ . During phase  $\phi_1$ , switches  $S_1$  and  $S_4$  are closed and the remaining are opened, making  $V_{in,mod+} = V_{out,mod+}$  and  $V_{in,mod-} = V_{out,mod-}$ , therefore,  $V_{out,mod} = V_{in,mod}$ . On the next phase,  $\phi_2$ , switches  $S_2$  and  $S_3$  are now closed, while  $S_1$  and  $S_4$  are opened, making  $V_{in,mod+} = V_{out,mod-}$  and  $V_{in,mod-} = V_{out,mod+}$ , leading to  $V_{out,mod} = -V_{in,mod}$ , and, consequently, to the desired signal  $V_A$ , shown in Figure 2.13(a). The switches used to modulate the signals are usually simple MOS transistors, as seen in Figure 2.15(b).

The usage of single transistors often lead to some problems, like charge injection [11], which is a phenomenon that occurs at the interruption of the channel of the MOS transistor as it enters cut-off region. As the channel is constituted by moving charges, upon entering cut-off region, the channel is interrupted and these charges are split, flowing to the drain and source terminals. The charge splitting is not uniform, as it depends on the impedance at each one of these terminals. Furthermore, the amount of charge injected is proportional to the parasitic capacitances of the transistor, that depend on its area, meaning that larger transistors will have more charges injected [11]. In this particular application, charge injection may lead to residual offsets and increased IRN, if the charges are injected into high impedance nodes, such as the inputs of an amplifier.

The usage of single MOS transistors as switches also lead to reduced signal input swing as both NMOS and PMOS transistors are not capable of being "ON" during all the voltage range, resulting in signal distortion. To understand how the use of a single MOS transistor can have limited voltage swing, consider an NMOS operating as a switch with a load capacitor (Figure

Figure 2.16: Circuits for determining the dynamic range of switches: (a) NMOS switch; (b) PMOS switch.

2.16(a)). If at a given moment,  $t_0$ ,  $V_{out}$  is low (defined as 0 V) and the input,  $V_{in}$ , transits from low to high ( $V_{DD}$  V), the transistor is "ON" while the gate to source voltage is higher than the threshold voltage, that is  $V_{GS} > V_{THn}$ . Since  $V_{GS} = V_{DD} - V_{out}$ , the transistor will remain "ON" until the output reaches  $V_{DD} - V_{THn}$ , thus not being able to pass a true "1" digital value to the output. In a similar way, a PMOS transistor is not able to pass a true "0" digital value to the output. Consider now the circuit of Figure 2.16(b), where, at  $t_0$ , the output is high and the input is transitioning from high to low. Given this, the transistor will be "ON" while  $V_{SG} > V_{THp}$ . As  $V_{SG} = V_{out} - 0$ , the transistor will remain "ON" until the output reaches  $V_{THp}$ . To overcome the problem of charge injection and increase the input swing of switches, modifications to the modulator of Figure 2.15(b) are proposed.

#### Switches for Chopper Modulators

To reduce the effects of charge injection, shorted half-sized dummy transistors are added to the drain and source of the main transistor (Figure 2.17(a)) and triggered with a clock phase opposite to the one of the main switch (Figure 2.17(b)). When the main switch turns off and interrupts its channel, the charges that compose it leave the transistor through the drain and source. At the same time, the dummy switches are switching on, thus they are attracting the charges injected by the main transistor to compose their channel. This way, the amount of charges injected into the high impedance nodes is reduced.

Figure 2.17: Modulator switch implemented as a: (a) NMOS transistor; (b) NMOS transistor with half-sized dummies.

To increase signal input swing Transmission Gates (TGs) can be used. The TG is a form of switch composed by a PMOS transistor and a NMOS transistor in parallel, triggered by opposite

clock phases, as shown in Figure 2.18(a). This configuration achieves good pull-up and pull-down performances, just like in the inverter circuit [9], increasing the input signal swing.

Figure 2.18: Transmission Gate: (a) circuit; (b) symbol.

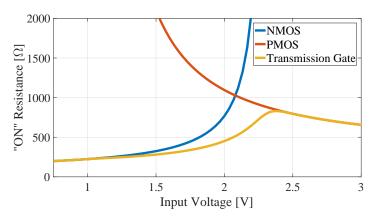

The "ON" resistance is defined as the source-to-drain resistance of the transistor, when it works as a turned on switch. It is an important parameter as high "ON" resistances cause significant voltage drops that may lead to significant signal losses, if the switch is place on the signal path. By combining NMOS and PMOS in parallel, an almost constant "ON" resistance of the switch is achieved, as seen in Figure 2.19, leading to smaller voltage drops across terminals and smaller power losses.

Figure 2.19: "ON" resistance of a NMOS, PMOS and a TG. Both NMOS and PMOS results were simulated for W/L = 10/0.35. The TG results were calculated using data of the other two curves.

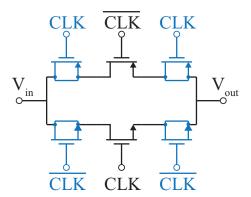

Half-sized shorted dummy switches are added to the drain and source terminals of the transistors of the TGs, to place an equal parasitic capacitance in those terminals, to achieve an equal charge splitting at the "ON" and "OFF" transitions, reducing the effects of charge injection introduced by the TGs [10], which may be larger than with single transistor configurations. For these reasons, switches composed by dummy compensated TGs are chosen to implement the modulators used in Chopper Stabilization.

Figure 2.20: TG with half-sized dummy transistors.

## 2.5 Fully-differential Amplifiers and Common-mode Feedback

As referred in Section 2.4 the usage of Chopper Stabilization to reduce flicker noise, requires the addition of modulators to the circuit. Since the modulators are differential circuits, the preamplifier of the ASIC will be implemented as a fully-differential folded cascode amplifier. For this reason, fully-differential amplifiers are here covered.

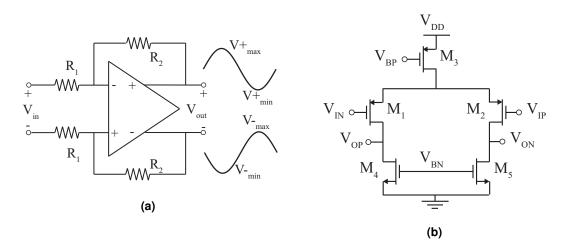

Figure 2.21: Example of: a) an inverting fully-differential amplifier with resistive feedback; b) transistor level implementation of the amplifier.

The major difference of fully-differential amplifiers relies on the fact that a differential signal is seen as the difference of two individual signal components, (non-inverting,  $V_{signal+}$ , and inverting,  $V_{signal-}$ , components), that is  $V_{signal} = V_{signal+} - V_{signal-}$ . Therefore, fully-differential amplifiers have two inputs and two outputs, thus requiring two feedback networks, as seen in Figure 2.21. Also, fully-differential amplifiers have twice the output swing of its single-ended counterpart [12].

Let the amplifier input be a sine wave. Its non-inverting and inverting outputs are also sine waves, but with opposite phases (Figure 2.21(a)). If the output of a singled-ended amplifier swings up to  $V_{max}$  and down to  $V_{min}$ , its output peak-to-peak maximum value is given by  $V_{max} - V_{min}$ .

In a differential amplifier, a single output (inverting or non-inverting) also swings up to  $V_{max}$  and down to  $V_{min}$ , leading to the same peak-to-peak voltage  $V_{max} - V_{min}$ . However, since the output is differential ( $V_{out} = V_{out+} - V_{out-}$ ) and  $V_{out+}$  and  $V_{out-}$  are in phase opposition, the maximum differential output voltage is  $2(V_{max} - V_{min})$ . This also leads to a higher Signal-to-Noise Ratio (SNR), when compared to single-ended amplifiers. Since the signal is twice larger, so is its power, leading to a SNR twice larger or 3 dB above the SNR of single-ended amplifier.

Fully-differential amplifiers are less susceptible to Common-Mode (CM) noise and power supply noise, as well. Consider the amplifier of Figure 2.21(b), where a small variation on the power supply occurs, that is  $V'_{DD} = V_{DD} + \Delta V$ . In that case, the source to gate voltage of  $M_3$ ,  $V_{SG3} = V'_{DD} - V_{BP}$  suffers the same variation  $\Delta V$ , that is

$$V_{SG3} = V_{DD} + \Delta V - V_{BP}, \qquad (2.34)$$

which results in drain current given by

$$I_{D3} = \frac{1}{2} K_P \frac{W}{L} \left( V_{DD} + \Delta V - V_{BN} - V_{THp} \right)^2.$$

(2.35)

If the circuit is balanced, this current is equally split between  $M_1$  and  $M_2$ , which will produce a null output differential voltage, thus rejecting the variations of the power supply.

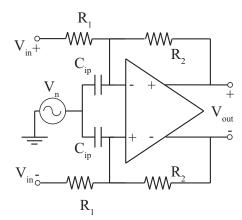

Figure 2.22: Fully-differential amplifier with CM noise.

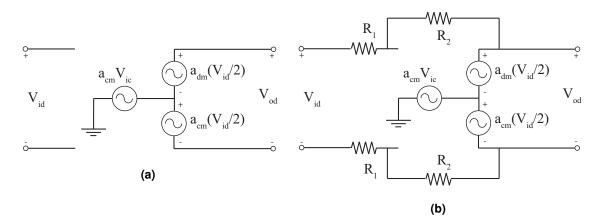

Now, consider also the circuit of Figure 2.22, where  $V_n$  is a noise voltage that is coupled to each of the amplifier inputs by the parasitic capacitances  $C_{ip}$ . With this configuration, each input has an equal signal applied, therefore the CM input voltage suffers from disturbances. Since both input noise signals are equal, they cause an equal drain current variation in  $M_1$  and  $M_2$ , leading to equal variations in  $V_{OP}$  and  $V_{ON}$ , respectively, which results in a zero differential output signal, if the amplifier is perfectly balanced. This means that the amplifier has zero CM gain and that this disturbance does not affect the CM output voltage [12]. In the case of the CM gain is nonzero but small, the CM voltage is affected, but the differential voltage is not, as long as the circuit is balanced. If that is not the case (for example, the parasitic capacitances are not matched), the output differential voltage is affected. For this reason, it can be noticed that a fully-differential amplifier has a CM gain  $a_{cm}$  and a differential gain  $a_{dm}$ , which are independent, if the circuit is balanced, that is the Differential-Mode (DM) output is only proportional to the DM input and the CM output is only proportional to the CM input. Hence, a simple small-signal model for this amplifier can be derived, as shown in Figure 2.23(a).

Figure 2.23: Small-signal model of a fully-differential amplifier: (a) open-loop configuration; (b) close-loop configuration.

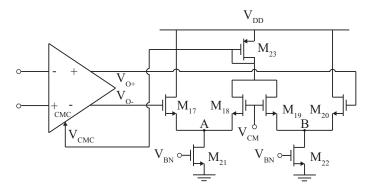

#### Common-mode Feedback

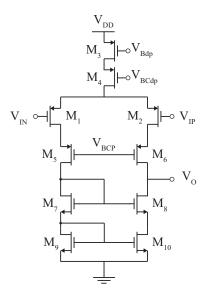

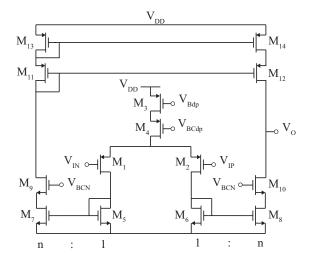

As previously discussed, a fully-differential amplifier possesses a CM gain and a DM gain, which are independent, as seen in Figure 2.23. If the amplifier is ideal,  $a_{cm} = 0$ ,  $a_{dm} = -\infty$ , which means that the CM output is zero for a finite input CM signal and the closed-loop DM gain is given by  $-R_2/R_1$ , as expected. This means that, while the DM output signal is well determined by the input DM signal, the CM input signal exerts little or no control in the CM output voltage  $V_{OCM}$ , since amplifiers have a very small CM gain,  $a_{cm}$  [12]. For all transistors to operate in saturation and maximize the output swing, a constant CM output voltage  $V_{OCM}$  must be applied. As the CM input voltage is not capable to control the output, an addition feedback path must be used in order to control the CM output voltage  $V_{OCM}$ , the Common-Mode Feedback (CMFB).

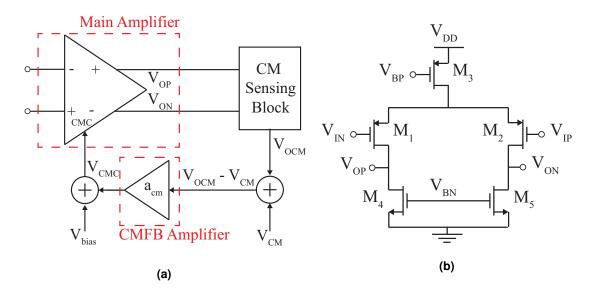

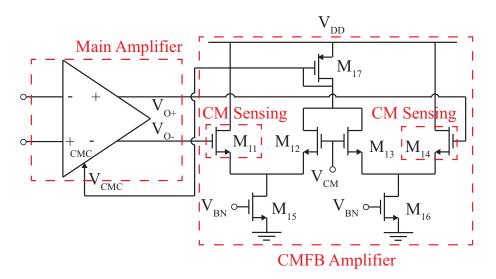

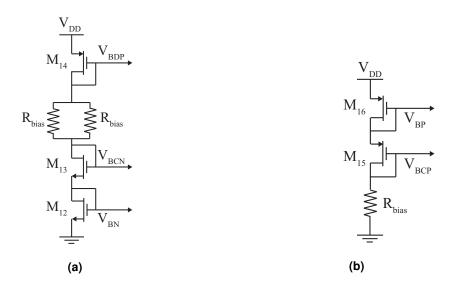

As seen from Figure 2.24(a), the CMFB is composed by a CM sensing block and a CMFB amplifier and employs a negative feedback to set  $V_{OCM}$  to a desired value,  $V_{CM}$ , by adjusting  $V_{BP}$  or  $V_{BN}$  of the amplifier of Figure 2.24(b). In this case,  $V_{BP}$  will be adjusted to make  $I_{D3} = |I_{D4}| + |I_{D5}|$  when  $V_{OCM} = V_{CM}$ .

The CM sensing block calculates the CM output voltage  $V_{OCM}$  as  $(V_{OP}+V_{ON})/2$ . This voltage is then compared with the desired CM voltage and the difference is amplified. Then, a biasing voltage is added (the voltage needed to correctly bias  $M_3$ , that is  $V_{BP}$ ) and the control signal  $V_{CMC}$ , which is given by

$$V_{CMC} = a_{cm}(V_{OCM} - VCM) + V_{bias},$$

(2.36)

Figure 2.24: CMFB: (a) the top-level diagram; (b) the main amplifier circuit.

is fed into the amplifier, specifically the gate of  $M_3$ . If the CMFB gain is high enough, the negative feedback will force  $V_{OCM} \approx V_{CM}$  and  $V_{CMC} \approx V_{bias}$ . Usually the gain from the CM control port, CMC, is much greater than unity, since it can be seen as the gain of a common-source, formed by  $M_3$ , with a large output resistance, and it is enough to provide all the gain needed in the CMFB loop, which allows  $a_{cm}$  to be small, thus having a larger bandwidth [12]. Two ways of implementing the CMFB are explained, whose main differences are in the way of sensing the output CM of the main amplifier.

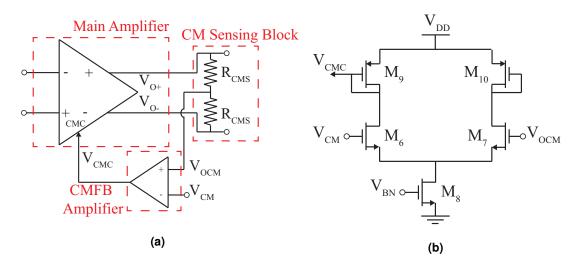

#### CM Sensing with Resistive Voltage Divider

One of the most simple ways to implement a CMFB circuit is by using a single-ended CMFB amplifier and a resistive voltage divider as a CM detector, as shown in Figure 2.25(a). The output CM voltage  $V_{OCM}$ , which is given by  $(V_{OP} - V_{ON}) \frac{R_{CMS}}{R_{CMS} + R_{CMS}} = \frac{V_{OP} - V_{ON}}{2}$ , is compared with the desired voltage  $V_{CM}$ , generating a control voltage that will bias  $M_3$  (Figure 2.24(b)) and adjusting the output CM. The CMFB amplifier circuit is shown in Figure 2.25(b) and it is composed by a differential pair and two diode-connected PMOS transistors as load. The difference between  $V_{OCM}$  and  $V_{CM}$  will unbalance the differential pair in such a way that if  $V_{CM} > V_{OCM}$ , the drain current of  $M_9$  will increase, as well as its source to gate voltage  $V_{SG9}$ . This voltage, when applied to the gate of  $M_3$  (Figure 2.24(b)) will cause an increase of the tail current of the amplifier, increasing  $V_{OCM}$ . If  $V_{CM} < V_{OCM}$ , the drain current of  $M_9$  decreases (Figure 2.25(b)) and, consequently,  $V_{SG9}$ , decreasing the amplifier tail current, which will bring  $V_{OCM}$  down.

By using CM sensing resistors,  $R_{CMS}$ , the DM output of the amplifier is loaded [12], as the node between resistors is an AC ground. This loading reduces the open-loop DM gain except if  $R_{CMS}$  is much larger than output DM resistance of the amplifier. The usage of resistors also

Figure 2.25: A CMFB scheme: (a) complete circuit; (b) the amplifier.

requires that they have large resistance values to ensure that the output current flows to the next stage and not to those resistors. To avoid the resistive loading, modifications to the circuit of Figure 2.25(a) can be made, for example adding buffers between the outputs and the resistors or controlling  $V_{OCM}$  by injecting currents into the amplifier, which will adjust the both CM outputs [12].

#### **CM Sensing with Differential Pairs**

A CMFB circuit that uses two differential pairs for CM sensing and amplification is shown in Figure 2.26.

Figure 2.26: A top-level CMFB diagram.

In this circuit, transistors  $M_{11-14}$  are matched and they form two differential pairs, that sense the CM output  $V_{OCM}$  and generate a control voltage  $V_{CMC}$ , which is proportional to  $V_{OCM}$  –

$V_{CMC}$ . Using a small-signal analysis and assuming that the CM gain of these pairs is zero, the drain currents of  $M_{12}$  and  $M_{13}$  are respectively given by

$$I_{D12} = \frac{I_{D15}}{2} + g_{m12} \frac{(V_{O-} - V_{CM})}{2}$$

(2.37)

and

$$I_{D13} = \frac{I_{D16}}{2} + g_{m13} \frac{(V_{O+} - V_{CM})}{2}.$$

(2.38)

These currents are summed in the diode-connected transistor  $M_{17}$ . Assuming that  $M_{15}$  and  $M_{16}$  are matched, the CM control current  $I_{CMC}$  is given by

$$I_{CMC} = I_{D17} = I_{D15,16} + g_{m12,13} \left( \frac{V_{O+} - V_{O-}}{2} - V_{CM} \right)$$

=  $I_{D15,16} + g_{m12,13} \left( V_{OCM} - V_{CM} \right).$  (2.39)

From (2.39), it can be noticed that  $I_{CMC}$  is composed by a DC component and a term proportional to  $V_{O+} + V_{O-}$ . This current is mirrored to  $M_3$  (Figure 2.24(b)), which will produce the amplifier tail current. If  $V_{OCM} = V_{CM}$ , the tail current is simply equal to  $I_{D15,16}$ , which should be the nominal tail current set upon design.

This circuit does not resistively loads the amplifier but transistors  $M_{11,14}$  have parasitic capacitances that increase the total output capacitance of the amplifier. Also, as this analysis was made assuming only small signals, this CMFB circuit will not properly function if the outputs are large enough to turn off any of  $M_{11-14}$  transistors. For this reason, their overdrive voltages must be increased.

To implement the fully-differential pre-amplifier, the CMFB that uses two differential pairs will be used to correctly set the amplifier output CM voltage.

# 2.6 DC Suppression

An important feature of circuits used for sensor reading is the capability to block the sensors biasing signals, which are usually DC signals, up to a few hundred of mV in amplitude. Furthermore, the sensors used present offsets which, adding to the biasing signals, can easily saturate the amplifiers. Therefore, there is the need of achieving a high-pass characteristic in order to eliminate the unwanted quantities [10] [13] [14].

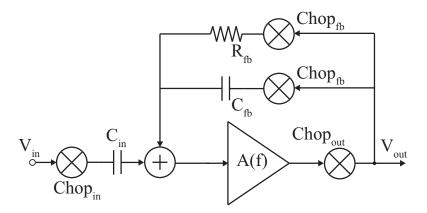

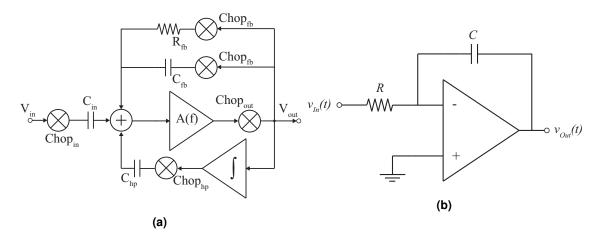

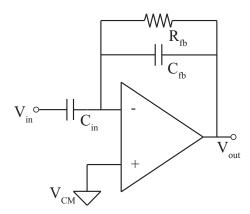

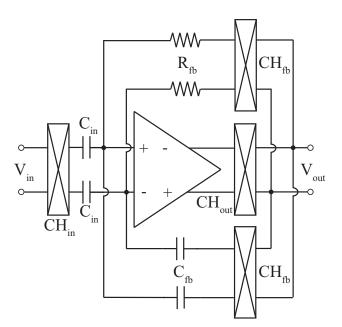

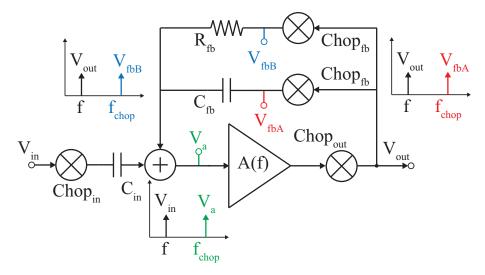

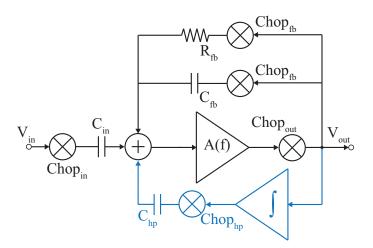

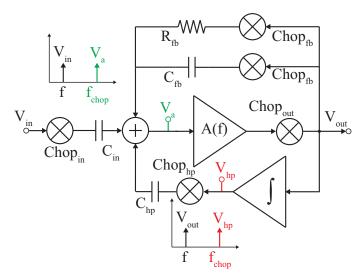

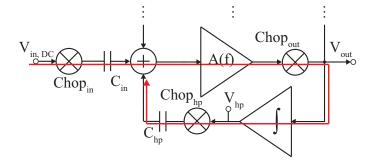

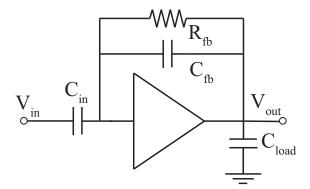

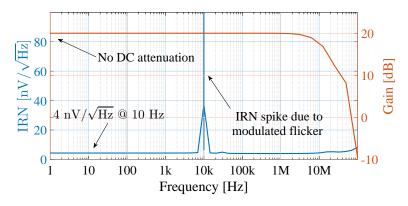

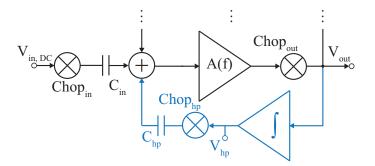

In this work, MR sensors are used and they are biased by a DC current, so that variations in its resistance can be measured. This means that the signal coming from the sensors has a significant DC component. Several solutions to achieve DC suppression are possible, like the one implemented in [13], where a Capacitively Couple Chopper Instrumentation Amplifier (CCCIA) is implemented, which is composed by a folded cascode amplifier with a capacitive feedback path and chopper modulators (Figure 2.27). Its band-pass gain is given by  $C_{in}/C_{fb}$ , where  $C_{fb}$  and  $C_{in}$  are the feedback and input capacitance values, respectively.

Figure 2.27: Block diagram of a CCCIA.

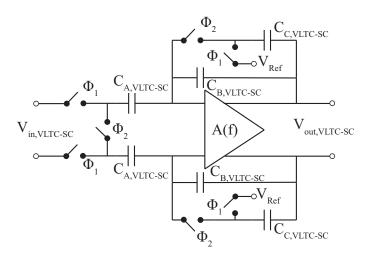

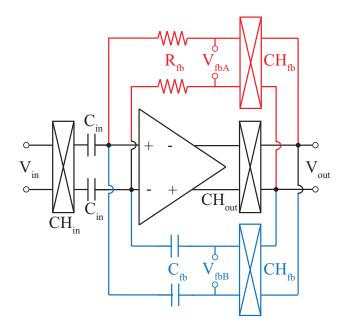

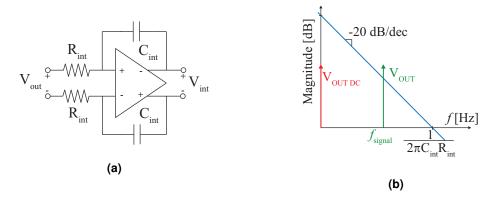

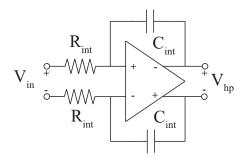

As Chopper Stabilization is implemented, due to the action of the input modulator  $Chop_{in}$ , the DC component is modulated to the chopper frequency  $f_{chop}$ , therefore is not blocked by the input capacitor  $C_{in}$  (Figure 2.27). To block the up-modulated DC, a new feedback path is added (Figure 2.28(a)), consisting of an inverting integrator (Figure 2.28(b)) that has a low-pass characteristic, amplifying only the DC at the output of the system. Then, the DC component is up-modulated to the chopper frequency  $f_{chop}$ , so that it can be subtracted from the signal at the virtual ground nodes of the amplifier. This implementation is called DC Servo Loop (DSL). Since the goal is to eliminate only the DC component, the high-pass pole of the system must be placed at a frequency  $f_{hp}$  lower than the input signal lowest frequency, in order to not affect it.

Figure 2.28: The DSL: (a) in the CCCIA; (b) integrator implementation.

For low-frequency applications, where input signal frequencies can be as low as 1 Hz, the pole of the integrator must be placed at a frequency  $f_{int}$  close to DC to force the frequency of the high-pass pole of the system  $f_{hp}$  to be lower than the minimal signal frequency. The frequency of the pole of the integrator,  $f_{int}$ , can be adjusted by changing its unity-gain frequency,  $f_{0,int}$ , which is given by

$$f_{0,int} = \frac{1}{2\pi} \frac{1}{CR}$$

(2.40)

where *R* and *C* are the values of the resistor and capacitor of the integrator of Figure 2.28(b). The unity-gain frequency of the integrator  $f_{0,int}$  relates to the frequency of the high-pass pole  $f_{hp}$  of the circuit as follows:

$$f_{hp} = \frac{C_{hp}}{C_{fb}} f_{0,int},$$

(2.41)