## **CAD: AIDA-TOP - Analog IC Topology Selection**

### João Maria Lobo Moutinho Soares de Melo

Thesis to obtain the Master of Science Degree in

## **Electrical and Computer Engineering**

Supervisors: Prof. Nuno Cavaco Gomes Horta Prof. Ricardo Filipe Sereno Póvoa

### **Examination Committee**

Chairperson: Prof. Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Prof. Nuno Cavaco Gomes Horta Members of the Committee: Prof. Rui Santos Tavares

July 2020

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

## Acknowledgements

It is impossible to thank all the important people that helped me during my master's degree in electrical engineering. Directly or indirectly, many people allowed the conclusion and enjoyment of this stage of my life and I will be forever thankful.

To my supervisor Ph. D. Nuno Horta for his guidance and help. To my co-supervisor Ricardo Póvoa who went above and beyond his duty in his support. My gratitude to ICG team, António Canelas for his diligent support, as well as to Ricardo Martins and Nuno Lourenço.

To my Técnico friends, to all my closest friends, and to my family, all of whom I shared many great moments with and that were always there for me. In particular I would like to thank those that had a special role throughout the completion of this dissertation, Daniel Farinha, João Ferreira, João Caeiro, Rita Mourão, José Mourão, Rita Lopes Mourão, my uncle Pedro Medeiros, my sister Luísa, and Monika Luśnia.

Finally, but not least to my parents, who always did everything in their power to provide me an extraordinary life.

This work was developed at Instituto de Telecomunicacoes and was funded by FCT/MCTES through national funds and when applicable co-funded EU funds under the project UIDB/EEA/50008/2020.

### Resumo

Esta tese de mestrado descreve o desenvolvimento de uma metodologia de selecção de topologias altamente customizável, independente da tecnologia, compatível com a ferramenta AIDA-C. A síntese de topologias é um passo essencial no decorrer do projecto de circuitos, maioritariamente dependente do conhecimento de desenhadores experientes. Criar uma ferramenta de EDA para realizar esta tarefa melhoraria substancialmente o *time-to-market*, visto que muitos outros elementos do projecto de circuitso já se encontram automatizados. O método escolhido recorre à informação de optimizações de dimensionamento anteriores, combinando-as com algoritmos de MCDM para obter a topologia mais apta, quer haja um circuito que já alcance os valores pedidos, ou caso não haja nenhum que o faça.

O método de selecção de topologias foi implementado no programa AIDA-TOP. Foi testado recorrendo a optimizações do AIDA-C de quatro topologias distintas, pertencentes à família OTA CMOS. A progressão do programa foi verificada usando variados exemplos de input. A ferramenta usou 40 optimizações de teste, cada uma contendo múltiplos circuitos simulados, atingindo 76,41% de taxa de acerto geral.

## Palavras-chave

Projecto de circuitos analógicos; Síntese topológica; Automação de Projecto Electrónico; Selecção Topológica; Optimização Multiobjectivo; Análise de decisão multicritério.

## Abstract

This Master thesis describes the development of a technology independent, highly customizable topology selection methodology compatible with AIDA-C. Topology synthesis is an essential step in circuit design, majorly dependent on the knowledge of experienced designers. Producing an EDA tool in this task of a circuit's design flow would drastically improve its time-to-market, since many other elements in this flow are already automated. The method chosen uses the information of past sizing optimizations, combining them with MCDM algorithms to get the most apt topology. It does so if there exists an optimized circuit able to reach the desired performances, or otherwise.

The topology selection method was implemented as the AIDA-TOP program. It was tested using AIDA-C optimizations of four distinct topologies, belonging to the CMOS OTA family. The program was verified to progress as expected with diverse input examples. The tool used 40 test optimizations with multiple simulated circuits each to arrive at an overall accuracy rate of 76,41%.

## Keywords

Analog circuit design; Topology Synthesis; Electronic Design Automation; Topology Selection; Multi-objective optimization; Multi-criteria decision analysis.

# Contents

| Ac  | knowle    | edgements                             | .i |

|-----|-----------|---------------------------------------|----|

| Re  | esumo     |                                       | ii |

| Ab  | ostract.  |                                       | ii |

| Lis | st of Fig | guresi                                | х  |

| Lis | st of Ta  | bles                                  | х  |

| Ac  | ronym     | S                                     | ĸi |

| 1   | Intro     | duction                               | 1  |

|     | 1.1       | Motivation                            | 1  |

|     | 1.2       | Analog IC Design flow                 | 3  |

|     | 1.3       | Topology level automation             | 6  |

|     | 1.4       | Objectives                            | 7  |

|     | 1.5       | Document structure                    | 7  |

| 2   | Prev      | ious Works                            | 9  |

|     | 2.1       | Topology Selection vs Generation      | 9  |

|     | 2.2       | Chronological review                  | 0  |

|     | 2.2.1     | 1 Manual CAD 1                        | 0  |

|     | 2.2.2     | 2 Hierarchical view1                  | 1  |

|     | 2.2.3     | 3 Knowledge-Based implementation 1    | 3  |

|     | 2.2.4     | 1 Joint design stages 1               | 4  |

|     | 2.2.5     | 5 Improvement of overall performance1 | 4  |

|     | 2.2.6     | 6 Automating knowledge 1              | 6  |

|     | 2.2.7     | 7 Fixed Single Objective 1            | 7  |

|     | 2.2.8     | 3 Evolutionary Algorithms 1           | 8  |

|     | 2.2.9     | 9 Mutable Objective 2                 | 0  |

|     | 2.2.1     | 10 Circuit evaluation                 | 0  |

|     | 2.2.1     | 11 Classes of EAs 2                   | 1  |

|     | 2.2.1     | 12 Genetic Programming 2              | 1  |

|     | 2.2.1     | 13 Multi-objective Optimization (MOO) | 3  |

|   | 2.2.1 | 4     | NSGA-II                         | . 24 |

|---|-------|-------|---------------------------------|------|

|   | 2.2.1 | 5     | Causal synthesis                | . 25 |

|   | 2.2.1 | 6     | Conceptual View                 | . 26 |

|   | 2.2.1 | 7     | Hybrid Generation and Selection | . 26 |

| 2 | 2.3   | Cate  | egorization of solutions        | . 27 |

| 2 | 2.4   | Wor   | rk Proposal                     | . 32 |

| 3 | Syste | em A  | rchitecture                     | . 33 |

| : | 3.1   | Intro | oduction                        | . 33 |

| : | 3.2   | Тор   | ology library                   | 35   |

| : | 3.3   | Mod   | dules                           | . 35 |

|   | 3.3.1 | R     | elevant Data Filter             | . 35 |

|   | 3.3.2 | 2 F   | easible Solution Finder         | . 37 |

|   | 3.3.3 | 8 P   | areto Reformation               | . 38 |

|   | 3.3.4 | L T   | OPSIS                           | . 39 |

|   | 3.3.5 | 5 C   | losest Topology Calculator      | . 42 |

|   | 3.3.6 | 6 F   | arthest Topology Calculator     | . 45 |

| 4 | Test  | Libra | ary                             | . 47 |

| 4 | 1.1   | Intro | oduction                        | . 47 |

| 4 | 1.2   | Test  | t Library content               | . 47 |

|   | 4.2.1 | Μ     | leasures                        | . 48 |

|   | 4.2.2 | 2 C   | Fircuits                        | . 50 |

| 4 | 1.3   | Libra | ary Implementation              | . 54 |

| 4 | 1.4   | Opti  | imizations                      | . 55 |

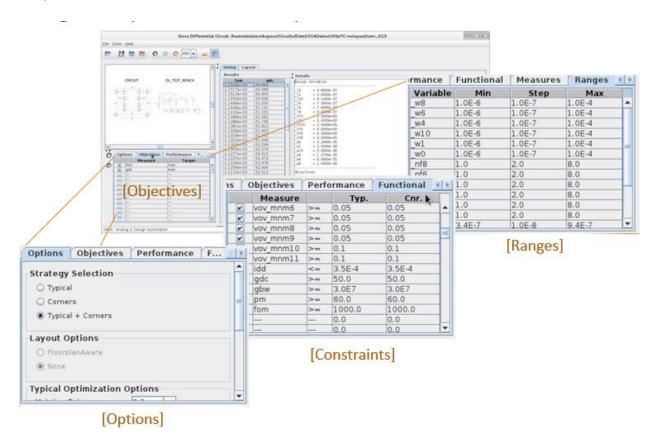

|   | 4.4.1 | A     | IDA-C                           | . 55 |

|   | 4.4.2 | 2 S   | earch Space and Constraints     | . 57 |

|   | 4.4.3 | 3 0   | Dutput file                     | . 58 |

|   | 4.4.4 | l Li  | ibrary Paretos                  | . 58 |

| 5 | Test  | s and | d results                       | 61   |

| į | 5.1   | Test  | t Set                           | . 61 |

|     | 5.2            | Model validation | 63 |  |

|-----|----------------|------------------|----|--|

|     | 5.2.1          | Closest topology | 63 |  |

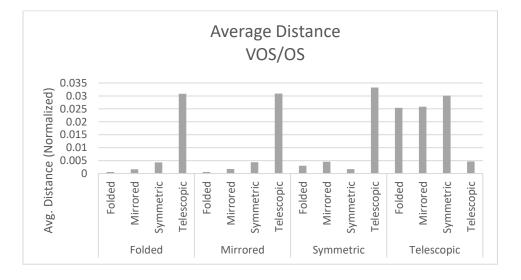

|     | 5.2.2          | Average Distance | 65 |  |

| 6   | Cond           | clusions         | 69 |  |

|     | 6.1            | Conclusion       | 69 |  |

|     | 6.2            | Future work      | 70 |  |

| Bil | Bibliography71 |                  |    |  |

# List of Figures

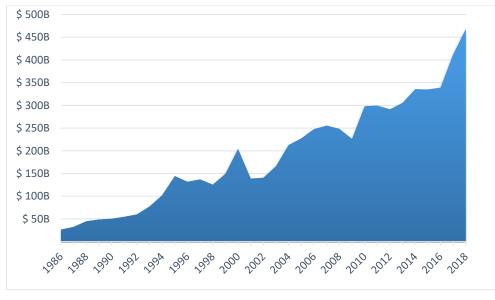

| Figure 1.1 - Semiconductor Billings from 1986 until present.[1][2]                                          | 1      |

|-------------------------------------------------------------------------------------------------------------|--------|

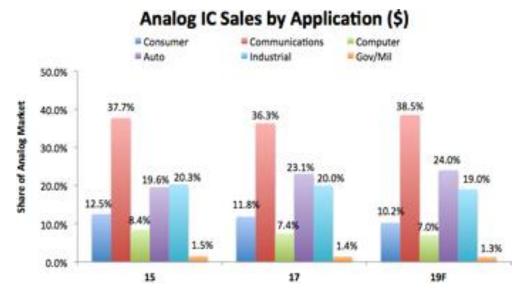

| Figure 1.2 – Analog IC Sales by application in percentage of revenue, from 2015 to 2019 forecast. [7]       | 3      |

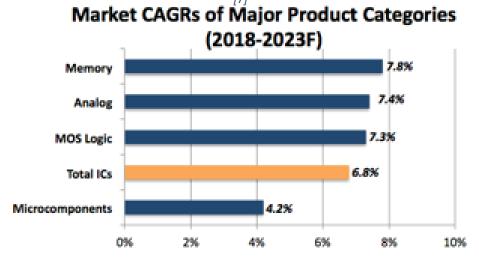

| Figure 1.3 – Expected growth of product categories from 2018 to 2023. [7]                                   | 3      |

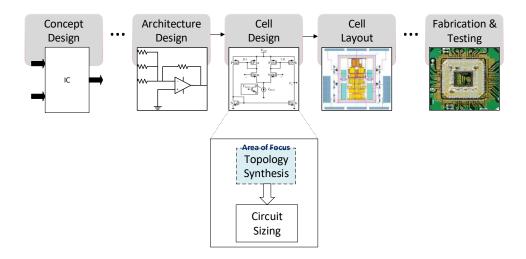

| Figure 1.4 - Design Flow diagram exalting the area this work focuses on (Topology Synthesis)                | 5      |

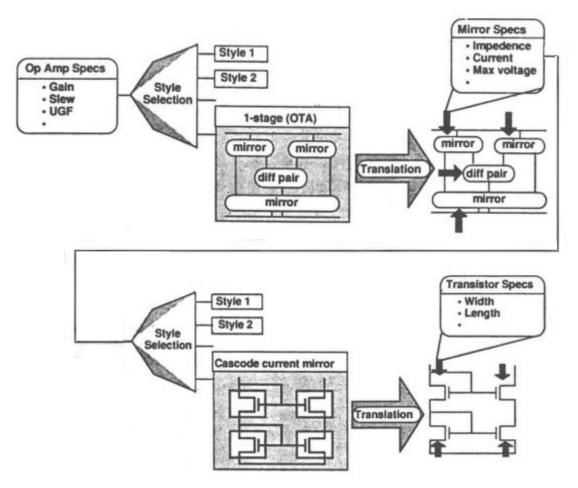

| Figure 2.1 – Two-layer Translation and Style Selection steps for opamp design. [21]                         | 13     |

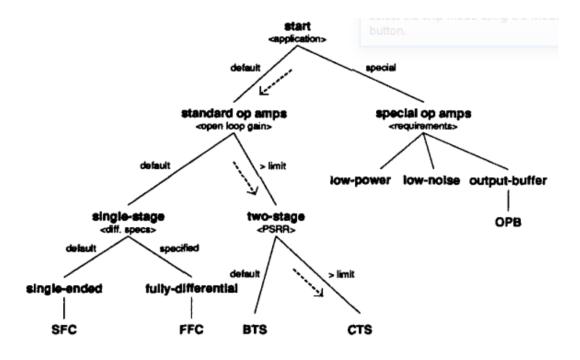

| Figure 2.2 - OPASYN decision tree. [22]                                                                     | 15     |

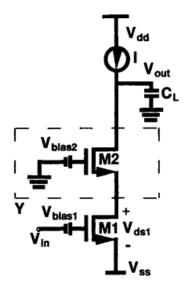

| Figure 2.3 – Common-source amplifier with variable Y controlling the presence of a cascode                  | 17     |

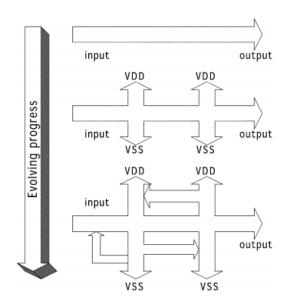

| Figure 2.4 – Effect of evolving functions.                                                                  | 22     |

| Figure 2.5 - Pareto Front example.                                                                          | 24     |

| Figure 2.6 – Pseudocode from [31] with the NSGA-II main loop                                                | 25     |

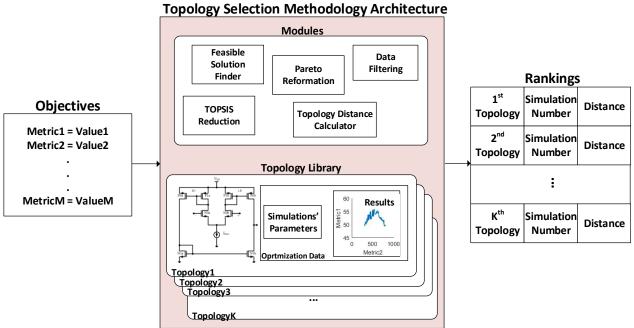

| Figure 3.1- Topology Selection Methodology Architecture.                                                    | 33     |

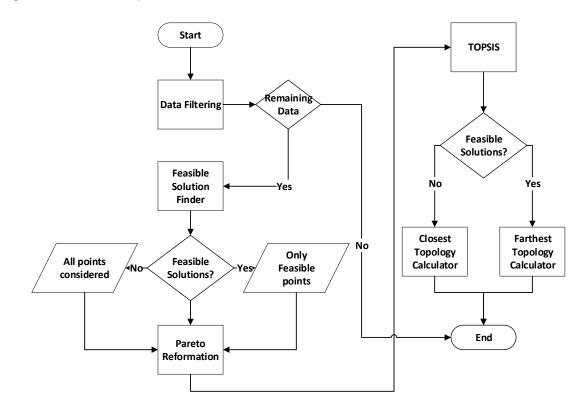

| Figure 3.2 - Module sequence in Topology Selection Methodology.                                             | 34     |

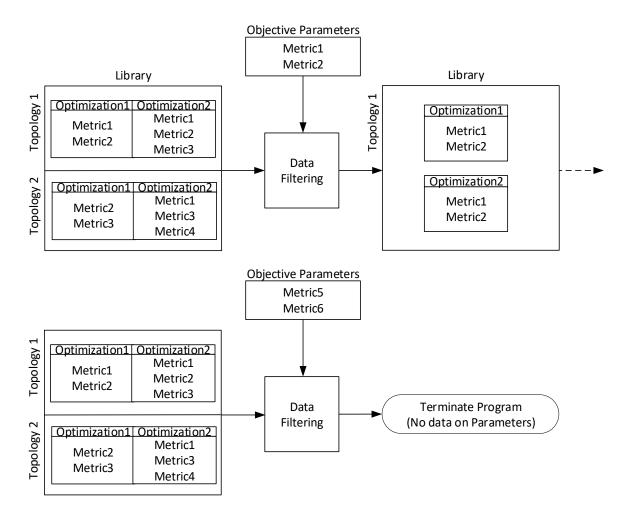

| Figure 3.3 - Data Filtering Module.                                                                         | 36     |

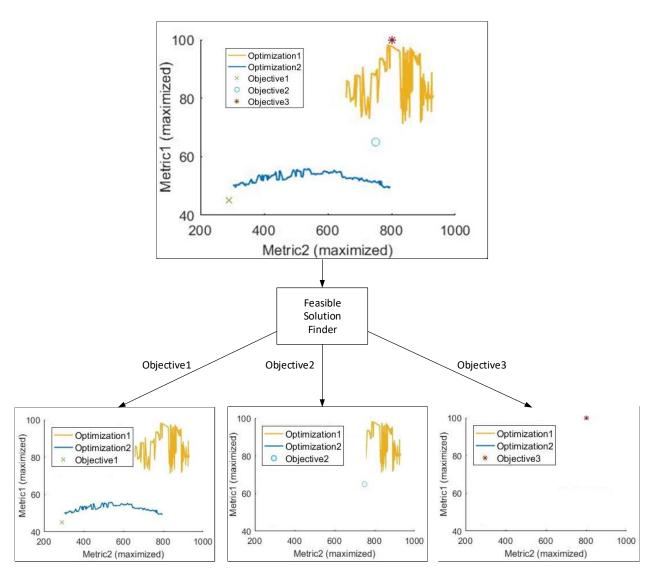

| Figure 3.4 – Feasible Solution Finder module examples.                                                      | 37     |

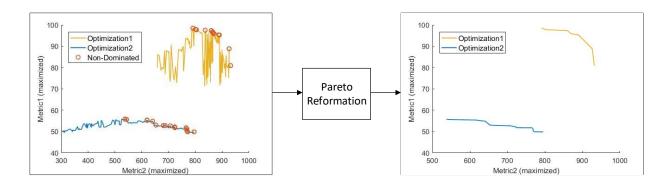

| Figure 3.5 - Pareto Reformation Module                                                                      | 39     |

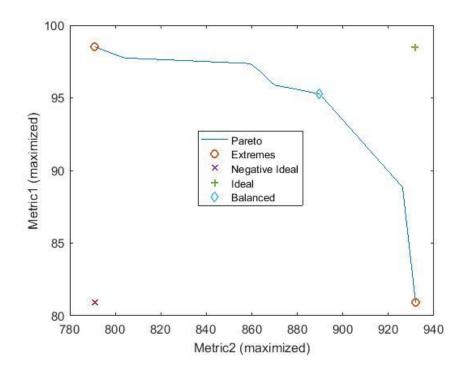

| Figure 3.6 - Example of the points selected by the TOPSIS algorithm in a pareto,                            | 42     |

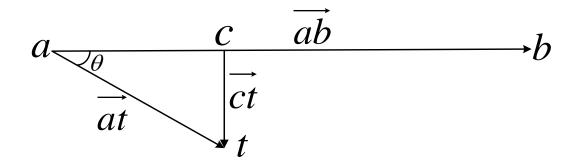

| Figure 3.7 – Geometric scheme of line-point distance                                                        | 43     |

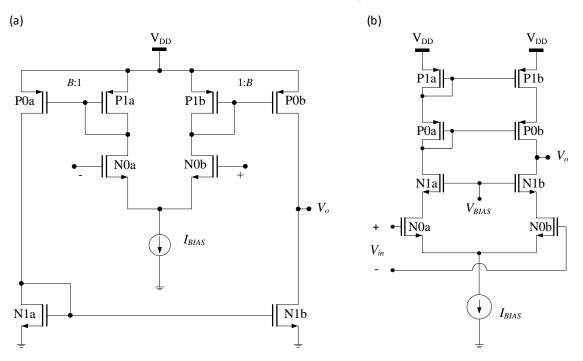

| Figure 4.1 – Two CMOS OTAs chosen for testing: (a) Symmetrical (b) Telescopic-Cascode                       | 50     |

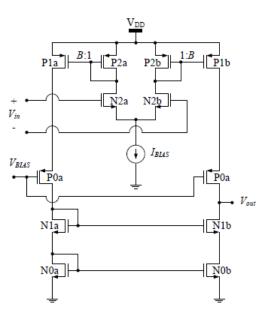

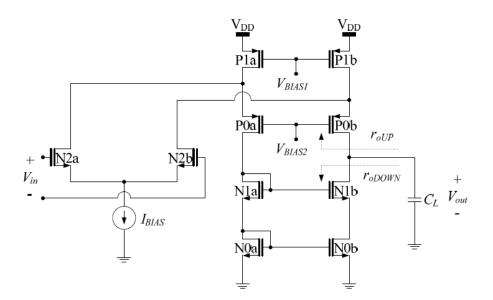

| Figure 4.2 - Mirrored-Cascode Amplifier.                                                                    | 52     |

| Figure 4.3 - Folded-Cascode Amplifier                                                                       | 53     |

| Figure 4.4 – Sample of AIDA-C input XML                                                                     | 55     |

| Figure 4.5 – AIDA-C GUI                                                                                     | 56     |

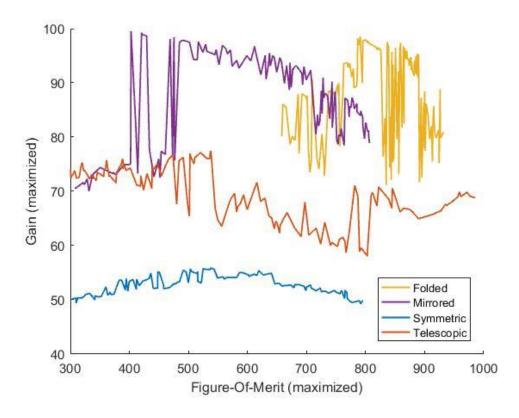

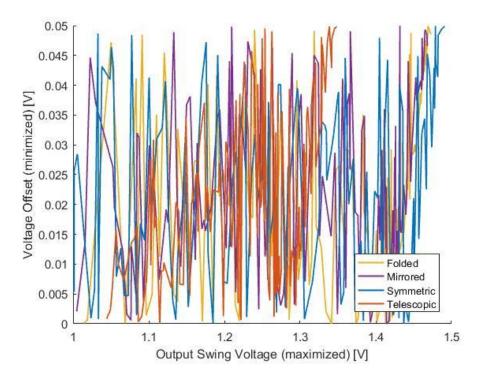

| Figure 4.6 - Projection of FOM and Gain output from 4000 generations of AIDA optimizations                  | 59     |

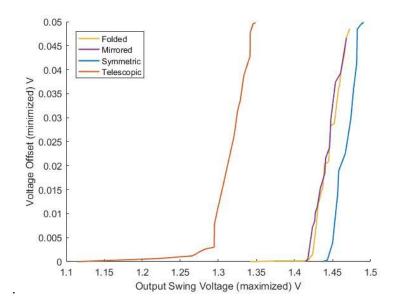

| Figure 4.7 - Projection of VOS and OS output from 4000 generations of AIDA optimizations                    | 59     |

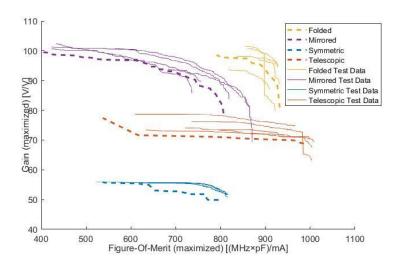

| Figure 5.1 - Two objective optimization for Gain and FOM side-by-side with view of four objective p         | areto  |

| reformed into the same two objectives                                                                       | 61     |

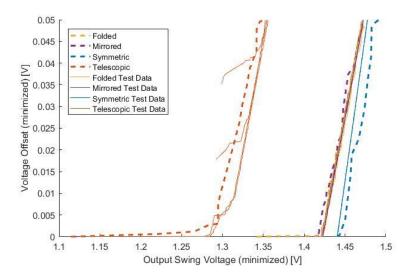

| Figure 5.2 - Two objective optimization for OS and VOS side-by-side with view of four objective p           | areto  |

| reformed into the same two objectives                                                                       | 62     |

| Figure 5.3 - 4 objective library reforned pareto for OS and VOS objectives.                                 | 63     |

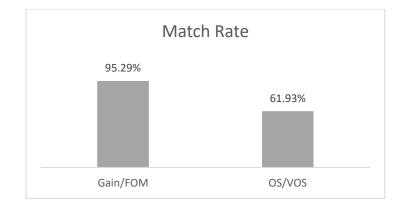

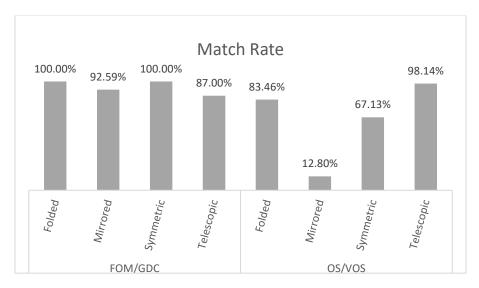

| Figure 5.4 – Match Rate on the two objective pairs available (1) Gain/Fom and, (2) OS, VOS                  | 64     |

| Figure 5.5 - Matching percentage in both objective pairs, per topology                                      | 65     |

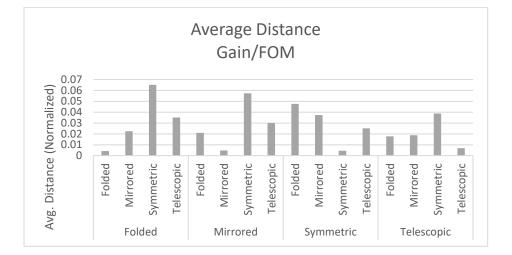

| Figure 5.6 - Average distance grouped by topology of test points to library topologies for Gain/FOM obje    | ective |

| pair                                                                                                        | 67     |

| Figure 5.7 - Average distance grouped by topology of test points to library topologies for VOS/OS objection | ective |

| pair                                                                                                        | 67     |

## List of Tables

| Table 2.1 – Evolutionary Algorithm Loop            | . 18 |

|----------------------------------------------------|------|

| Table 2.2 - Classification of previous works.      | . 29 |

| Table 3.1 - Pareto reformation algorithm           | . 38 |

| Table 3.2 - TOPSIS algorithm.                      | . 41 |

| Table 3.3 - Topologies distance sorting algorithm. | . 44 |

| Table 4.1 - Relative performance of circuits       | . 53 |

| Table 4.2 - Output signal swing expressions        | . 53 |

| Table 4.3 - Transistor dimension possible values.  | . 57 |

| Table 4.4 - Topology number of dimension variables | . 57 |

| Table 5.1 – Prediction break down by optimization  | . 66 |

| Table 6.1 – AIDA-TOP Classification                | . 69 |

# Acronyms

| ADC     | Analog to Digital Converter                       |

|---------|---------------------------------------------------|

| AMS     | Analog or Mixed Signal                            |

| ASIC    | Application Specific Integrated Chip              |

| CAD     | Computer-Aided Design                             |

| CMOS    | Complementary Metal-Oxide-Semiconductor           |

| EA      | Evolutionary Algorithm                            |

| EDA     | Electronic Design Automation                      |

| GA      | Genetic Algorithm                                 |

| GP      | Genetic Programming                               |

| GUI     | Graphical User Interface                          |

| HDL     | Hardware Description Language                     |

| IC      | Integrated Circuits                               |

| IOT     | Internet of Things                                |

| KCL     | Kirchhoff's' Current Laws                         |

| KVL     | Kirchhoff's' Voltage Laws                         |

| MCDM    | Multi Criteria Decision Makers                    |

| MINLP   | Mixed Integer NonLinear Programing                |

| MODA    | Multi-Objective Decision Algorithms               |

| MOEA    | Multi-Objective Evolutionary Algorithm            |

| MOO     | Multi-Objective Optimization                      |

| MOSFET  | Metal–Oxide–Semiconductor Field-Effect Transistor |

| NSGA-II | Nondominated Sorting Genetic Algorithm II         |

| OPAMP   | Operational Amplifier                             |

| OS      | Output Swing Voltage                              |

- OTA Operational Transconductance Amplifiers

- POF Pareto-Fronts

- PSSR Power Supply Rejection Ratio

- SoC System on Chip

- SPICE Simulation Program with Integrated Circuit Emphasis

- TOPSIS Technique For Order of Preference by Similarity to Ideal Solution

- VOS Offset Voltage

## 1 Introduction

This chapter is an overview on the of the work that has been done, laying out the reasons for its conception and the goals it sets to reach, while defining its place amongst the existing solutions. Then, it presents the document's structure, showing its logical flow, with the additional benefit of making it more searchable.

## 1.1 Motivation

Electronic circuits flood the contemporary world, taking part in our day-to-day, in a great variety of ways. In their infancy they existed scarcely as a tool to propel new means of communication, having grown with the appearance and popularization of radios, telephones, and televisions. With the invention of the transistor, and the ability to integrate it in large numbers into a semiconductor made integrated chip (IC), their adoption became mainstream. ICs have a cheap and reliable production method, making them ideal for mass production. This revolution made products such as computers, mobile phones and home appliances available for most consumers and infiltrated most areas of professional activity. To understand the magnitude of this expansion it can be observed, in Figure 1.1, that the semiconductor market worth grew from \$20 billion to \$480 billion [1], [2](approximately), from 1986 to 2018, sustaining the success of multiple companies amongst the most profitable ones in the world.

Figure 1.1 - Semiconductor Billings from 1986 until present.[1][2]

At first, the symbolic representation (schematic) and the physical implementation (geometric blueprint, also called layout) could be made manually. The number of devices that an integrated circuit contained grew exponentially, making it to dozens of billions nowadays [3], soon making their hand conception unviable, due to the number of devices and the precision required. Besides, the testing and correction of a circuit might require a long time and bear great costs.

Computer-aided design (CAD) surfaced to improve electronic design automation (EDA), facilitating the creation of circuits, in all its sectors from tools that ensure and implement logic, to ones that implement the physical circuit construction and verification of the layouts for fabrication. In the last 20 years processors, memories, digital and mixed-signal blocks etc. have been relegated to a single silicon substrate, the system on chip (SoC) that, on the digital front, often resorts to the reuse of blocks[4]. These blocks are application specific ICs (ASICs), cells that were standardized for a certain functionality. This uniformization made it possible to develop higher abstraction level, leading to the inception of hardware description languages (HDL), who are, through logic synthesis, converted in schematics. [5]

Such mechanisms, that greatly increased productivity, have not been employed in analog or mixed-signal circuits (AMS). This lack of libraries constituted by standard cells is one of the reasons why, despite the relatively small proportion of analog circuits in electronic devices, their design is more complicated than the digital counterpart. Complexity in analog circuits stems from the intricate relations between devices, and performance goals and specifications being continuous.[6] This trait means that they are more easily impacted by interference brought by the constant reduction in chip sizes. Moreover, digital circuits are, by nature, improved with the amount of computation power, directly linked to the number of transistors. In the AMS world, this is not applicable, removing relevance of standard cells and, consequently, from the description languages that can be originated.

The present difficulty in the development of AMS circuits, is a threat to product life cycles due to the increasing time-to-market-constraints. Furthermore, the task is resource intensive, especially in human form, since it relies on analog designers, who must be highly trained. Due to the continuous nature of the "real world", AMS circuits emerge as a necessity to interface with digital systems. This connection not only makes them indispensable, but also intimately links the successes of IC and semiconductor market, with the ability to produce this category of circuits.

Figure 1.2 shows the largest grossing applications for analog ICs. A growing trend in the automotive application is visible, propelled by the investment in driving cooperation and autonomy, requiring a large number of sensors to make it possible. Communications have been this industry's biggest sector and are predicted to continue leading it. These factors, in conjunction with up-and-coming technologies, like the Internet of Things (IoT), leave optimistic prospects for the analog market, as shown in Figure 1.3. This figure displays the compound annual growth rate (CAGR), a business measure of cumulative growth, in this case from 2018 to 2023. In comparison to other device types within the semiconductor industry, analog ones are forecasted to have second largest rate until 2023 (7.4%), preceded only by memory devices (7.8%) [7]. The future interest in this type of circuits, and existing limitations to their conception, justify the importance of improving AMS IC design.

Figure 1.2 – Analog IC Sales by application in percentage of revenue, from 2015 to 2019 forecast.

Figure 1.3 – Expected growth of product categories from 2018 to 2023. [7]

### 1.2 Analog IC Design flow

The need for bettering the design of AMS circuits has been established. This subsection will focus on describing the chain of processes to create a circuit. It will examine the status of AMS EDA and delineate the portion chosen the for intervention of this work.

The set of actions that start with the concept for a circuit and end with the delivery of a physical circuit is its design flow. Due to the differences explained in the previous section, even though the AMS and digital components will integrate the same chip, they will have parts of their flow that are distinct. Because our focus is on the analog branch, the generally accepted [8] model for it, that was proposed by Gielen and Rutenbar in [9], defines the following stages:

- 1. **Concept design –** The behavioral description of the chip, and the qualitative specifications to be reached are outlined.

- System design Definition of hardware and software elements and their languages (if applicable). The intended behavior of hardware components is described, as are the interfaces. Choice of technology, packaging, and test strategy for verification, are analyzed, on the implementation viewpoint.

- Architectural design Construction of the hardware architecture from the highest-level perspective. Segmenting the architecture into interconnected functional blocks, distinguishing analog and digital elements, while ascribing requirements to all components.

- 4. Cell design After this step digital and analog design flows are not the same. Specification of analog blocks, detailing their topological design the devices (transistors, resistors etc.) composing the blocks and the way they are connected also attributing their parameters e.g. transistor physical dimensions, resistance of resistors. The latter activity is called circuit sizing.

- Cell layout Transformation of a sized electrical schematic into layout, geometrically parameterizing multiple layers, using the minimum area whilst avoiding parasitic effects that ruin performance.

- System Layout Create the higher-level layout that is reached by gathering all cells after they are defined, placing and routing them, putting together the IC. Establishes shielding mechanisms to guard from crosstalk and substrate noise coupling.

- 7. **Fabrication and Testing –** The molds that mirror the layout (masks) are generated and used to produce the ICs, the deliverable from the whole flow where the actual performance can be validated.

All the stages include simulation and validation to see if the requirements have been met. If in any of them are not met, it is possible to backtrack to a previous process, regressing in the flow, to correct mistakes or attempt alternative options.

This design flow for circuits represents a top-down approach, starting with an abstract perception of a full system, finishing with a concrete and detailed view. The higher levels (earlier stages) allow for a broader exploration of the search space, enabling a more varied gamut of circuits. For this conversion to happen, simplifications must be made about the components that integrate it, modeling their behavior. Models should sacrifice the minimum amount of accuracy whilst being as simple as possible, to allow rapid simulation. A model is deficient when: (1) it leads regularly to options that in lower layers will prove to be inaccurate, (2) is not simple enough. In both cases it will result in longer design times, by backtracking often in (1) and through excessive computational complexity in each run for (2).

To produce tools for higher levels, it is necessary to have sufficiently exact tools for the lower levels. Starting from the bottom, if fabrication and testing processes do not work properly, it is not feasible to extract, and model information to automate the chip's layout. The same is seen throughout the chain. So, if the layout

simulation is erroneous, the cell design will be as well. And if it is not automated, modifications in cell design, can require laborious layout redesign, due to the more concrete and detailed nature of this task.

The way EDA tools have developed supports this thesis. Initially came the automation of fabrication, which started in the 1960's [10]. The Cell Layout level has some solutions with commercial potential that start to surface (LAYGEN-II[11]), as does the sizing portion of Cell design (AIDA-CMK[12], Cadence's Virtuoso ADE GXLs[13], Synopsys' Titan ADX[14]) and some tools that already integrate both (AIDA[15]). However, when one examines the topological side of designing cells one confronts a task that still relies on graphical schematic entry tools, a manual chore relying on the expertise and time of highly trained analog designers. In view of this handicap, the current work proposes a methodology to improve the fourth stage of Cell Design. Namely, it is a proposal of a system to help in synthesizing a topology. Figure 1.4 provides a diagram view of the design flow pointing out the step where this project intervenes.

Figure 1.4 - Design Flow diagram exalting the area this work focuses on (Topology Synthesis).

Currently to get to a topology, an analog designer comes up with a schematic he finds to be likely to conform to the set objectives. This is done by using topologies that the designer has previously worked with, having acquired sensibility for their abilities, sometimes tweaking them to accommodate specifications that might be troublesome.

These topologies are often inserted, device by device, into a graphical schematic tool. Upon conclusion, the schematic can be input to sizing and layout tools, but at this point, the range of achievable performance specifications is much more narrow. For this reason, it is paramount, for successful circuit creation, that an adequate topology is chosen, as a failure to do so, limits the potential of a circuit drastically. If the topology is deemed unfeasible, redrawing is required, repeating the process until all goals are reached. The whole process is a time-consuming endeavor reliant on highly trained designers.

The integration of a tool that would automatically choose the schematic could, make this choice more efficient. Such a tool would automate the manual tasks and the expert knowledge involved, letting the expert designers focus on other tasks.

### 1.3 Topology level automation

This work intervenes in the first stage of cell design of electing a topology. It is a task of infinite possibilities, as it is possible to choose any number of components and combine them in different manners. It is further complicated by the strong effect and high variability that the devices parameters have.

To the action of experimenting combinations of elements roaming the design space coming up with atypical architectures the name of topology generation is given. This technique came up with the advent of genetic algorithms, allowing the creation of hundreds of thousands of unique structures[16]. Nevertheless, the portion of physically meaningful alternatives generated is minor, and the overhead of inspecting them reduces the attractiveness of this activity. Alternatively, with topology selection, tools often create a bank of solutions which designers know and understand, from which the tool chooses the one believed to have the largest potential to succeed. While selection began as the most popular approach, recently the trend has been to use the generation method.

Within these classifications, a wealth of ways to approach this problem have been attempted, some deficient due to excessive computational requirements, others due to the restrictive library, or due to the time necessary to compose a model. These libraries are largely sector dependent and reveal to be easily outdated by innovative technologies and designs. Recently a new paradigm was introduced where a balance between generation and selection is sought, originating new topologies exclusively if the library does not contain a viable solution. The strategy is explored by us is in topology selection.

To fill the breach in contemporary IC design, it is offered a methodology enabling the creation of a knowledge database (library), that can be customized with the most useful solutions for multiple sectors and uses. The hypothesis of using previous multi-objective optimizations is explored, to deduce which circuit can reach specifications currently required. To create that knowledge bank, Multi Criteria Decision Makers (MCDM) are adopted, summarizing the optimizations, into a smaller set of points that can describe them competently. Besides this functionality, an algorithm is described which will then parse through the stored information, selecting circuits that conform to the requirements of a newly asked circuit, suggesting the most flexible, performing topology. In case of not having a solution, the methodology uses the database to recommend the most promising design, so that further optimizations in sizing, or manual alterations to the components can be performed to reach the goals asked.

## 1.4 Objectives

The finality of the endeavor here presented, is divided into:

- Analyzing key academic works that represent major milestones regarding the development of topological synthesis aids.

- Creating a topology synthesis methodology, complementary to AIDA-C that:

- 1. receives the desired performance for a number of goals and delivers circuits, from a library, capable of attaining them, in preferential order.

- 2. In case of failure to encounter such circuits, delivers a list of available topologies based on their potential to be improved to fulfil these goals

- Choosing a collection of circuits and measurements suitable for performing optimizations on them to form the library.

- Developing a test set to verify the possibility of using optimizations with a higher number of objectives for lower number of objective requests to prove the tool's usefulness and correct functioning.

- Implementing the Topology into the AIDA-TOP tool.

- Examining the results of the application of the test set on the tool.

To define these objectives as successfully reached it is necessary to prove the methodology works. There are two manners to show the methodology functions correctly. The optimizations will be run on circuits that are known in-depth. This will allow for comparison between what would be expected before-hand, against the recommendations provided by the AIDA-TOP tool, which implements the methodology. Additionally, optimizations in which the objectives are subsets of the initially performed, will be executed, to evaluate to what extent the sizing with more goals can be indicative of a circuit's potential. This validation should be made in way to exclude statistical anomalies, providing a good confidence interval.

### 1.5 Document structure

This thesis will be divided into three main chapters. To start, a literature review, delving into the subject of choosing a topology. It will lay, chronologically, approaches previously attempted, selected to demonstrate different categories of strategies, and how they came to be. Still in Chapter 2, the categories stated are summed up, before they are used to do an extensive labelling of all previous works. On the 3<sup>rd</sup> Chapter the actual definition of our solution commences. In this section the details of the methodology are clearly defined, providing the reason that lead to the decisions made all through its creation. Chapter 4 logic and details of the preparations executed to check the precision of the methodology. Chapter 5 shows results achieved from using the tool, giving the metrics that can be used to discern whether this enterprise should be considered a success. In addition to these chapters it is written a final summary of everything accomplished, and ideas for the continuations to this work are given.

### 2 Previous Works

Choice of appropriate topology is a significant step for proper circuit CAD. This significance has made it a subject that has been analyzed throughout the years, searching for an adequate solution. Proposed strategies of approach diverge broadly in their results and methodologies. In this section, they are investigated, to understand which ones are most suitable, and thus could serve foundation to devise an improved solution. Furthermore, other knowledge requirements are presented, to fully comprehend the decisions made in constructing a novel algorithm, as well as its way of functioning.

Firstly, the main classification of solutions is explained, splitting the task into two main branches. Then a historic perspective is issued, where all projects that introduced a new type of paradigm are surveyed, exploring innovative concepts, which create new categories. Afterwards, all these categories and their use, are summarized to be applied in a table classifying a wide selection of works. This same table will include (when available), metrics that provide further details about each tool.

To understand the development of this framework, there are also some concepts, from related subjects that need to be explained. In this work multiple non-trivial concepts and algorithms such as Pareto-Fronts (POF), Multi-Objective Decision Algorithms (MODA), or nondominated sorting genetic algorithm II (NSGA-II) are used. They will be explained either where they first were applied during this review of previous works.

### 2.1 Topology Selection vs Generation

Pertaining to the objective of synthesizing a topology to reach a set of requirements, the mechanisms involved are typically distinguished into two disjunct categories: Topology Selection and Topology Generation. Similarly to the remaining classifications, it could also be presented within the context of the historical overview, nevertheless, its preponderance made it logical to emphasize, by describing it separately. While the overall perspective is that these are easily distinguishable, there is some misperception in the boundaries of each strategy. This confusion can be observed when sifting through past ventures in the subject of EDA and it stems from the usual meaning of these words, in their English language usage. In this subsection each of the strategies is demarcated clearly, making for a concise definition, that can be objectively applied.

As it has been mentioned before, when designing an analog circuit there is a never-ending number of topologies, that can be created by connecting multiple components in different manners. There are some architectures for each class that designers, depending on their specialization, know well. They are aware of their applications, limits, and general features. These types of topologies are finite yet numerous. The process of selecting the most appropriate topology amongst known ones, is named **Topology Selection**. Another way of approaching the problem is to construct one or more topologies, combining components or blocks of components. Here there is infinite room for expansion, by adding components or simply by joining them in previously unconsidered patterns. This is called **Topology Generation**.

The reason for misunderstandings is that some topology generation methods, originate a multitude of topologies, until all combinations of connections, up to a maximum number of components, are exhausted. These compose a library, from which the relevant ones are said to be *selected*[17],[18]. This wording, albeit correct, in everyday terminology uses the same word that was chosen to define the election of a schematic within those with a familiar structure. To ensure a clear distinction I would state again that Selection encompasses strictly habitual designs. If a topology, or wealth of topologies, stand outside of the bibliography of a class of circuits, then Topology Generation is being observed.

### 2.2 Chronological review

The idea of using computers to aid in the task cell design for analog circuits has been around since the end of the 1980's. To make a contribution in this field it is helpful to be aware of what was attempted before. This awareness can only be complete, considering what made the main actors choose a path, evaluating the merits and pitfalls of previous attempts. This way it is possible to avoid redundancy, take advantage of well performing concepts, and escape methods that proved less advantageous.

This topic, as with many others, is marked by divergent approaches. The emergence of these can usually be singled out in time, allowing us to present the algorithms, still used currently, in a chronological way. In this subsection, works are presented in this order, giving a causal perspective of their development, as well as insight of the historical trends. By clustering according to new concepts, it is possible to understand the main ideas of several works without delving into implementation details of all of them. The implementation can be improved, or features can be added, but the divisions presented here, make the most difference in the results of a project. Despite this, it is also useful to have a notion of the troubles and considerations encountered in implementing a tool, hence the detailed analysis of individual papers.

#### 2.2.1 Manual CAD

Even though there exist some small ventures into computer synthesized topologies, the first notable work to use the aid of a computers in the problem of choosing a schematic was IDAC [19], in 1987. It came as the culmination of independent endeavors on different types of circuits. This interactive tool introduced the idea of Topology Selection. It started on the architecture level design offering a library of classes of circuits: operational transconductance amplifiers (OTAs), analog to digital converters (ADCs), quartz oscillators, amongst others.

Within each, multiple different schematics were available to be picked by the user. Consequently, the process of selection can be labeled as **manual**. To size the topologies, the tool solved equations, previously coded into IDAC. Built-in analyzers simulated the fully sized circuits and compared the results with input specifications. Thus, regarding the design flow IDAC attempted to cover the architectural and cell design stages. Within the latter stage the sizing and topology selection were made separately, which given our

focus on the topology, it can be categorized as **independent** topology design. When the specifications failed, the program executed new iteration with adjusted specifications.

This process was to be repeated, exhausting all possible schematics, finally announcing the ones that should be able to perform in the desired way, while warning of potential shortcomings they could have. Regarding those that failed to meet the requirements, suggestions of how they could potentially be improved, were provided. In the end, the circuits were presented in a form that could be used by a sister tool ILAC[20], to perform the layout design.

This work was pioneer, representing one of the first CAD programs to be developed. It was an ambitious project, intended to help in two full stages of design. In the sizing department it strived for complete automation. In both, architectural and topology design, it saved time by having an incorporated library with useful solutions, ready to be used. Furthermore, after analysis, it supplied multiple successful topologies, with information about potential faults, from which the user could choose.

However, although this first approach gave a first glimpse into the importance of having an auxiliary in finding a topology, it did so in a way that resorts to brute force, going through all chosen designs, indiscriminately. At that point the selection relied on the user to choose the relevant topologies and interpret the results of the sizing tool.

#### 2.2.2 Hierarchical view

Two years later, Harjani et al. [21] developed a new system, OASYS, attempting to address IDAC's lack of flexibility due to the usage of circuit schematics that could not be altered, more difficulty to tune failures because of a less hierarchical structure, dependency on a separate numerical optimization phase for coarse design loop, and lastly its more closed goal, presenting only a series of programs for specific cases.

To resolve these issues, this solution ported an approach from the digital counterpart, with the caveat of the characteristic of reusage of portions cells, typical to analog design. The authors emphasized that a main focus of this new methodology is hierarchy.

Even though both IDAC and OASYS present hierarchies, they do it in a distinct manner. IDAC displayed it through coverage of several design flow stages, being overly ambitious in the breadth of stages it encompassed. This overreach is evidenced by the fact that future ventures commonly restricted themselves to one class of circuits. IDAC first focused on architectural design, which has classes of circuits, and cell-design (instance of a class), after the class is chosen. OASYS only considers the cell stage. However, it further subdivided a cell into sub-cell abstracts blocks (e.g. current mirror), sub-blocks.

Given that our work's interest is centered in cell-design, the approach is considered **hierarchical**, if it divides cells into more than one layer like in OASYS. On the contrary, IDAC's cell representation is **flat**, with each schematic being immediately composed of electrical devices. The use of hierarchy replicates the human designer's *modus operandi*, of partitioning the task into designing multiple smaller components. If the circuit is larger, extra levels may be added. The layers, their components, and respective models were created from designers' knowledge of often reused blocks and abstractions.

In this hierarchical structure (as seen in OASYS), not only is the circuit design broken into smaller pieces, but additionally, it permits the usage of the same blocks in different contexts, setting them up only once. Nevertheless, this representation removes the ability to employ design "tricks", that affect multiple blocks, which are only accessible when single devices are exposed and independently mutable, a capability this tool does not possess. Humans have the knowledge to implement such tricks, using a flattened view of the schematic, expanding the limits of performance.

In this same implementation iterations of two steps are needed to arrive at a complete circuit. The number of iterations depends on the layers of hierarchy that exist. For each layer, firstly a distinct combination of building blocks is chosen. These interconnections of blocks are called design styles. Then, from the known interactions between the blocks, and the final desired requirements, specifications are translated for each block. This couple of tasks is undergone until the design styles' blocks are elementary components. The first step is design style selection, and the second translation. As am example, to design an opamp, two iterations are translated so that the best combination of connections of transistors within a sub-block can be designated and finally sized. A visual representation of these concepts is shown in Figure 2.1. In the end, the framework strived to meet required specifications, allowing for optional future optimization.

Figure 2.1 – Two-layer Translation and Style Selection steps for opamp design. [21]

With this strategy, the design task remained uniform, independently of the complexity of circuits. Furthermore, since block interconnections are limited, there was a fixed number of design styles. For the specification of each design style into device level, there existed also a fixed number of possibilities, albeit with variable component sizings. This represents a divide-and-conquer approach to the problem, making for balanced computation between tasks. Such structure also permits for scalability, as the process remains unchanged, only considering additional options, should it be decided to add sub-blocks, if each one is sufficiently defined.

#### 2.2.3 Knowledge-Based implementation

While choosing design styles OASYS relied mostly on attempting multiple ones generating them in a predefined order, testing and storing the best. The thought behind this, was that a wealth of design styles can be coerced to perform at asked standards in different situations, even if sub optimally. The authors stated that it was a much more natural way to choose fully implemented circuits than using heuristics to

guess beforehand which one will be better. Despite this, some heuristics were also used to obtain an approximation of the feasibility of the critical parameters, permitting discrimination amongst design styles.

In the beginning, performance specifications were input by the user. After design style selection, the program now requires translation for defining specifications that the styles' constituent blocks must attend to. To execute the translation, a design style needs a design plan, consisting of useful circuit relationships. Since problems are often under-constrained, the storage of the plans, as basic analytical relationships, is often insufficient. The plan is a course of action to arrive at intended parameters. They consist of steps that apply heuristics that might need future verification e.g. estimation parasitic capacitance, gain partitioning in different stages. These also computes algebraic linear equations and sets of simultaneous equations.

A failure handling system is implemented, which is activated by the impossibility of achieving a certain specification with the default plan. Plan-fixers, chosen with IF-THEN rules, are either based on simple actions, or be more algorithmic. These fixes are required when some heuristics were used to get an approximation of a quantity, proved incorrect by a more precise computation executed in a lower level.

This tool further automates the process, by replacing extensive simulation and optimization of human selected circuits, with methods that reduce computation, while still providing the best or at least a good option. The authors instilled subject specific information, to be used for synthesis. This information must be manually modeled and introduced into the tool, making them **manually compounded knowledge-based** tools.

#### 2.2.4 Joint design stages

Contrary to IDAC, in OASYS it is unfeasible to separate clearly what actions focus on topology creation from those that concern sizing. This option is antagonistic with the independent, regarding the separation of the cell design parts. When the design flow does not demarcate the topology design part, it can be defined as **joint** topology design, indicating the union of the topology design stage with other tasks.

In OASYS' particular case topology and sizing are mixed, but it is possible to find encounter others joining different stages, as architectural and/or layout. Whilst joint design presupposes that other tasks are considered, independent design, may or may not have additional ones. In IDAC it is seen a topology design independent stage, but sizing is executed afterwards.

#### 2.2.5 Improvement of overall performance

At the same time as OASYS was published, OPASYN [22] was released. It set out to synthesize Complementary Metal-Oxide-Semiconductor (CMOS) Operational Amplifiers (OPAMPs) completely, covering cell and layout design. The component here scrutinized is the Selection Module, responsible for providing a promising topology, which will later be introduced into size and layout modules. Alternatively, the user could input a schematic of his choosing.

This work used flat view, citing an impossibility to propagate constraints within components, due to tight and intricate coupling between functional models. The 5 topologies, available in this work laid on the leaves of a decision tree shown in Figure 2.2. The choice was made by pruning it according to the demands in the following specifications: application area, open-loop gain, Power Supply Rejection Ratio (PSSR), and fully differential requirement.

Upon selection the topology would be forwarded to the sizing module where the parameters were tuned, maximizing a design cost function, calculated as a weighted sum of the performance in each parameter. This method of evaluating the success of a circuit departs from the previous works, that focused solely in attaining the constraints presented. It was then an **overall** performance objective, contrary to the previously seen focus on **constraints achievement**.

Figure 2.2 - OPASYN decision tree. [22]

At last, its layout was defined, and the final circuits presented to the user, that must make the final selection. Ultimately OPASYN's topology design appears to be overshadowed by the larger focus placed into the sizing and layout tools.

Even though both this work and OASYS were knowledge-based, it is possible to observe that they are distinct in the amount of knowledge they contain. This difference shows a trade-off within this type of solutions. OPASYN had only a handful of topologies available, limiting the choice when compared to OASYS. On the other hand, the implementation of OPASYN was simpler requiring only a few lines of code to choose between all options, whereas the other tool requires extensive codification per block. Generally,

as the options grow larger in this sort of solutions, so must the complexity of the code and the expertise and time required to program it.

In terms of hierarchy they present opposite mindsets, flat and hierarchical. The latter view provides the ability to generalize knowledge of a block into multiple usages, unbalancing the relationship between set up complexity and the number of synthesizable topologies. This advantage is gained by understanding all blocks and their relationships, which is demanding to do and even harder to implement.

#### 2.2.6 Automating knowledge

Maulik et al. [23], realized that with a few adaptations, the problem of obtaining topologies and their device characteristics could be perceived as a Nonlinear Programming problem, thus enabling the usage of methodologies familiar this branch of mathematics. This was a solution joint with sizing, a point considered essential for this work.

Resorting to [24] cited in the paper, the definition of a nonlinear programing problem is formulated as:

$$\begin{array}{ll} \text{Minimize} & f(x) \\ \text{s.t.} & g_i(x) \leq 0 & \text{for } i = 1, \dots, m \\ & h_i(x) = 0 & \text{for } i = 1, \dots, l \\ & x \in X \end{array}$$

where f(x) is the objective function to be minimized, varying the value of variables  $x_1, ..., x_n$  contained in the vector x belonging to subset of  $\mathbb{R}^n$ , X, whilst obeying to inequality  $g_i(x)$  and equality  $h_i(x)$  constraints. To apply this formulation to the circuit design problem, it was defined that the variables had two meanings. Binary variables represented the inclusion or the exclusion of predefined parts of the circuit, e.g. commonsource amplifier with the value of variable Y deciding whether it includes a cascode. Figure 2.3 shows the circuit with all options included, that is, with the cascode (dashed line) and the variable that controls it (Y) marked nearby. Additionally, to completely describe the circuit, the device parameters, whose representation is continuous, also needed to be included.

Usage of both, continuous and integer variables, leads to the description of this problem as Mixed Integer. Regarding the equations that constraint the system, they are not all linear, considering the circuits contain nonlinear components. Subsequently, the problem of solving for variables is classified as Mixed Integer NonLinear Programming reason for its name to be MINLP.

Figure 2.3 – Common-source amplifier with variable Y controlling the presence of a cascode.

In this work the constraints contained limitations of the technology, Kirchhoff's' Current and Voltage Laws (KCL and KVL) constraints, in conjunction with performance requirements. Variable conditions are trivial, performance conditions, however, required experts' time and knowledge to define. KVL and KCL were extracted resorting to an external algorithm, initiating the notion of **automatic compounded knowledge-based** tools, even if used only for part of the whole knowledge.

#### 2.2.7 Fixed Single Objective

The objective function f(x) in (2.1) was centered on minimizing the area of the circuit, the **fixed single** objective of this optimization solution. This goal, as the overall performance one, no longer arrests execution when constraint specifications are assured, continuing the search for designs that perform better in this sole objective.

The set of all solutions where the entirety of constraints is guaranteed is the feasible region (with feasible solutions in it), within which an optimum is sought. An algorithm was chosen that formerly demonstrated to be able to solve this faction of problems, was the elected method, adjusting the representation to be as convex as possible, improving the algorithm's performance. These steps are applied to 64 two-stage CMOS topologies, first setting up the circuits, then selecting of optimal one. MINLP is the only approach that explicitly states the problem as a nonlinear programing one, using a known methodology to discover optimal solutions.

#### 2.2.8 Evolutionary Algorithms

A few decades after the birth of evolutionary algorithms (EA), analog designers began attempting to utilize its principles to automate circuit synthesis. Inspired by the successes of works which applied this subclass of biological-based algorithms in other steps of the analog synthesis flow, Lohn and Colombano [25] opted to include the task of defining a topology, representing the first impactful results in such effort.

Evolutionary computation bases itself on the Darwinian concept of survival of the fittest. It operates on collections of individuals, called populations, and much like nature, retains, on every generation i.e. iteration, only those who behave more fittingly to the surrounding conditions. As stated Ashlock's book [26] a algorithm is encompassed in evolutionary computation if it contains the loop in Table 2.1.

Table 2.1 – Evolutionary Algorithm Loop. Generate population of structures Repeat Test the structures for quality Select the structures to reproduce Replace old structures with new ones Until satisfied

To implement such method, it is required that populations and their individuals are defined. Their structures must be detailed, the criteria by which the individuals are deemed fit set, and the necessary mechanisms to vary the population, creating different individuals that might be more adequate, employed.

In this version, the individuals that integrated the population were the circuits. The way each generation is ranked by fitness reflected the objectives of the algorithm, considering fitter the ones that performed better at them.

Also replicating biological evolution, the main mechanisms for diversification were crossover, and mutation. Crossover refers to the mixing of traits (genes) in surviving elements, an operation prone to generate healthy offspring, through combination of different characteristics. Mutation slightly alters an individual, potentially inserting an unexplored concept, aiding in exploring all possibilities. No justification was provided regarding the population size and number of generations set.

A circuit constructing bot placed components individually, in a manner that generated valid circuit graphs. The circuits had a cap of 150 devices, which could be transistors, resistors, inductors, and capacitors. The constructing thread decided which component was placed, how it was placed, and its parameters, encoding it into a bytecode. Since the device parameters were set simultaneous to the creation of the schematic, there was no division between the sizing and topology tasks. The bot moved along through a main branch,

extending the circuit one component at a time, creating occasional secondary branches. Consequently, a circuit was a list of bytecodes, defining the order of placement of all sized components.

This non-hierarchical view, centered on components, gave the ability to construct a wide range of topologies, only restricted by number of elements and validity insurance through limiting the main branch constructing thread to one node. This limitation had the benefit of keeping creation complexity at O(n), by discarding the need for verification of circuit correctness.

To commence this algorithm, the initial population had to be created, having a user defined number of individuals up to 18 000. The circuit-constructing bot then generated all these circuits, providing a starting point for the algorithm. They were evaluated, computing the individual fitness, which was the aptness to reach the objectives.

According to [27], cited in the paper, the evolutionary algorithm in an iteration firstly undergoes reproduction, with a mating pool, having the same number of individuals as the current population, to be occupied with elements of the existing one. In this phase, copies of elements from the previous generation are chosen randomly, with the probability of an individual being replicated proportional to its fitness. These draws are performed independently until the pool is complete. This way, fitness imitates the natural ability of a creature to reproduce.

After these steps, the mating pool only contains clones of previous elements, not introducing diversity. Adaptable species often display genetic material from two parents, thus varying the gene pool. This concept is emulated by the crossover operator, combining two arbitrary elements in the new population through swapping portions of their genetic information, originating offspring. The rate of elements subject to this rearrangement is the crossover probability, or crossover rate[25].

Finally, the mutation process occurred, where a small percentage of values were changed by chance. The frequency of these alterations is the mutation rate. Both these methods work towards the exploration of the search space for more prolific solutions. After reproduction, crossover, and mutation a new generation is created. The crossover rate is typically much higher than the mutation probability, in tune with what happens in nature. This loop will be repeated until a set number of generations is reached. The listed steps, either the initial creation of the population, as well as subsequent generations, have the potential to originate unseen circuits, revealing the first topology generation tool.

#### 2.2.9 Mutable Objective

In the MINLP (section 2.2.6) solution the concept of having a single metric, as objective to improve after all constraints had been met, was presented. However, in AMS design this objective is not universal. Even within the same class of circuits, an application, might require the largest gain, or lowest power consumption. As a reflection of this necessity, the latest work introduced (Lohn and Colombano [25]) doesn't set a particular goal for all classes of circuits. It gives the user the ability to select the specification considered a priority thus having a **mutable single** objective.

#### 2.2.10 Circuit evaluation

Until this point, the way to evaluate the performance of a circuit, within its design, had been through numerical analysis of the circuits. The analysis is performed on circuits' models, requiring previous set-up of equations that describe it, either manually or with algorithmic aid. Different circuit categories demand distinct analyses to evaluate their behavior. The models contain approximations that can lead to relevant alterations in actual circuit behavior. This technique is **equation-based** evaluation.

On the other hand the work of Lohn and Columbano [25], uses the renowned Simulation Program with Integrated Circuit Emphasis (SPICE) tool. Released for public domain by Berkley University in 1975, this simulation program has been a staple from its creation to modern days a staple in electrical simulation. The program takes a standard circuit representation (netlist) and emulates precisely its physical behavior. The bytecode list format was translated into the netlist format for each of the individuals in a generation and ran by the simulator. It is possible to categorize the evaluation of circuits produced as **simulation-based**

Before this usage in the evaluation step, this simulator was usually run to verify a final design. The reason for only using in that stage is the nonlinear growth of computation requirements expended by SPICE with the growth of circuit nodes, becoming very demanding with this node increase. This characteristic is a consequence of the representation of circuits as nonlinear differential equations, whose solution is difficult but leads to an exact model. It is also a method that can be applied to generality of schematics, not necessitating further set-up beyond the translation to a netlist. Over the years other similar tools have emerged, particularly SPECTRE and Eldo®, having similar method of action.

In choosing a simulation-based method, accuracy and the ability to effortlessly use a wealth of schematics are chosen over computation speed. That is what happens in [25] with the added benefit of a parallel implementation, simultaneously simulating several circuits, reducing the population's evaluation time.

#### 2.2.11 Classes of EAs

It is clear from the description of [25] that the work elaborates an EA. This class of solutions can be further subdivided into Genetic Algorithms (GA) or Genetic Programming (GP). The defining characteristics to place an approach into either category is based on the way of representation of the individuals. Koza [28], introduces GP as an extension of GA, looking to repair the limitation imposed through the exclusive usage of fixed-length character strings, expanding to more complex, adaptable hierarchic structures capable of encompassing computer functions. These should portray the hierarchy and dynamic size of a computer program, that can assume a tree form.

The project [25] assumed some qualities of a GA, as it had the typical structure of an evolutionary algorithm, and used strictly crossover and mutation. It also featured some relating to GP with its dynamic size, and the inclusion of function-like instructions for circuit placement. However, following the definitions provided, it failed the GA trait of fixed sized, and the GP's computer program hierarchical representation, leading the authors to present it as a GA with some GP elements. This new evolutionary methodology, through genetic programming or algorithm was groundbreaking and originated a great number of tools.

### 2.2.12 Genetic Programming

In the previous section the concept of genetic programming was introduced. In this section its first clear-cut, impactful implementation in topology generation is analyzed. The motivation behind the Sripramong et al. [17] was based upon the recognition of potential of evolutionary computation for analog circuit synthesis. It pointed out shortcomings displayed by the previously overviewed GA, which it vowed to improve. In particular it mentioned voluminous computation, from iterating 18,000 generations, the limitation of ways of connecting transistors, besides the lack of redundancy and unconventionality verifiers, creating repeated as well as unorthodox connections.

The schematics were represented in tree-form, conforming to the standard GP representation. The traversal of said tree instructed the evolution of a single wire from input to output into a complex network of device connections (Figure 2.4). For that, it had 5 different connection modifying actions (evolving functions) that a wire could be turned into, one node referencing function, 7 two-terminal components (resistor, capacitor, independent sources etc. as well as floating connection), and transistors (N or P-type) which have 3 terminals. A node could, for example, turn a wire into two parallel or series ones, and its leaves define which components were present in each of them. The parent defines how the leaves were connected, with exception of 3 terminal components that required a third connection and an evolving function that enabled the connection with a non-adjacent node, named a cross-linked connection.

Figure 2.4 – Effect of evolving functions.

For every tree, current flow lists were extracted from their original representation, according to the dc current flowing through them. These lists were analyzed, to correct circuits with isolated or useless parts, change component connection, and obtain transistors' operating region. This methodology was based on Kirchhoff's laws, to process generated circuits. This verification ensured exclusively apt circuits were sent for PSPICE3 simulation, a resource demanding step, necessary to have precise data for the evaluation portion (simulation-based).

To initiate the evolutionary process the user had to supply an embryonic circuit. This circuit was converted to the program's preferred representation and cloned until it the population was complete. Afterwards, this uniform generation would undergo mutation, and current-flow analysis. The fitness function was composed as the normalized sum of 7 usual circuit goals, hence representing an overall performance goal, summing other 3 economic related targets after the main goals were reached.

The methods for developing new generations remain reproduction, crossover and mutation. But unlike the previous method of propagating the population, in this work, tournament selection is implemented, putting a few randomly selected individuals at odds, keeping the highest fitness one as a parent for crossover. Mutation is equally different, not changing just single bits, but resorting to the user-defined library to mutate random parts of a circuit and their parameters (mixed phases). This utilization of building blocks makes for a hierarchical representation of circuits. Regarding population size they contain 300-1000 elements, and the program halts when constraints are met, as opposed to pre-defining a number of generations

### 2.2.13 Multi-objective Optimization (MOO)

A multi-objective optimization problem is one that, as the name indicates, contains more than one objective function. A MOO problem is defined as [29]:

Which is similar to (2.1), but instead of having one objective f function, there are M objective functions.. The concept of feasible region is also applicable in here. The challenge of finding an optimal analog circuit, can be seen as such, since designers usually have multiple criteria they wish to optimize e.g. minimize area and maximize gain. The strategies formerly shown to address this particularity, convert its functions into a single one. However, the principles of confronting a single function problem are dissimilar to facing additional objective functions.

One concept unique to MOO is Pareto-Optimal solutions. This is a MCDM, useful when there is more than one objective function, to determine optimum solutions.

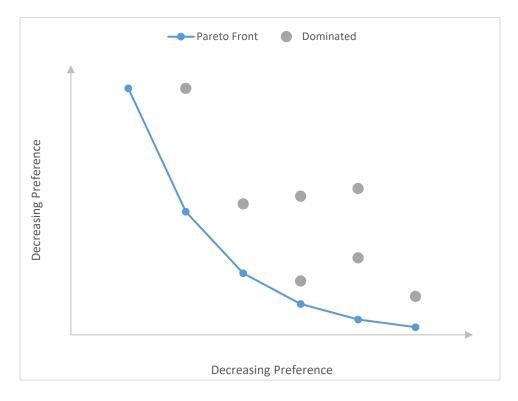

Take a problem with M = 2, so it has 2 objectives. Choosing any two solutions from the feasible region, for some it can be noted that one is superior (dominating) to the other in all objectives (dominated). On the other hand, other pairs might have it so that one solution is better in the first objective but worse in the second. The same can happen but being superior in the second objective and inferior in the first. They are said to be non-dominated solutions, where none excels the other, if both goals are equally valued. The curve obtained from line-connecting these solutions, is the pareto-optimal front (POF) and the group of all solutions the Pareto Set. This formulation can be extended for a larger number of objectives. In Figure 2.5 there is an example of a pareto front and dominated points that are excluded from it. In this case the axes evolve in decreasing preference, so the preferred points are the minimums.

Figure 2.5 - Pareto Front example.

A multi-objective evolutionary algorithm (MOEA) joins components from the two subsets of approaches the Multi-Objective perspective with an Evolutionary basis for iterating to through the search space. MOJITO [16], published in 2011 does exactly this. A mixed phase, hierarchical solution, with emphasis in exclusively using trustworthy topologies connected in familiar ways, an area where the authors reckoned that previous tools faltered, leading to manufacture-fallible circuits.

## 2.2.14 NSGA-II

The MOEA applied in MOJITO [16] (for a number of objectives not much larger than 2) is the NSGA-II algorithm. The second version of the NSGA introduced in 2002 [30] became a staple for MOEA, for its application of elitism, diversity assurance and computational efficiency. Elitism is the act of storing the best elements (elite) from previous generations in subsequent ones, bringing advantages in terms of efficiency in addition to keeping the best solutions from worsening with generations[30]. At the same time, diversity is relevant by increasing the amount of pareto optimal-solutions[25]. The fitness metric here revolves on individuals not being dominated (nondominated) by others, to progress towards the Pareto-optimal region.

The algorithm has two important subroutines: 1) fast nondominated sort 2) crowding distance assignment. The first segments a population P, into fronts  $F_i$  where i - 1 denotes the number of elements that dominate all individuals contained. Crowding distance assignment routine obtains the average distance of an element to its neighbors, the smaller this distance, the more crowded and less diverse the population is. The main routine, in Figure 2.6, initiates a random parent population  $P_0$  with N individuals, on which tournament selection, crossover and mutation are applied, getting  $Q_0$  an equally large offspring population. After, the main loop starts, both are joined into  $R_0$  (2N elements) that will be sorted based on nondomination, obtaining fronts  $F_i$ . The elite fronts that cumulatively contain less than N elements will be indiscriminately added to the next parent set  $P_1$ . The front that would cause  $P_1$  to exceed N elements will be sorted by decreasing crowding order  $\prec_n$ , to occupy the remaining spots (until N) in  $P_1$  with the least crowded options.  $Q_1$  is fabricated with the same evolutionary operations to obtain offspring as the ones used before. This loop is repeated for the desired number of generations.

$$\begin{split} R_t &= P_t \cup Q_t \\ \mathcal{F} = \texttt{fast-non-dominated-sort}(R_t) \\ P_{t+1} &= \emptyset \text{ and } i = 1 \\ \texttt{until} \; |P_{t+1}| + |\mathcal{F}_i| \leq N \\ & \texttt{crowding-distance-assignment}(\mathcal{F}_i) \\ P_{t+1} &= P_{t+1} \cup \mathcal{F}_i \\ i &= i+1 \\ \texttt{Sort}(\mathcal{F}_i, \prec_n) \\ P_{t+1} &= P_{t+1} \cup \mathcal{F}_i[1:(N - |P_{t+1}|)] \\ Q_{t+1} &= \texttt{make-new-pop}(P_{t+1}) \\ t &= t+1 \end{split}$$

combine parent and offspring population  $\mathcal{F} = (\mathcal{F}_1, \mathcal{F}_2, \ldots)$ , all nondominated fronts of  $R_t$ until the parent population is filled calculate crowding-distance in  $\mathcal{F}_i$ include *i*th nondominated front in the parent pop check the next front for inclusion sort in descending order using  $\prec_n$ choose the first  $(N - |P_{t+1}|)$  elements of  $\mathcal{F}_i$ use selection, crossover and mutation to create a new population  $Q_{t+1}$ increment the generation counter

Figure 2.6 – Pseudocode from [31] with the NSGA-II main loop.

MOJITO implements this algorithm, with some modifications to avoid premature convergence, in a GP based program. Namely the version used divides the population into age groups. In this manner, random individuals can be added to the population without being unfairly compared to circuits that already underwent improvements. This further diversifies the population, originating a broader spectrum of solutions.

## 2.2.15 Causal synthesis

Artificial cognitive systems emerged as a consequence of the interest in artificial intelligence looking to incorporate cognitive neuroscience and developmental psychology. The idea is to replicate the abilities of perceiving the environment, recognize the necessity to operate, gather experience from past events and mutate as required by the surroundings, into an artificial system. This sort of technique stems from a recognition of the superiority of humans in the performance of a wealth of tasks. To import what is described as unified theory of cognition, composed of skills such as attention, memory, problem solving, decision making, and learning, to a system is to create a Cognitive Architecture. [32]

Observing the problem of circuit synthesis, it fits the type of challenges that artificial cognitive system is sets out to solve. First and foremost, to this day the design of circuits is still reliant on expert-knowledge, especially when it comes to the choice of schematic. Secondly, it is evident from the preponderance of hierarchy in previous works, that pattern detection is an important component. In addition to this, the ability to learn in these architectures could replace the manual or algorithmic methods of knowledge formulation once used. Li et al, presented in 2018 InnovA [33], a cognitive architecture applied to analog circuit design.

This cognitive architecture tries to exert creative problem solving, topology creation and modification, design knowledge identification and reuse. It appropriates ideas from the fields that have been referred as inspiration to these architectures, to bring functionalities like concept formation, comparison, and combination. It is a tool that generates innovative topologies, unbeknownst so far, through combination of concepts and features. This work, ultimately, tries to decompose circuits, understand the cause for the existence of its parts, and integrate these skills with the ability of learning to learn. The use of cause and effect for synthesis and learning introduces **causal** synthesis.

## 2.2.16 Conceptual View

Riddled with ideas from psychology and neuroscience, the InnovA architecture is intricate, having different modules coupled with each other. One of these, uses signal paths to autonomously detect building blocks, storing frequent connections between them, or small differences deeming them all as concepts. The uniqueness of these is ensured prior to addition. They are divided in clusters, based on topological similarity, each addressing a set of performance specifications (niche). The kernel gathers the common traits to the elements in the cluster, also containing what they add to the performance, thus supplying the reason for their presence (causality). This is the module of semantic memory, as the information stored is relevant within the same context (specific conditions). The union of all semantic memories is the long-term memory, which will originate short-term memory when using only a portion of it based on the task at hand and episodic memory, listing solutions for specific problems. The introduction of concepts that include the usage of traditional building blocks but not exclusively, also having small modifications that influence the circuit originate **conceptual view**, breaking from the preexisting dichotomy. This implementation simultaneously allows the advantage from both previous perspectives, reusing known blocks, but enabling the usage of "tricks", all mentioned in section 2.2.2

## 2.2.17 Hybrid Generation and Selection

The architecture has a subjective and an objective reasoning and learning part. The reasoning occurs any time that the tool is presented with a problem. It runs through a series of mechanisms influenced by both parts to arrive at a solution. Long-term memory (and consequently the other types) is not static, it can be changed without the intervention of the user. This is the learning part of the architecture, having the ability to include circuits that the users supply. Furthermore, it can re-assess knowledge when presented with new challenges, by adding solutions or changing previous conceptions that had been created. Even though the purpose and way of operating of both are detailed, only the objective type and its algorithms are already implemented.