# **RISC-V Processing System with streaming support**

# Eduardo Miguel Ferreira Cabral de Melo

Thesis to obtain the Master of Science Degree in

# **Electrical and Computer Engineering**

Supervisor(s): Prof. Nuno Filipe Valentim Roma Prof. Pedro Filipe Zeferino Tomás

# **Examination Committee**

Chairperson: Prof. Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Prof. Pedro Filipe Zeferino Tomás Member of the Committee: Prof. João Carlos Viegas Martins Bispo

January 2020

ii

### Declaração

Declaro que o presente documento é um trabalho original da minha autoria e que cumpre todos os requisitos do Código de Conduta e Boas Práticas da Universidade de Lisboa.

### Declaration

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

# Acknowledgments

Quero agradecer aos meus orientadores, Professor Pedro Tomás e Professor Nuno Roma, pelo apoio prestado ao longo do desenvolvimento da minha tese. Quero também agradecer ao Nuno Neves pelo apoio prestado ao desenvolvimento da tese, especialmente em dúvidas relacionadas com o Xilinx Vivado. Por fim quero agradecer à minha família e aos meus amigos, por me apoiarem ao longo do meu percurso de 5 anos e especialmente durante o desenvolvimento deste trabalho.

This work was partially supported by national funds through Fundação para a Ciência e a Tecnologia under projects UID/CEC/50021/2019 and PTDC/EEI-HAC/30485/2017.

# Resumo

Ao longo dos últimos dois anos, a popularidade do conjunto de instruções RISC-V pela comunidade open-source e companhias tem vindo a crescer. O crescimento da popularide do RISC-V subsequentemente incentiva o desenvolvimento de novas extensões opcionais adicionadas ao conjunto de instruções RISC-V que, por sua vez, proporcionam ferramentas para enfrentar diversas tarefas de elevada relevância para a industria, consequentemente promovendo o desenvolvimento de extensões que usam novas técnicas e conceitos ainda nao aplicados. O desenvolvimento deste trabalho foi motivado pela análise de uma nova extensao desenvolvida para o RISC-V, chamada Unlimited Vector Extension, que proporciona suporte ao nível da arquitetura de conjunto de instruções para streaming de dados em conjunto com o suporte para instruções SIMD escaláveis. Este trabalho proporciona uma implementação proof of concept da extensão UVE, partindo de um sistema softcore RISC-V base, adicionando um Stream Engine e um Acelarador Vectorial ao sistema base. O sistema foi implementado com sucesso na placa FPGA Xilinx Virtex UltraScale+ VCU1525 e testado usando um conjunto de benchmarks corretamente vectorizados para uso com a extensão UVE, resultando em tempos de execução até 23 vezes mais elevados e valores de EDP até 195 vezes mais baixos quando comparado com código RISC-V não vectorizado.

# Abstract

Over the last two years, the adoption of the RISC-V ISA by the open-source community and companies has been increasing. This further encourages the development of new custom extensions added on top of the base ISA, some of them making use of novelty techniques and concepts. The development of this work was motivated by analysing a novel isntruction set extension that was recently developed for the RISC-V ISA, namely the Unlimited Vector Extension(UVE). It provides ISA level support for data streaming coupled with scalable SIMD instructions, and, in simulation, provides substantial performance gains regarding the state-of-the-art ARM Scalable Vector Extension (SVE). This work provides a proof of concept implementation of the UVE extension on a base RISC-V Softcore system, by adding a Stream Engine and Vector Accelerator hardware component to the design. The system was successfully implemented on a Xilinx Virtex UltraScale+ VCU1525 FPGA Board and tested by vectorizing a set of benchmarks, which resulted in execution times of up to 23 times higher and EDP values of up to 195 lower when compared with the base RISC-V code.

# Contents

|   | Ackı  | nowledgments                                         | iv   |

|---|-------|------------------------------------------------------|------|

|   | Res   | sumo                                                 | v    |

|   | Abs   | stract                                               | vii  |

|   | List  | of Tables                                            | xiii |

|   | List  | of Figures                                           | xv   |

|   | Nom   | nenclature                                           | 1    |

|   | Glos  | ssary                                                | 1    |

| 1 | Intra | oduction                                             | 1    |

| ' |       |                                                      | -    |

|   | 1.1   | Motivation and Topic Overview                        | 1    |

|   | 1.2   |                                                      |      |

|   | 1.3   |                                                      | 2    |

|   | 1.4   | Thesis Outline                                       | 2    |

| 2 | Bac   | ckground and Related Work                            | 5    |

|   | 2.1   | Scalable Single Instruction Multiple Data Extensions | 5    |

|   |       | 2.1.1 ARM Scalable Vector Extension                  | 6    |

|   |       | 2.1.2 RISC-V Vector Extension                        | 7    |

|   | 2.2   | Data Streaming Architectures                         | 8    |

|   |       | 2.2.1 Data Streaming to Multiple Processing Elements | 8    |

|   |       | 2.2.2 Data Streaming to Dedicated Accelerator        | 11   |

|   | 2.3   | Unlimited Vector Extension                           | 12   |

|   |       | 2.3.1 Memory Access Representation                   | 13   |

|   |       | 2.3.2 Architectural State                            | 16   |

|   |       | 2.3.3 Streaming Instructions                         | 18   |

|   | 2.4   | Summary                                              | 20   |

| 3 | Bas   | se RISC-V Softcore Processor                         | 21   |

|   | 3.1   | Scalar Core                                          | 21   |

|   |       | 3.1.1 Instruction Fetch Stage                        | 22   |

|   |       | 3.1.2 Instruction Decode Stage                       | 22   |

|   |       | 3.1.3 Execute Stage                                  | 23   |

|   |      | 3.1.4  | Memory Stage                            | 23 |

|---|------|--------|-----------------------------------------|----|

|   |      | 3.1.5  | Write Back Stage                        | 24 |

|   | 3.2  | L1 Da  | ta Cache                                | 24 |

|   | 3.3  | Periph | erals                                   | 25 |

|   | 3.4  | Summ   | nary                                    | 26 |

| 4 | Prop | posed  | System Architecture                     | 27 |

|   | 4.1  | Vector | Accelerator                             | 28 |

|   |      | 4.1.1  | Instruction Decode Stage                | 29 |

|   |      | 4.1.2  | Execute Stage                           | 30 |

|   |      | 4.1.3  | Memory Stage                            | 32 |

|   |      | 4.1.4  | Write Back Stage                        | 32 |

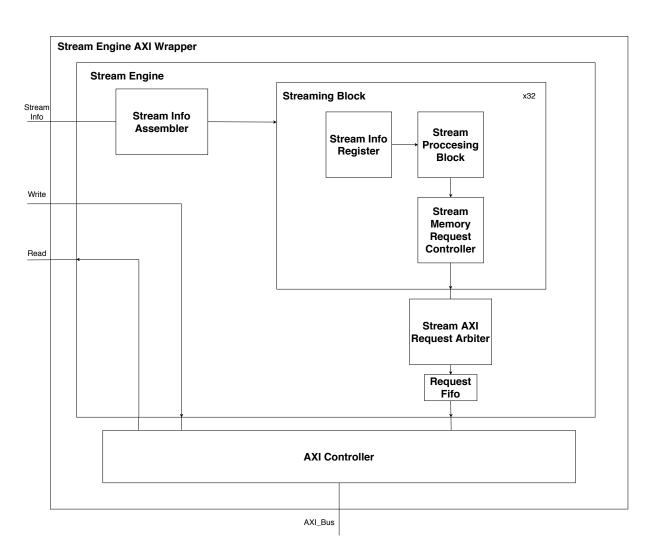

|   | 4.2  | Strear | ning Engine                             | 33 |

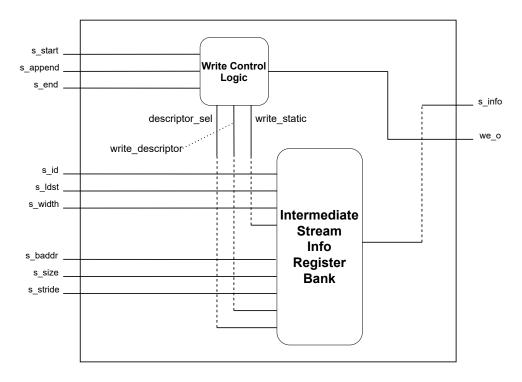

|   |      | 4.2.1  | Stream Info Assembler                   | 34 |

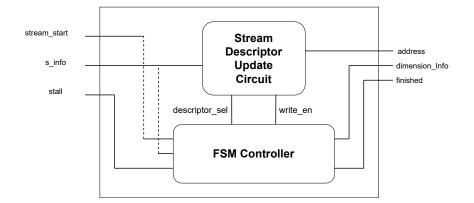

|   |      | 4.2.2  | Stream Processing Block                 | 35 |

|   |      | 4.2.3  | Stream Memory Request Controller        | 39 |

|   |      | 4.2.4  | Stream Request Arbiter                  | 40 |

|   |      | 4.2.5  | Stream AXI Controller                   | 42 |

|   |      | 4.2.6  | Stream Data Input/Output Interface      | 43 |

|   | 4.3  | Syster | m Additions and Modifications           | 44 |

|   |      | 4.3.1  | Peripheral Controller                   | 44 |

|   |      | 4.3.2  | Scalar Core                             | 45 |

|   | 4.4  | Summ   | nary                                    | 49 |

| 5 | Dev  | elopme | ent Workflow and Benchmarks             | 51 |

|   | 5.1  | Softwa | are Tools                               | 51 |

|   |      | 5.1.1  | GCC Compiler                            | 51 |

|   |      | 5.1.2  | Unlimited Vector Extension Support      | 52 |

|   |      | 5.1.3  | Board Support Package and Linker Script | 52 |

|   | 5.2  | Bench  | marks                                   | 53 |

|   |      | 5.2.1  | Memory Copy                             | 53 |

|   |      | 5.2.2  | Scaled Vector Addition                  | 55 |

|   |      | 5.2.3  | Matrix Vector Multiplication            | 56 |

|   | 5.3  | Summ   | nary                                    | 58 |

| 6 | Imp  | lement | ation and Benchmark Results             | 59 |

|   | 6.1  | Impler | nentation Results                       | 59 |

|   |      | 6.1.1  | Area Analysis                           | 59 |

|   |      | 6.1.2  | Timing Analysis                         | 61 |

|   |      | 6.1.3  | Power Analysis                          | 62 |

|    | 6.2 Benchmark Results |         |                              | 63 |  |  |

|----|-----------------------|---------|------------------------------|----|--|--|

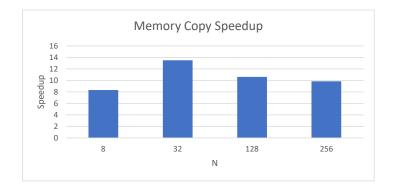

|    |                       | 6.2.1   | Memory Copy                  | 63 |  |  |

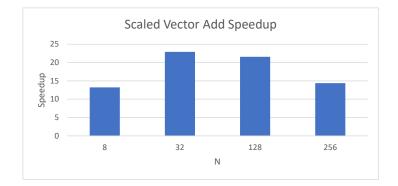

|    |                       | 6.2.2   | Scaled Vector Addition       | 64 |  |  |

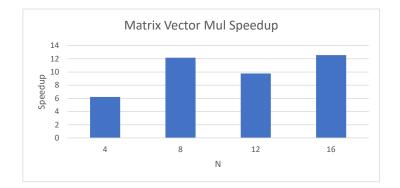

|    |                       | 6.2.3   | Matrix Vector Multiplication | 65 |  |  |

|    |                       | 6.2.4   | Energy Efficiency Analysis   | 66 |  |  |

|    | 6.3                   | Summ    | ary                          | 67 |  |  |

| 7  | Con                   | clusior | ıs                           | 69 |  |  |

|    | 7.1 Future Work       |         |                              |    |  |  |

| Bi | bliog                 | raphy   |                              | 71 |  |  |

| Α  | RISC                  | C-V Suj | pported Instructions         | 73 |  |  |

| В  | UVE                   | Suppo   | orted Instructions           | 75 |  |  |

| С  | Boa                   | rd Sup  | port Package                 | 77 |  |  |

# **List of Tables**

| 3.1 | Peripheral Address Ranges.                                                            | 26 |

|-----|---------------------------------------------------------------------------------------|----|

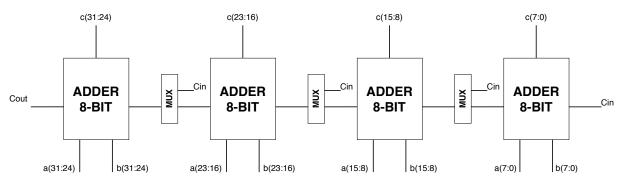

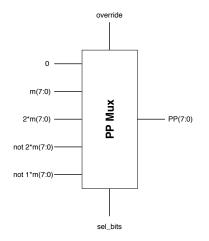

| 4.1 | Radix-4 Block Values and correspondent operation.                                     | 32 |

| 4.2 | Stream Info Assembler Input signal types and widths.                                  | 35 |

| 4.3 | Stream Info Assembler valid requests.                                                 | 35 |

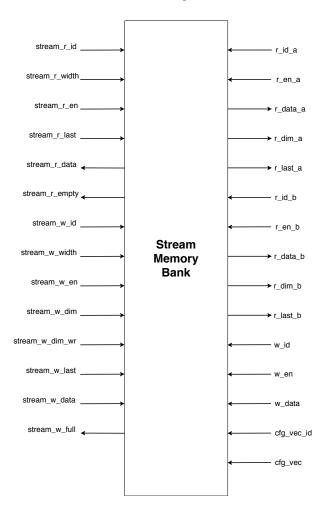

| 4.4 | Streaming Engine Read Interface.                                                      | 43 |

| 4.5 | Streaming Engine Write Interface.                                                     | 44 |

| 4.6 | Multi-cycle floating point operations.                                                | 49 |

| 5.1 | System memory layout.                                                                 | 53 |

| 6.1 | FPGA resource usage                                                                   | 61 |

| 6.2 | Maximum operating frequency results. Clock domain 1 correspond to the Scalar Core     |    |

|     | and Instruction Cache, clock domain 2 to the Peripheral Controller and Data Cache and |    |

|     | clock domain 3 to Streaming Engine and Vector Accelerator.                            | 62 |

| 6.3 | Dynamic power requirement per component.                                              | 63 |

| 6.4 | Energy Delay Product values.                                                          | 67 |

| B.1 | UVE Supported Instructions.                                                           | 75 |

# **List of Figures**

| 2.1  | Example of Execution Lanes for use in SIMD Instructions.                        | 5  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Stream Management Engine Overview, proposed by Neves et al                      | 9  |

| 2.3  | In-Cache Streaming Architecture Overview, proposed by Neves et al               | 10 |

| 2.4  | Softbrain Architecture Overview, proposed by Nowatzki et al.                    | 11 |

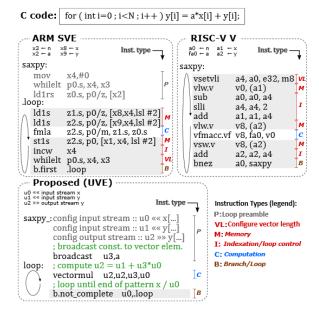

| 2.5  | Saxpy example kernel implementations using ARM SVE, RISC-V V and the UVE exten- |    |

|      | sion [4]. Instructions with shaded background represent loop overhead.          | 12 |

| 2.6  | One dimensional access examples                                                 | 13 |

| 2.7  | Two dimensional access examples                                                 | 14 |

| 2.8  | Lower triangular and Indirect Access Examples                                   | 14 |

| 2.9  | Vector Register Example Layout.                                                 | 16 |

| 2.10 | Predication Examples.                                                           | 17 |

| 2.11 | Simple 1D stream configuration instructions.                                    | 18 |

| 2.12 | Multiple dimension stream configuration instructions.                           | 18 |

| 2.13 | Stream control instructions.                                                    | 19 |

| 2.14 | Stream loop control instructions.                                               | 20 |

| 3.1  | Base RISC-V Processing System.                                                  | 21 |

| 3.2  | RISC-V Scalar Core.                                                             | 22 |

| 3.3  | Scoreboard Overview.                                                            | 23 |

| 3.4  | Cache WriteBack/WriteAllocate FSM.                                              | 24 |

| 3.5  | Peripheral Interface Diagram.                                                   | 25 |

| 3.6  | Peripheral Interface Diagram.                                                   | 26 |

| 4.1  | RISC-V Streaming Processing System.                                             | 27 |

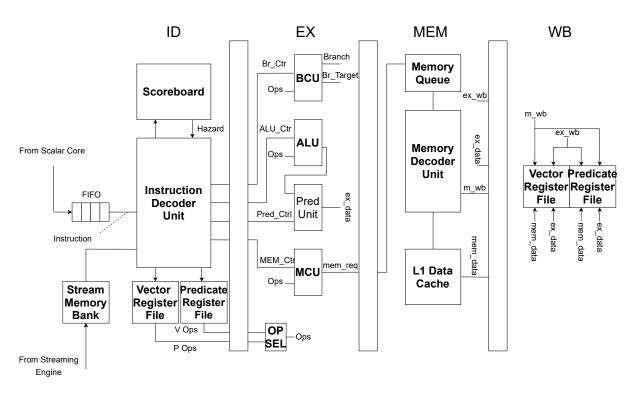

| 4.2  | Vector Accelerator Pipeline Diagram                                             | 28 |

| 4.3  | Stream Memory Bank I/O                                                          | 29 |

| 4.4  | 32 bit Variable Width Adder                                                     | 30 |

| 4.5  | Partial Product Operation Select Mux.                                           | 31 |

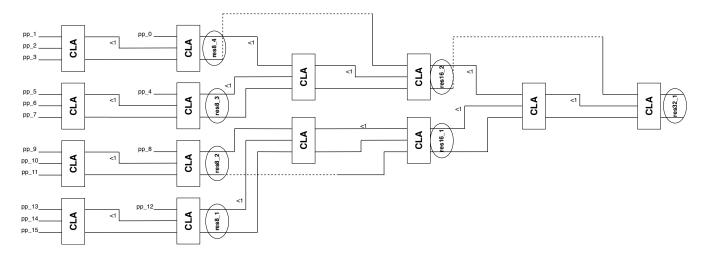

| 4.6  | 6 Lever Wallace Tree Reduction.                                                 | 32 |

| 4.7  | Streaming Engine Component Diagram.                                             | 33 |

| 4.8  | Stream Info Assembler Diagram.                                                  | 34 |

| 4.9  | Processing Block Diagram.                                    | 36 |

|------|--------------------------------------------------------------|----|

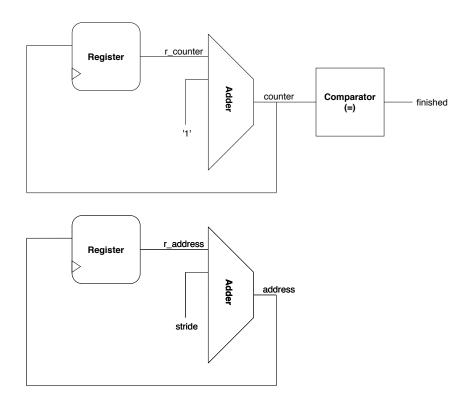

| 4.10 | Single Descriptor Update Circuit Diagram                     | 36 |

| 4.11 | Multiple Descriptor Update Circuit Diagram.                  | 37 |

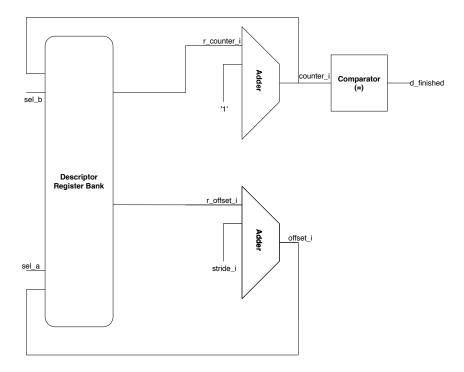

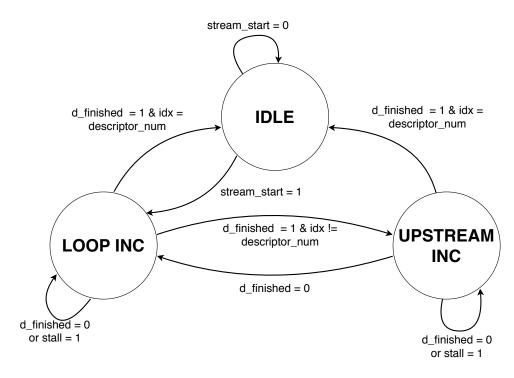

| 4.12 | Processing Block Finite State Machine Model.                 | 38 |

| 4.13 | Stream Memory Request Controller Diagram.                    | 39 |

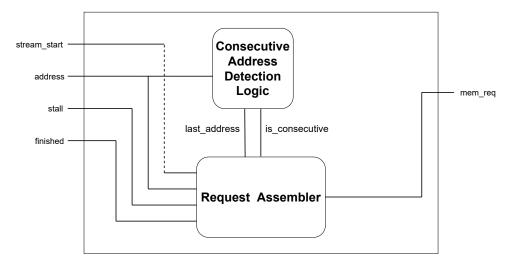

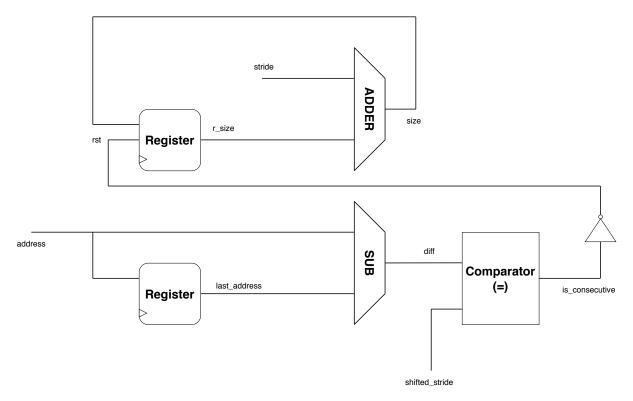

| 4.14 | Memory Request Controller Detection Circuit.                 | 39 |

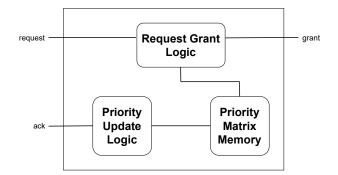

| 4.15 | Stream Request Arbiter Diagram.                              | 40 |

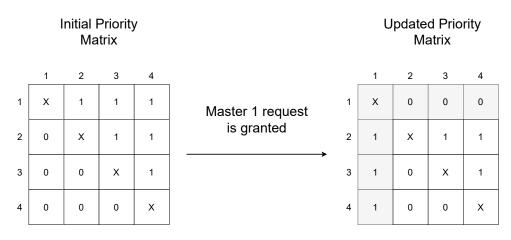

| 4.16 | Priority Matrix Update Example                               | 41 |

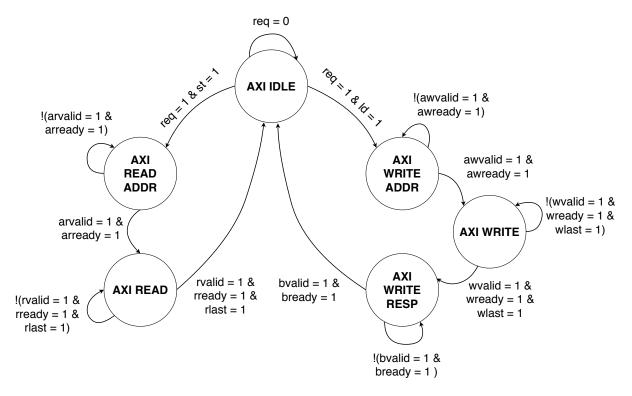

| 4.17 | AXI Controller Finite State Machine Diagram.                 | 42 |

| 4.18 | Peripheral Controller Finite State Machine Model             | 45 |

| 4.19 | Instruction Cache Simplified Diagram.                        | 46 |

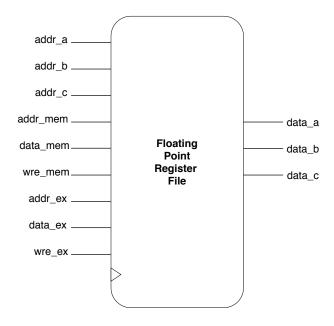

| 4.20 | Floating Point Register File I/O.                            | 47 |

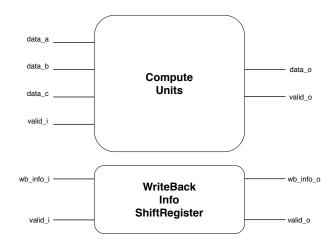

| 4.21 | Floating Point Unit Schematic.                               | 48 |

| 6.1  | Implementation placement result with highlighted components. | 60 |

| 6.2  | Memory Copy kernel speedup.                                  | 64 |

| 6.3  | Scaled Vector Addition kernel speedup.                       | 65 |

| 6.4  | Matrix Vector Multiplication kernel speedup.                 | 66 |

# **Chapter 1**

# Introduction

### 1.1 Motivation and Topic Overview

The CPU market over the last few years has been dominated by either off-the-shelf third party solutions, such as INTEL and AMD x86 processors, in consumer grade high performance devices, mainly laptop and desktop computers, or by ARM's proprietary instruction set architecture and processor designs in the mobile device and microcontroller domains. Although using third-party proprietary solutions has its benefits, such as not needing a dedicated hardware team to design and implement in-house solutions, it also comes with disadvantages, mainly due to the fact that the customer of the third party solution has little to no control over the processor architecture or over the changes made to the instruction set architecture, including its flexibility. In fact, APPLE's recent decision of moving their Macintosh computers from Intel x86 to ARM validates that having more control over the whole development stack does prove advantageous.

In order to provide the hardware community with a royalty free, flexible open source instruction set architecture, the RISC-V ISA was developed at the University of California, Berkeley and the ISA specification was later published so it could be used both in academia and in commercial products alike. The RISC-V ISA was structured to be as modular as possible. Consequently, and due to being a RISC instruction set architecture, the base integer instruction set, RV32 or RV64, depending on if the system is targeting 32 bits or 64 bits, is minimal. This leads to the base ISA being suitable for microcontrollers and others solutions that have strict power and area constraints. In contrast, if one requires a solution that does not have strict power and area constraints, but on the other hand requires more advanced features such as floating point support, or atomic and memory fencing instruction support, then one can make use of the several extensions that RISC-V ISA, third-party extensions that fulfill custom needs can be developed and integrated into a RISC-V design.

The motivation for this work started from the analysis of a novelty SIMD extension for RISC-V, the Unlimited Vector Extension (UVE). This extension provides ISA level support for data streaming, by describing a set of streaming instructions. Moreover, it provides a set of SIMD instructions that can be

used to produce or consume data to/from the streams defined and a set of stream branch instructions for stream-based loop flow control.

Another motivation for this work was the analysis of the Configurable RISC-V Softcore Processing System. This system provides a RISC-V Softcore implementation with support for 32-bit integer instructions, including the multiply and divide extension instructions. Furthermore, it provides support for a level 1 data cache and a set of memory-mapped peripherals. However, the lack of floating point support and of an Instruction Cache limit the flexibility and performance of the system.

This thesis strives to corroborate the flexibility provided by the RISC-V and the viability of ISA level data streaming support by providing a proof of concept implementation of a novel custom RISC-V scalable SIMD extension with ISA level support for data streaming on top of an already existing RISC-V processing system, while also contributing with improvements to the existing system, by the introduction of an Instruction Cache and floating point support.

## 1.2 Objectives

The objectives set and completed during the development of this work can be summarized in the following points:

- Addition of floating point support to the Scalar Core

- Development and inclusion of an Instruction Cache

- Development of a proof-of-concept implementation of the UVE extension on top of the base softcore system

# 1.3 Contributions

The addition of data streaming to a RISC-V system is the main focus of this work, consequently the main contribution of this work is the development of an hardware solution that allows support for data streaming at an ISA level. Throughout the realization of this work, others contributions were made, such as the addition of a dedicated Single Instruction Multiple Data accelerator, the development of an instruction cache, the communication mechanisms required so that the core and accelerator can both interface with the memory hierarchy of the system and peripherals, the introduction of support for different clock domains in the system and finally the analysis of the system results using a set of benchmarks.

## 1.4 Thesis Outline

This document is divided into 5 chapters, excluding the introduction and conclusions of this work. Chapter 2 provides the necessary background knowledge and concepts, related to computer architectures, needed to follow the work described in the following chapters. Succeeding chapter 2, a brief description of the baseline system used in this work and its components is provided in chapter 3. Consequently, this chapter provides some context to the reader about what part of the system is work prior to this thesis. Chapter 4 then explains in detail the hardware solutions developed in this work, and what is the function of each component when looking at the overall system. To more easily present relevant information, this chapter has been divided into three sections. The first section describes in detail the architecture of the developed SIMD accelerator. The second section focuses solely on the development of the Stream Engine and gives the reader an understanding of how data streaming is handled in the system. The third section then delves into the further changes that complement the addition of data streaming to the baseline system. Finally, chapters 5 and 6 provide an overview of the benchmarks used to evaluate the performance of the system, the software tools needed to compile such benchmarks, the system resource, frequency and power requirements and at last benchmark results and discussion.

# **Chapter 2**

# **Background and Related Work**

# 2.1 Scalable Single Instruction Multiple Data Extensions

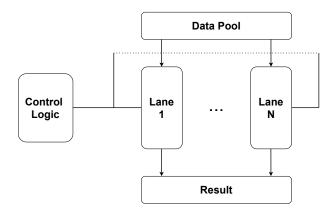

Figure 2.1: Example of Execution Lanes for use in SIMD Instructions.

The inclusion of Single Instruction Multiple Data (SIMD) extensions has become a standard in modern instruction set architectures. These extensions allow the architecture to explore data level parallelism, by processing several data elements, i.e a vector of elements, using a single program instruction, therefore increasing data throughput. The parallel processing of elements is achieved at the architecture level by including several lanes of execution in the core, where each lane processes a given data element and all lanes are arranged in parallel, like the example in figure 2.1. The number of lanes is proportional to the register width of the SIMD extension, which is most commonly 256 or 512 bits. In scalable SIMD extensions, the vector length is scalable at the implementation level. With this mechanism, the flexibility of the extension greatly increases, since it provides the user with the capability to use smaller or larger vector lengths, depending on the application, therefore producing reusable code. This section will present two scalable SIMD extensions of note, the ARM SVE extension and the RISC-V V extension.

### 2.1.1 ARM Scalable Vector Extension

ARM's solution to provide a scalable SIMD extension to its instruction set is the SVE extension[17]. The SVE extension architectural state is composed of 32 vector registers, named *Z0* to *Z31*, extended on top of the already existing Neon registers to provide scalable containers for the supported width data elements, the element widths being 8, 16, 32 and 64 bits. The SVE extension also includes the addition of 16 predicate registers, *P0* to *P15* that are used to control the execution of the different lanes that operate on the vector elements. From these 16 predicate registers, only the first 8 are allowed in use of instruction predication, and all 16 are allowed for use in predicate only instructions. Since SVE is a scalable SIMD extension, the vector length can be chosen by the user, however the value of the vector length must be a multiple of 128 bits, up to a maximum value of 2048 bits. Consequently, the predicate length is also variable, and is 1/8th of the size of the vector length in use, serving as a byte mask that conditions the execution of given lanes, depending on the values of the bits of the predicate.

To better understand the scalable nature of SVE, and how it is used in practice, an example kernel of the SAXPY (Single Precision A times X plus Y) algorithm implemented using the SVE extension is presented in Listing 2.1. The loop preamble sets the initial vector length using the instruction *whilelt* p0.s, x4, x3, by populating the p0 predicate register through the values of registers x4 and x3. In detail, the value x4 represents the iteration variable, commonly refered as *i*, and register x3 represents the comparison value and the predicate register is populated with ones until the value in x4 is greater than or equal to the comparison value x3. This process is repeated each iteration of the loop and the iterator variable is updated using the *incw* x4 instruction. The *incx* family of instructions updates the iterator variable according to the data type being processed, which in the case of the SAXPY algorithm is the word type, corresponding to 32 bit elements. At last, the instruction *b.first .loop* controls the flow of the loop code, by performing a branch to the *.loop* tag if the iterator variable does not meet the finish condition. The condition codes needed for the *b.first* branch instruction to work correctly, i.e the predicate register, are set by the *whilelt* instruction each time it is called, and since the predication is continuous, i.e there are no zeroes interleaved with 1's, the branch instruction needs only to check the first element and check if it is active or inactive.

| saxpy: |                          |

|--------|--------------------------|

| mov    | x4,#0                    |

| while  | lt p0.s,x4,x3            |

| ld1rs  | z0.s,p0.z,[x2]           |

| .loop: |                          |

| ld1s   | z1.s,p0/z,[x8,x4,lsl #2] |

| ld1s   | z2.s,p0/z,[x9,x4,lsl #2] |

| fmla   | z2.s,p0/m,z1.s,z0.s      |

| st1s   | z2.s,p0,[x1,x4,ls1 #2]   |

| incw   | x4                       |

| while  | lt p0.s,x4,x3            |

#### Listing 2.1: SAXPY kernel implementation using ARM SVE extension.

#### 2.1.2 RISC-V Vector Extension

The SIMD solution offered by the RISC-V Instruction set, RISC-V V extension[15], was introduced to provide the data level parallelism support that is lacking from the base RISC-V ISA. Contrary to the ARM SVE extension, the architectural state added by the RISC-V extension is separate from the base ISA architecture. Consequently, 32 new vector registers, named v0 to v31, are added by the extension, that serve as containers for elements of the types inherited from the base ISA and its optional single precision and double precision floating point extensions, namely the integer and fixed point data types. In constrast with the ARM SVE extension, the RISC-V V extension demands no limitation on the maximum vector length, except it must be a multiple of the highest width element supported, providing a more flexible and easier code development platform. The vector registers can optionally be used as predicate registers to mask the execution of the SIMD instructions provided by the extension. The control of the vector length in use by the extension is managed using the vsetvli instruction. This instruction takes as arguments the vector size, in number of elements, and element size requested, calculates the actual vector size in bits needed and compares it with the implemented vector length, using the minimum of both values as the configured size for all the vectors and writes this size to the destination register. This instruction also has a grouping factor option. This grouping factor can be used to group, for example, vectors v0 to v3, such that a instruction that uses v0 as an operand will use the values of all the vectors grouped to v0 in the computation. The grouping factor argument can also be used to divide a particular vector register into multiple vectors, therefore processing more that one vector using a single SIMD instruction.

The code presented in Listing 2.2 represents an implementation of the same SAXPY kernel referenced before, however this time using the RISC-V V extension. In this case, the entire kernel is inserted in loop code, where the vector length is controlled by the *vsetvli* and the remaining loop control code uses the base ISA instructions such as the *bnez* branch instruction. The vector configuration uses an element width of 32 is used, set by the use of the argument *e32* and a grouping factor of 8, meaning that registers *v0* to *v7*, *v8* to *15* and so on are grouped together and treated as a single vector register. Contrary to the SVE example, the iterator and address calculation is done almost entirely using base RISC-V instructions, as can be seen by the use of the *slli*, *sub* and *add* instructions used in the loop code, using only the configure size, i.e the number of elements processed, from the *vsetvli* instruction.

| saxpy:    |              |

|-----------|--------------|

| vsetvli   | a4,a0,e32,m8 |

| vlw.v     | v0,(a1)      |

| sub       | a0,a0,a4     |

| slli      | a4,a4,2      |

| add       | a1,a1,a4     |

| vlw,v     | v8,(a2)      |

| vfmacc.vf | v8,fa0,v0    |

| vsw.v     | v8,(a2)      |

| add       | a2,a2,a4     |

| bnez      | a0, saxpy    |

|           |              |

Listing 2.2: SAXPY kernel implementation using RISC-V V extension.

## 2.2 Data Streaming Architectures

Over the last years, with the evolution of the semiconductor process technology, processor clock speeds have been significantly increased. In fact, this evolution of clock speed has completely overshadowed the increases in clock speed of off-chip memory, which in turn has had its improvements focused on providing larger memory capacity. Therefore, modern processors now have to deal with pipeline stall times of hundreds of clock cycles if a cache miss occurs, resulting in a large amount of wasted resources. Most modern systems rely on prefetching techniques such as cache prefetching, to attempt to mask the high latency costs of cache misses by attempting to predict and load data that will later be used by the processor, using a variety of algorithms such as sequential prefetching, strided prefetching or Access Map Patter Matching (AMPM) [2][7]. However, this type of hardware prefetching suffers from often not providing large gains to execution time. This is mainly due to the fact that cache prefetching is more effective on simple memory patterns, and struggles to predict more complex memory access patterns, where the most gains to be had from prefetching are located. To explore such gains, the use of independent components, entirely dedicated to data streaming, that can be programmed to prefetch complex memory access patterns have been proposed and tested, with favourable results. These components can be the base from where the architecture of the system is built around, or can be integrated in an already existing architecture. This chapter will present some examples of Data Streaming Architectures, focusing on multiple and single processing element architectures.

### 2.2.1 Data Streaming to Multiple Processing Elements

Systems that implement a multi-core architecture strive to explore the benefits of concurrent execution of several instructions, by offloading different sections of the program to different cores of the system. However, with the concurrent execution of several cores in the system comes the inevitable concurrent memory accesses of the different cores that exert a large amount of pressure on the memory hierarchy of shared-memory many-core systems.

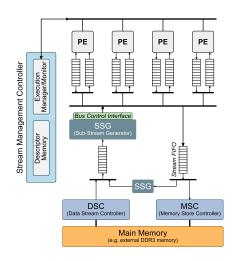

Figure 2.2: Stream Management Engine Overview, proposed by Neves et al. [9]

Consequently, a stream management engine solution [9] was proposed to minimize the number of memory accesses, maximize data throughput to the processing elements and reduce energy consumption on shared-memory multi-core systems, represented in figure 2.2. The stream management engine is comprised of several hardware structures, namely the Data Stream Controller(DSC), the Memory Store Controller(MSC), the Sub-Stream Generator(SSG), the Stream Management Controller(SMC) and a set of stream FIFO memories. The DSC, MSC and SSG all implement a Description Tree Controller that is used to generate addresses based on a stream description using stream descriptors. The Data Stream Controller then uses the calculated addresses by the DTC to issue memory read operations and generates the resulting data streams. The data received from memory is tagged with ordered serial numbers and a unique per stream identifier, so that data ordering and destination processing elements(PE's) can be recognized, and subsequently sent to an output stream FIFO. On the other hand, the Memory Store Controller uses the values calculated by the DTC to issue memory write operations, that consume data produced by the PE's. Additionally, monitoring logic is used to identify the incoming streams that should be written to main memory and streams that should be redirected to other PE's using the Sub-Stream Generator. The last of the components based on the Descriptor Tree Controller, the Sub-Stream Generator, generates sub-streams which ,instead of generating memory addresses, generate serial numbers coupled with stream identifiers. The data incoming to the SSG is the redirected with the new serial numbers and stream identifier to the destination processing elements. The inclusion of the SSG component allows the Stream Management Engine to produce sub-streams from a main stream, and redirect the sub-streams to the appropriate PE's and also to generate an output stream from multiple sub-streams, effectively implementing scatter and gather operations using data from the different PE's. Additionally, the SSG can be used to create streams from output streams from the PE's and redirect the newly created stream back to the processing elements, providing an easy mechanism for data reuse. Lastly, the Stream Management Controller is responsible for maintaining a central descriptor memory, used to describe streams, assigning descriptors to the DSC, MSC and the SSG's and

controlling the execution of the several processing elements of the system based on the data-stream flow.

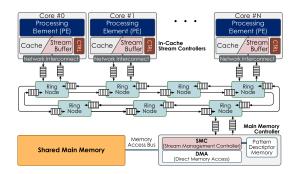

Figure 2.3: In-Cache Streaming Architecture Overview, proposed by Neves et al. [10]

An alternative streaming solution [10], proposes the use of an in-cache stream paradigm to provide a streaming architecture that can merge the benefits of traditional address-based and stream-based communication paradigms and consequently be able to tackle all types of applications, from simple to complex memory patterns. The proposed architecture is represented in figure 2.3. Contrary to the solution described above, each processing element has access to a data cache, following more traditional multi-core architectures, however the data cache implementation deviates from the standard. In detail, the processing element can view its set of n-ways present on the data cache as typical cache ways or as stream buffers, due to the fact that the cache includes two types of controllers, a typical addressbased cache controller and a stream controller. Both controllers have access to the same resources, i.e the cache ways available by the implementation, however a specific cache way is either controller by the cache controller or by the stream controller, not both simultaneously. The cache does provide a dynamic way to change the ownership of the cache ways through a register, and this ownership can be controller by the processing element associated with the given cache. When controller by the cache controller, a given cache way works using the normal tag comparison and line selection logic, however when controlled by the stream manager controller, the cache way is interpreted as a circular buffer to where data can be produced or consumed. Using this mechanism, the cache is able to change its behaviour depending on the type of communication needed, typical address-based or stream-based, and can in fact employ both communication mechanisms at the same time by shared the cache ways between the cache controller and stream controller. The data caches associated with the given processing elements are interconnected and connected to the Main Memory Controller through interconnected ring nodes that convey point-to-point and broadcast capabilities, providing the system with support for scatter and gather operations using the different PE's and shared main memory. At last, the Main Memory Controller provides the typical direct memory access support required for usual address-based communication and additionally contains a Stream Management Controller coupled with a Pattern Descriptor memory bank, used to control data-stream flow through the system, analogously to the Stream Management Controller described in the previous solution.

#### 2.2.2 Data Streaming to Dedicated Accelerator

The rise in popularity of machine-learning, computer vision, and other fields of science that require tasks with high computational intensity have started to shift the industry focus from general purpose high performance computing solutions, such as SIMD support or GPGPUs, to application and domain-specific accelerators that offer higher performance gains at the cost of generality. These application and domain-specific accelerators are usually coupled with the main processing core of the system, which provides the necessary control signals and data to the accelerator. Being that the accelerators are designed for a specific domain or application, it follows that the cost of processing should be lower that the cost of memory accesses, for a given application, making most domain-specific accelerator performance gains memory-bound.

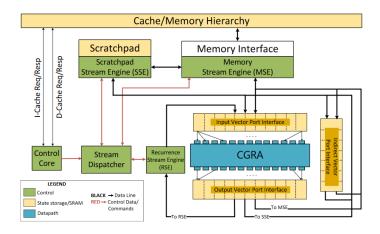

Figure 2.4: Softbrain Architecture Overview, proposed by Nowatzki et al. [11]

In order to lower the impact of memory accesses in application or domain-specific accelerators, a hardware streaming solution was proposed by Nowatzki et al. and a microarchitecture, illustrated in figure 2.4, was developed to evaluate its performance. The Softbrain microarchitecture is composed of five main elements, the Control Core, Stream Dispatcher, Stream Engines, Vector Ports and the Coarse Grained Reconfigurable Architecture (CGRA).

The Control Core is a low-power single-issue inorder core whose purpose is to generate streamdataflow commands to the stream dispatcher, i.e it acts as a programmer of the stream dispatcher. The low power and low area requirements are due to the simple function the core has to serve, since it is not a general purpose computing core.

The Stream Dispatcher Unit then processes the commands from the Control Core and controls the concurrent execution of the stream engines of the architecture, tracking resource dependencies and issuing commands when needed. There are a total of three stream engines that need to be controlled by the Stream Dispatcher Unit, the Memory Stream Engine, the Scratchpad Stream Engine and the Recurrence Stream Engine. The Memory Stream Engine processes streams and in turn issues the respective read and write requests to main memory, while also producing and consuming its values to/from the Vector Port Interfaces. The Scratchpad Stream Engine processes streams that access the Scratchpad memory instead of main memory, effectively allowing for reuse of loaded data. This scratchpad memory is populated by the use of store streams that use data from the Output Vector Port Interface. At last, the Recurrence Stream Engine is used for immediate reuse of data without memory storage, i.e the data is forwarded from the Output Vector Port directly to the Input Vector Port after being processed by the Recurrence Stream Engine.

The several stream engines present in the microarchitecture share data between themselves and with the CGRA through the Vector Port Interfaces. The Input Vector Port Interface stores incoming data from streams until the CGRA is ready to consume the data for the computation, while the Output Vector Port Interface stores the result of the computation performed by the CGRA until it is ready to be consumed by an outgoing stream. An additional interface, named Indirect Vector Port Interface, is used to store the streaming addresses of indirect loads or stores.

Lastly, the Coarse Grained Reconfigurable Architecture is a domain-specific accelerator that eanbles pipelined computation of dataflow graphs using a mesh of processing elements, where each processing element contains a set of pipelined functional units.

When comparing the core + acceleration solution with the many-core solutions described previously, it is clear that some of the techniques are reused, regardless of the target architecture. These techniques are the use of a dedicated Stream Controller, the use of buffering memory modules, such as stream FIFOS, to allow prefetching of data, communication buses that allow for scatter and gather operations and hardware support for data reuse to reduce memory accesses.

## 2.3 Unlimited Vector Extension

Figure 2.5: Saxpy example kernel implementations using ARM SVE, RISC-V V and the UVE extension[4]. Instructions with shaded background represent loop overhead.

Section 2.1 of this chapter explained the advantages of a SIMD adopting a scalable aproach, i.e the extension makes no assumptions nor limits the maximum vector length, facilitating the vectorization

and providing more flexibility to the produced code. However, both scalable solutions analysed so far in this thesis express a fundamental drawback that limits the theoretical performance gains achievable, the drawback being the large instruction overhead required to set up the processing of the required data elements. The instruction overhead manifests itself in the form of indexation, loop control and memory access instructions, which in fact can, in most cases, represent the majority of the loop code (shaded instructions illustrated in figure 2.5), therefore lowering processing throughput by wasting processor resources.

The Unlimited Vector Extension [4] is a custom scalable single instruction multiple data extension developed for the RISC-V instruction set architecture, created with the main purpose of reducing the number of overhead instructions in loop code in order to extract more performance gains out of data level parallelism. To this end, it uses a set of hierarchically ordered set of descriptors to describe memory access patterns. These descriptors are defined by user code, using the stream instructions of the UVE extension, at the loop preamble, as can be seen in figure 2.5. The decoupling of the memory instructions from the loop code is achieved by allowing a Stream Engine to process the descriptors defined in the prefetch instructions and stream the relevant data to/from the core. This decoupling can be done without losing flexibility in the type of memory accesses possible, since complex memory patterns can still be supported by conjugating several types of descriptors in a hierarchical fashion.

#### 2.3.1 Memory Access Representation

The UVE extension uses a memory access representation based on stream descriptors to describe the sequence of addresses that comprise accesses to array-based variables. This model follows the structure of nested for loops used in regular code, in order to make the transition from non-vectorized code with no prefetching to UVE code easier of both understand and perform, either by hand or by the compiler.

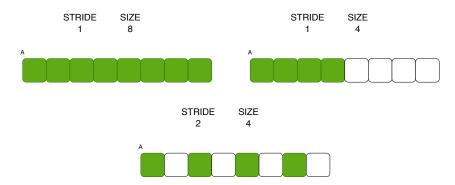

Figure 2.6: One dimensional access examples.

Using regular C code, one could represent an one dimensional access to memory using a single for loop, as illustrated in Listing 2.3. This access makes use of three fundamental variables, the base address of the variable A, the stride of the memory access and N, the size of the memory access.Consequently, the UVE representation for a one dimensional access is a descriptor, called base stream descriptor, that is represented by a three value tuple. The tuple that represents the base

stream descriptor can be used to calculate memory addresses by applying it to a simple affine function,  $address_i = base\_address + i * stride, i = 0, .., N - 1$ . By using this internal representation, several memory access patterns are possible, by varying the base address, size and stride variables. Some example accesses are represented in figure 2.6.

Figure 2.7: Two dimensional access examples.

The use of a single base stream descriptor can be used to represent a multitude of one dimensional accesses, depending on the values of the tuple variables, however it can not be used to represent multi-dimensional memory access patterns. Therefore, to provide support for a n-dimensional memory access pattern, the UVE extension employs a hierarchical organization of several stream descriptors. The stream descriptors are combined using a linear cascade scheme, analogous to the nested for loop method, where a descriptor corresponding to dimension *i* is used to calculate an offset, using a affine function, that is then added to the offset of the descriptor associated with dimension *i-1*. This method is effectively linearly combining the affine functions off all the base descriptors used to describe the memory access. Consequently, the level of flexibility provided is far greater when compared with the use of a single base descriptor, since instead of 3 variables that can be tuned to create the desired memory access pattern. Some examples of memory patterns using two cascaded base descriptors are illustrated in figure 2.7.

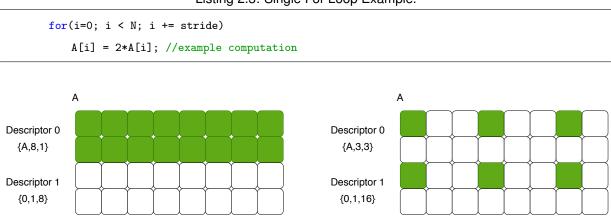

Figure 2.8: Lower triangular and Indirect Access Examples.

Whilst the hierarchical organization described in the previous paragraph does indeed provide greater

flexibility that the use of a single descriptor, there are still some types of memory patterns that the descriptor tree cannot represent, as is. Lets take as an example the first for loop represented in Listing 2.4. This loop represents a lower triangular access pattern to matrix A by the use of an inter loop dependency. In this case the size value of the inner loop is modified by each iteration of the outer loop. To deal with these inter loop dependencies, the UVE extension provides a new mechanism called static descriptor modifiers. A static descriptor modifier is represented by a tuple comprised of four elements. The first element is the target, which is as an identifier of the descriptor parameter to modify. The second and third elements are the behavior and displacement of the modifier. The behavior defines the operation to be executed, i.e addition or subtraction, and the displacement is the value used by the operation to update the parameter value. The final value of the tuple is the size of the static descriptor modifier and it specifies the total number of iterations for which the modification should occur.

The second for loop of Listing 2.4 provides yet another example of a memory access pattern that cannot be described only with the use of base descriptors. In this case, the array B is not directly indexed by the index variable of the for loop but is instead indexed by the value present in slot i of array A, i.e array B is indirectly indexed using array A and index variable i. In order to represent the behavior of indirect indexing in the stream descriptor architecture, the UVE extension describes another type of tuple called indirect descriptor modifier. It is composed of 3 values, the first and second values are the target and behaviour of the modifier, just like in the static descriptor modifier, however the third value of the tuple is a pointer to the origin data stream. The indirect descriptor modifier does not need a size value in its tuple since we are associating the origin stream with the target stream and consequently the sizes of the target stream depends on the size of the origin stream. The behavior value of the indirect stream modifier encodes the following operations:

- *add*: the displacement value resulting from the origin stream is added to the target stream parameter each iteration.

- *sub*: the displacement value is subtracted to the target parameter.

- value: sets the target value to the value resulting from the origin stream.

A visual representation of the examples present in Listing 2.4 that illustrate the use of the static and indirect descriptor modifiers can be observed in figure 2.8. The memory pattern on the left makes use of the static descriptor modifier to modify the size of the inner base descriptor by incrementing it every iteration, resulting in a lower triangular pattern. The memory patter on the right makes use of the values from vector A, resulting from the origin stream, as the index to access values in vector B, using the indirect descriptor modifier. It should be noted that, to modify a parameter associated with dimension i, the corresponding modifier should be associated with dimension i+i.

Listing 2.4: Inter loop dependency and indirect indexing examples.

```

/* Lower Triangular Access, Inter Loop Dependency*/

int K = 0;

for(i=0; i<N; i++)</pre>

```

```

{

K++;

for(j=0; j<K; j++)

{

A[i*N + j];

}

}

/*Indirect Indexing of array B*/

for(i=0; i<N; i++)

B[A[i]];</pre>

```

#### 2.3.2 Architectural State

Since the UVE extension is at its core a SIMD extension, it defines two new register files, one composed of vector registers and another composed of predicate registers. However, contrary to other SIMD extensions, UVE also defines a stream interface to the vector instructions due to the fact that the ISA extension supports data streaming.

The vector register file comprises 32 vector registers, named *u0* to *u31*, analogous to the scalar register file defined by the RISC-V base ISA. The vector registers are not limited by the extension to any particular maximum size, due to the extension adopting a scalable approach to vector. The only restriction applied to the maximum size of the vector is that it must be a multiple of the largest element width allowed, which in this case is 64 bits. However a minimum size allowed for the vector registers is defined. This is the case because the vectors are comprised of individual elements, and the elements widths supported by the extension are byte(8 bits), half-word(16 bits), word(32 bits) and double word(64 bits). Consequently the minimum size allowed for a vector register is the maximum width of the supported elements, which in the case of the UVE extension is 64 bits. If, for example, one decides to only support up to 32-bit elements then the minimum size requirement can be relaxed to 32 bits since 64-bit wide elements are not supported.

#### Vector Register

| Vector Data   | Element<br>Width                  | Valid Index     |

|---------------|-----------------------------------|-----------------|

| Vector Length | $\leftarrow$ 2 bits $\rightarrow$ | < Index Length> |

Figure 2.9: Vector Register Example Layout.

Due to the fact that the vectors are scalable in size, some additional meta-information needs to be kept for each register to support the scalable behavior. Consequently, each vector register holds not only the vector data but also the width of the elements in the vector and a valid index value. The element width informs the processor about the widths of the elements in the vector so it can process them correctly in the execute stage. The valid index informs the processor about how many elements in the vector are valid, assuming all valid elements are contiguous in the vector. By using these two values, each vector register has the flexibility of processing elements of different size and also store vectors of different size with the use of the valid index value. A simple illustration of the contents of a vector register is represented in figure 2.9. The element width data is encoded in 2 bits since only 4 possible element widths are available while the index width depends on the vector length of the implementation.

The predicate register file, contrary to the RISC-V scalar register file and the vector register file, features only 16 predicate registers, named p0 to p15, however only the first 8 registers, p0 to p7, are used to predicate arithmetic and regular memory instructions. The remaining registers, p8 to p15, are used in predicate instructions that configure values for the first 8 registers or for context saving if needed. Additionally, predicate register p0 is hardwired to 1 removing the need for pre-configuration of a predicate register if normal execution is pretended (no predication).

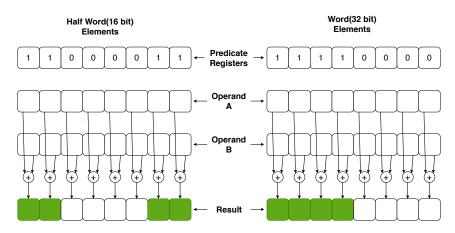

Figure 2.10: Predication Examples.

The width of a single predicate register is dependent of the size of the vector length of the implementation. In fact, the data of the predicate register acts as as a byte mask that selects which lanes should execute and which lanes should not (no operation), so the precise width of a predicate register is *Vector\_Length/8*. A couple examples of predication using different element widths are illustrated in figure 2.10, considering a vector length of 64 bits. The left example shows a predication on half word elements and consequently the bits of the predicate register that are set are always in pairs, since each bit represents a byte of the vector. With this predicate register, only the first and last half words of the vector are changed to the result of the operation (highlighted in green) and the rest of the half words remain unchanged. In the right example, the element width is now 32 bits, and the predicate register is allowing the operation on the first word, but not on the second word of the vector.

Due to the fact that the UVE extension provides ISA level support for data streaming, it defines a streaming interface that must be followed for the correct functioning of the streaming instructions provided. The streaming interface makes use of the already existing vector register file, by associating each stream with a specific vector register. Therefore, when a compute instruction reads or writes to a specific vector register, if that register is associated with a data stream, then the instruction consumes or produces, depending if the stream is a load or store stream, the vector data from or to the stream. This instruction behavior is destructive, meaning that if an instruction reads the contents of, for example, vector register *u1* and this register is associated with a load stream, then the data read is permanently consumed and cannot be accessed again using the stream interface. If the consumed data is to be accessed again, then the processor must save it in an intermediate register or memory address of choice. This behaviour eliminates the need of dedicated step instructions for streams since consuming or producing values from/to a configured stream automatically iterates the associated stream. Associating each active stream with a vector register provides advantages due to the fact that no further decoding bits are necessary in the instructions to read/write to streams and not exception mechanisms are needed when reading or writing to a non-configured stream due to the fact that if the stream is not configured, then the instructions simply reads/writes from/to the normal vector register is question.

#### 2.3.3 Streaming Instructions

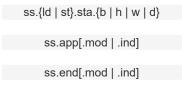

Due to the fact that the UVE extension provides support for ISA level data streaming, it provides a set of instructions to control the configuration and flow of streams. These instructions can be divided into several groups, mainly configuration instructions, stream control instructions and loop control instructions and allow the user code full control over the prefetching mechanisms, memory patterns and loop flow.

#### **Configuration Instructions**

ss.ld.{b | h | w | d}

### ss.st.{b | h | w | d}

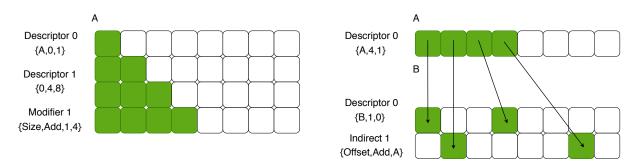

Figure 2.11: Simple 1D stream configuration instructions.

The configuration instructions give the user access to configuration of a variety of memory patterns by making use of the descriptors explained in the previous section. The simplest memory pattern available is a one dimensional memory pattern but, despite being simple, it is one of the most common memory patterns and consequently the UVE extension provides a pair of instructions to define one dimensional streams, illustrated in figure 2.11. The *ss.ld* instruction creates a load stream following a one dimensional pattern defined by the tuple values supplied by the user in the operand registers while the *ss.st* instruction creates a store stream. Both instructions require a prefix that provides information about the element width of the stream to be configured, *b* for byte elements, *h* for half word elements, *w* for word elements and *d* for double word elements.

Figure 2.12: Multiple dimension stream configuration instructions.

To make use of the full potential of the hierarchical descriptor model representation of memory patterns explained in the previous section, mainly multi-dimensional memory patterns and modifiers, UVE provides access to three types of stream configuration instructions, represented in figure 2.12. The instruction *ss.sta* creates a stream, with direction chosen by the prefix *ld* or *st*, and appends the descriptor associated to the first dimension, much like the *ss.ld* or *ss.st* instructions explained before, however in this case the stream configuration is not terminated and more descriptors can be added. To add more descriptors to the stream in configuration, the user can make use of both the *ss.app* and *ss.end* instructions. This *ss.app* instruction appends a descriptor to a stream, with the option of appending an indirect or static modifier instead if the prefix *.ind* or *.mod* are present, respectively. The *ss.end* instruction behaves just like the append instructions, with the exception that the *ss.end* instruction signals the termination of the configuration phase of the stream in question and consequently no further descriptors or modifiers can be added.

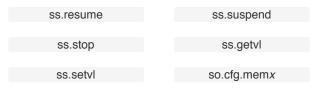

#### Stream control Instructions

Figure 2.13: Stream control instructions.

When a UVE stream has been successfully configured, it will start prefetching data to the processor immediately, however the need to stop or suspend a stream with a user command might be necessary for the correct program flow, consequently the UVE extension provides a set of stream control instructions that give the user control over the stream state and data path. The instructions *ss.resume*, *ss.suspend* and *ss.stop* control the stream state. If the user requires a stream to be suspended for a period of time, then *ss.suspend* can be used and the stream can then later be resumed with the *ss.resume* instruction. If, however, the user requires an early termination of a stream, i.e the termination of a stream that has yet to complete the full memory pattern described, then the *ss.stop* instruction should be used. The UVE extension also allows the query and manipulation of the vector length used by each stream with the use of the *ss.getvl* and *ss.setvl* instructions, respectively. Lastly, the *so.cfg.memx* instruction configures data path to be used by the stream. In particular, the prefix *x* point to the usage of the level *x* memory level of the system in question. This instruction allows the user to decide if the stream in question benefits from the use of the cache levels of the system, to make use of the latency reduction of accesses, or direct access to main memory, in order to prevent cache pollution.

#### **Loop Control Instructions**

Data streaming mechanisms provide the most benefit when used in user code that iterates over memory addresses using loop code. Consequently the UVE extension provides instructions to control the flow of such loops using stream dimension information. Two types of loop control instructions are

### so.b.[n]c

#### so.b.[n]dc

#### Figure 2.14: Stream loop control instructions.

provided, in the form of conditional branches, and each of the types includes a negation variant using the optional *n* prefix. The *so.b.c* instruction performs a branch operation if the stream in question ended, while the *so.b.dc* performs a branch operation if the dimension of the stream indicated by a register operand ended. By using this set of loop control instructions, a fine control over stream data and processing based on stream dimension can be achieved, analogously to nested for loop behavior.

# 2.4 Summary

This chapter started out by describing some of the state of the art scalable SIMD solutions, namely the ARM SVE extension and the RISC-V V extension, and providing vectorized code examples for each solution. Then, in the second section, an analysis of proposed streaming architectures as done, focusing on architectures streaming to multi-core systems and core-accelerator systems. Finally, the third chapter explained in detail the novelty UVE RISC-V extension, which combines scalable SIMD instructions with data streaming instructions, to provide ISA level data streaming and parallel processing support.

# **Chapter 3**

# **Base RISC-V Softcore Processor**

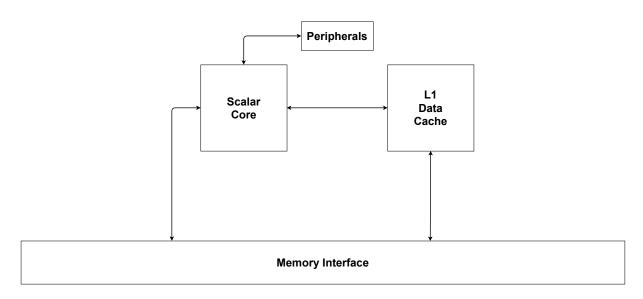

Figure 3.1: Base RISC-V Processing System.

The Configurable RISC-V Softcore Processor [16] was developed at Instituto Superior Técnico, as part of João Rodrigues's Master Thesis and had the objective of providing multi-cycle functional unit and peripheral support to a RISC-V softcore, features that were lacking in others RISC-V Cores at the time, consequently it was used as a baseline for this work. In figure 4.1, the base system is illustrated, being composed of three main elements, the Scalar Core, which implements a subset of the RISC-V ISA, a level 1 data cache with a direct connection to main memory via the memory interface, and a set of memory mapped peripherals, namely a UART interface, a cycle counter and a timer.

# 3.1 Scalar Core

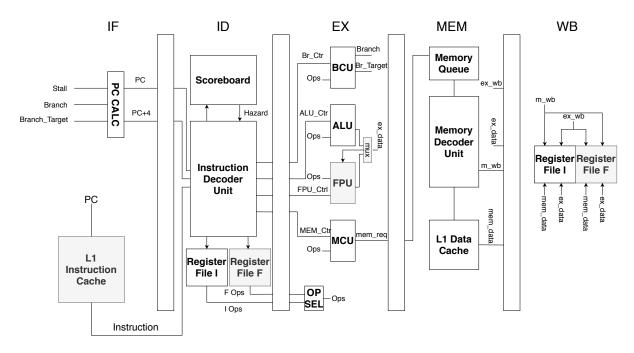

The integral part of the system used as a starting point is the Scalar Core, which implements the 32 bit base RISC-V instruction set plus the Integer Multiply and Divide extension. In figure 3.2, one can observe the architecture diagram of the Scalar Core. The core implements an in-order 5 stage pipeline where the ID stage features a Dependency Handler Unit, in this case a Scoreboard, to manage hazards

Figure 3.2: RISC-V Scalar Core.

that originate from the use of multi-cycle units, such as the Multiplier and Divider, and from memory accesses.

#### 3.1.1 Instruction Fetch Stage

The Instruction Fetch (IF) stage is responsible for calculating the address of the next instruction using the current Program Counter value or, in case of a branch, the branch target value calculated in the Execute stage. In the original system, the core had a built in BRAM memory that stored the program instructions and as such, the program counter was used to access the BRAM data each clock cycle to provide the next instruction to the Instruction Decode stage.

#### 3.1.2 Instruction Decode Stage

The instruction loaded from the integrated BRAM in the IF stage is forwarded to the Instruction Decode (ID) stage. In this stage a Instruction Decoder Unit decodes the necessary signals to control the Execute and Memory stages in order to perform the instruction requested by the IF stage. In parallel, the Scoreboard unit, represented in figure 3.3, analyses the operands and destination registers of the provided instruction and calculates if a hazard will occur. This hazard flag is then used by the ID stage to stall the pipeline if indeed a hazard is detected. The types of hazards relevant for this in-order pipeline are Read After Write (RAW), Write After Write, due to multi-cycle units, and Structural hazards. Finally the ID stage includes the Integer Register File, which holds the register operands needed by the Execute Stage.

| Dog  | Latency |     |     |     |   |   |   |   | Mem.        |      |

|------|---------|-----|-----|-----|---|---|---|---|-------------|------|

| Reg. | L       | L-1 | L-2 | L-3 |   | 4 | 3 | 2 | 1           | wem. |

| R0   | -       | -   | -   | -   | - | - | - | - | -           | -    |

| R1   |         |     |     |     |   |   |   |   |             |      |

| R2   |         |     |     |     |   |   |   |   |             |      |

| R3   |         |     |     |     |   |   |   |   |             |      |

| R4   |         |     |     |     |   |   |   |   |             |      |

| R5   |         |     |     |     |   |   |   |   |             |      |

| R6   |         |     |     |     |   |   |   |   |             |      |

| R7   |         |     |     |     |   |   |   |   |             |      |

| R8   |         |     |     |     |   |   |   |   |             |      |

| R9   |         |     |     |     |   |   |   |   |             |      |

| R10  |         |     |     |     |   |   | 1 |   |             |      |

|      |         |     |     |     |   |   |   |   |             |      |

| R22  |         |     |     |     |   |   |   |   |             |      |

| R23  |         |     |     |     |   |   |   |   |             |      |

| R24  |         |     |     |     |   |   |   |   | ,<br>,<br>, |      |

| R25  |         |     |     |     |   |   |   |   |             |      |

| R26  |         |     |     |     |   |   |   |   |             |      |

| R27  |         |     |     |     |   |   |   |   |             |      |

| R28  |         |     |     |     |   |   |   |   |             |      |

| R29  |         |     |     |     |   |   |   |   |             |      |

| R30  |         |     |     |     |   |   |   |   |             |      |

| R31  |         |     |     |     |   |   |   |   |             |      |

Figure 3.3: Configurable Softcore Processor Scoreboard Overview [16]

#### 3.1.3 Execute Stage

After the instruction is successfully decoded and no hazard is detected, the operands are loaded from the Integer Register File and used as inputs to the EX, along with some control signals, mainly the ALU and MEM control Signals. The Execute stage features an ALU capable of computing all the instructions present in the RISCV32IM subset of the RISC-V instruction set, including multi-cycle multiplier and divide units. It also supports a branch control unit, which calculates the branch target address and the branch result, based on the condition specified by the branch instruction. The core uses a static branch not taken prediction mechanism, meaning that the core always assumes the branch is not taken and fetches the next program instruction. If a branch is indeed taken, the pipeline will be flushed, voiding all instructions that were fetched during speculative regime, else the pipeline will continue with normal operation. The EX stage also includes a memory control unit that calculates the memory address based on ID control values and forwards the results to the Memory (MEM) stage. One should note that non-memory instructions skip the Memory stage of the pipeline and are directly forwarded to the Write Back stage.

#### 3.1.4 Memory Stage

If the decoded instruction is a load/store instruction, then the appropriate address is calculated in the EX stage and the relevant control signals are forwarded to the Memory Stage. This stage implements a request buffer, meaning that several memory requests will not stall the pipeline due to the fact that they

can be stored in a buffer for later processing. When a request is read from the buffer, the MEM stage identifies if the request is a store or load request and assembles the required signals to form a request to the Data Cache. The MEM stage then waits for the data cache response, i,e the data requested by the core, or the confirmation that the data was stored, and only after the response is acknowledged does the MEM stage read the next request from the buffer. This ensures that the requests are handled in order and that no other handler units need to be developed to reorganize memory requests.

#### 3.1.5 Write Back Stage

After the data has been successfully computed in the EX stage or loaded in the MEM stage, the Write Back Stage (WB) will save the data in the appropriate register, according to the instruction. The Integer Register File was built to have support for 2 separate write channels, the memory write channel and the execute write channel, with the later having priority over the other in case of simultaneous write. However, this mechanism is implemented as a fail-safe as it indicates the presence of a WAW, which should be handled by the Scoreboard, by delaying the hazard generating instruction.

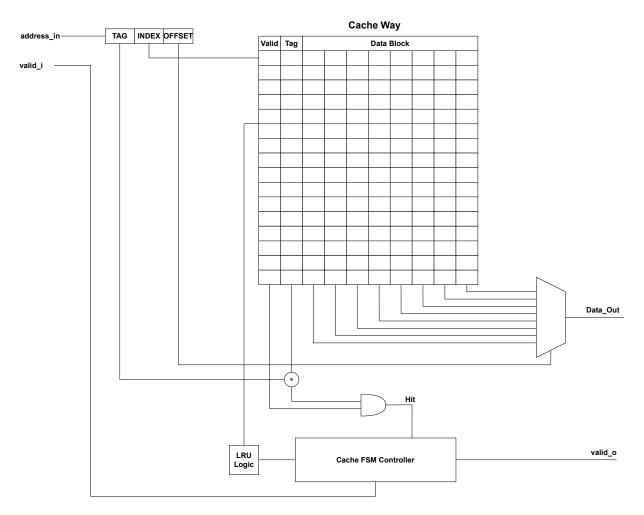

### 3.2 L1 Data Cache

Since the Scalar Core supports load and store request from memory, the original system contemplated a level 1 Data Cache, with the purpose of drastically reducing load and store latency, since accesses to main memory can be avoided if the data was previously fetched and stored in the data cache.

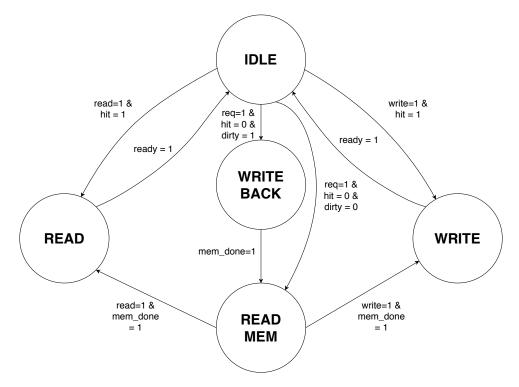

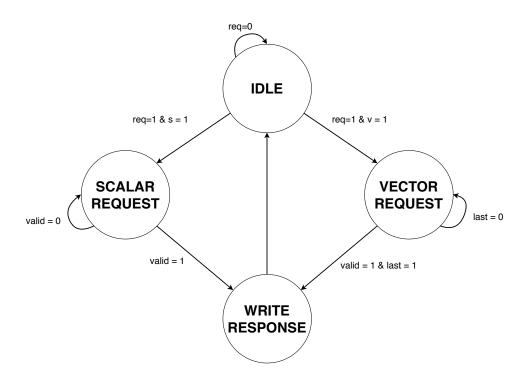

Figure 3.4: Cache WriteBack/WriteAllocate FSM.

The cache can be configured to use two different access mechanisms: direct-mapped or 2-way set associative using the Least Recently Used(LRU) data replacement policy, both with cache line size of 256 bits, number of lines equal to 16 and each line featuring a valid and dirty bit. Both these configurations use the Write-Back/Write Allocate policy, controlled by a cache controller that implements the finite state machine model present in figure 3.4. The cache starts out in the IDLE state and transitions if a read or write request is performed. If the given request results in a cache hit, then in 1 clock cycle the data is read/written depending on the request and the state returns to IDLE. If the request results in a cache miss, then either the cache line in question is dirty, i.e has already been written to by the processor, or it is not dirty. If the cache line is dirty, the state transitions to WRITE BACK and the contents of the cache line are written to main memory. If the cache line is not dirty or after the data has been written to main memory in order for it to be read or written to, according to the incoming request. Using this state machine, one can reduce the number of requests to main memory, comparing with the write through policy, and reduce memory request latency as a result.

### 3.3 Peripherals

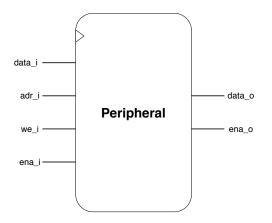

Figure 3.5: Peripheral Interface Diagram.

The original system provided support for several memory mapped peripherals, such as an UART interface, a cycle counter and a timer. On the original architecture, additional peripherals can be added, by implementing the interface illustrated in figure 3.5, where the *data\_o* and *ena\_o* signals are mandatory only if the peripheral supports read transactions.

The UART peripheral provides an interface for serial communication using the RX channel for reading and TX channel for writing. This interface can be used to communicate with other peripherals or the host system, if it exists. The cycle counter implemented in the system uses the processor clock to keep track of how many clock cycles have elapsed. The counter can be used to measure cycles of execution for benchmark purposes. The last peripheral, the timer, uses a clock with known frequency to calculate elapsed time. With this peripheral, one can measure execution times by requesting the timer value at the start and end of execution and calculate the difference between the two values. All the peripherals are accessed by normal load or store instructions, meaning that they are mapped to the processor memory space. The start and final address values of each peripheral are represented in table 3.1. Since the peripherals are memory mapped and the entire address range of the processor is not occupied, the system does support inclusion of additional peripherals, if needed. No changes to the core are necessary, only the address decoder must be updated to reflect the new memory mapped peripherals to be added.

| Peripheral    | Start Address | Final Address |  |

|---------------|---------------|---------------|--|

| UART          | 0xFFFFFFF0    | 0xFFFFFFFC    |  |

| Cycle Counter | 0xFFFFFF00    | 0xFFFFFF04    |  |

| Timer         | 0xFFFFFF80    | 0xFFFFFF84    |  |

Table 3.1: Peripheral Address Ranges.

# 3.4 Summary

This chapter introduced a system implementation composed of a softcore that supports the RV32IM subset of the RISC-V ISA, represted in the first table of appendix A, a data cache and memory mapped peripherals. The system was implemented in a Virtex UltraScale+ VCU1525 FPGA obtaining the resource usage and operating frequency values represented in figure 3.6.

| Design              |       | Frequency |        |       |     |       |

|---------------------|-------|-----------|--------|-------|-----|-------|

| Design              | LUT   | LUTRAM    | FF     | BRAM  | DSP | [MHz] |

| Core                | 5800  | 2407      | 2346   | 0     | 0   | 250   |

| Core (+ MUL)        | 5921  | 2434      | 2439   | 0     | 4   | 250   |

| Core (+ DIV)        | 7234  | 2419      | 5230   | 0     | 0   | 250   |

| Core (+ MUL + DIV)  | 7336  | 2446      | 5307   | 0     | 4   | 250   |

| Core + XDMA         | 28856 | 2367      | 31931  | 75    | 4   | 200   |

| Core + XDMA + Cache | 33137 | 3699      | 33872  | 59    | 4   | 100   |

| Core + XDMA +       | 94343 | 9924      | 102055 | 110.5 | 7   | 100   |

| Cache + DRAM        | 0-040 | 0024      | 102000 | 110.5 | ,   | 100   |

Figure 3.6: Resource usage and operating frequency of the different configurations of the Configurable Softcore Processor [16]

# **Chapter 4**

# **Proposed System Architecture**

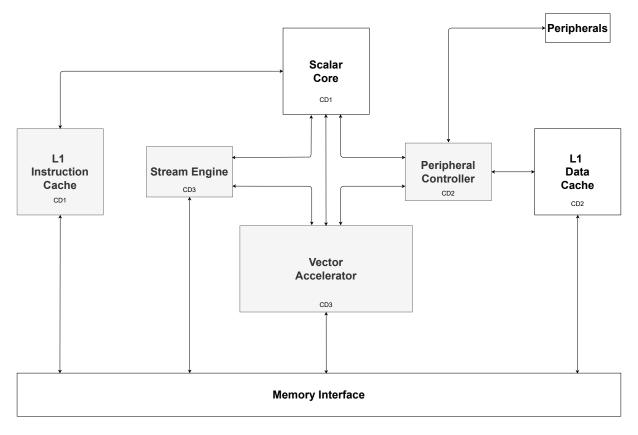

Figure 4.1: RISC-V Streaming Processing System.

This chapter will explain in detail the modifications to the base RISC-V system (figure 3.1) and the architecture of the new hardware blocks introduced by this work, mainly the Streaming Engine, the Vector Accelerator, the Peripheral Controller, and the L1 Instruction Cache, illustrated in figure 4.1. The system provides support for three clock domains, consequently each component has a corresponding clock domain, also represented in figure 4.1. The Scalar Core was modified to have the capabilities of programming and controlling both the Streaming Engine and the Vector Accelerator. The Streaming Engine processes streams configured by the Scalar Core, interfaces with main memory to load or store the data required, and interfaces with the Vector Accelerator to produce/consume data to/from SIMD

instructions. The Vector Accelerator provides the necessary hardware to support Single Instruction Multiple Data instructions and a stream memory bank to interface with the Streaming Engine in order to process stream data. At last, the Peripheral Controller performs memory request arbitration between the Scalar Core and the Vector Accelerator, and further decodes the address to redirect the request to either the level 1 Data Cache or to the relevant memory mapped peripheral.

### 4.1 Vector Accelerator

Figure 4.2: Vector Accelerator Pipeline Diagram.

In order to add support for SIMD instructions from the UVE extension, two choices were considered. The first choice considered was to modify the Scalar Core to support the new instructions. Several changes should be made such as the inclusion of a new vector register file and addition of the required functional units and bus width modifications to support vector operations. The second choice was to develop a separate accelerator to support the new instructions. With the latest approach, the new accelerator can run in parallel with the scalar core. Moreover this approach has the added benefit of avoiding SIMD support to affect the critical path of the previously developed Scalar Core, as the accelerator can simply operate with a different clock. The drawback to this method is the need to add inter clock communication between the core and accelerator, which adds to the complexity of the overall design. In this work, the second option was chosen and a Vector Accelerator was designed.

The Vector Accelerator implements a 4 stage in-order pipeline architecture that is controller by the Scalar Core via a asynchronous fifo buffer. It supports a subset of the UVE extension, represented in appendix B, instructions and as such features programmable vector width, as explained in 2.3. The simplified diagram of the accelerator pipeline is illustrated in figure 4.2.

#### 4.1.1 Instruction Decode Stage

The ID stage of the Vector Accelerator receives the instruction from the Scalar Core through a FIFO instead of an instruction cache or integrated memory. As such, the ID stage stalls the pipeline if the FIFO is empty, since there are no instructions to decode. If a valid instruction is ready to be read on the FIFO, then the instruction is decoded and the scoreboard computes if a hazard would be caused by issuing the instruction. If a hazard is indeed detected, the ID stage will stall the pipeline and the instruction will not be read from the FIFO since it needs to be available until the hazard is resolved. The ID stage also controls the Vector Register File and Predication Register File using decoded signals from the incoming instructions and provides the values to the Execute stage.

Figure 4.3: Stream Memory Bank I/O.