# Breaking security of crypto systems using cache side-channel attack

### **Bruno Miguel Simões Lopes**

Thesis to obtain the Master of Science Degree in

### **Information Systems and Computer Engineering**

Supervisors: Prof. Ricardo Jorge Fernandes Chaves Prof. Tiago Miguel Braga da Silva Dias

### **Examination Committee**

Chairperson: Prof. Francisco António Chaves Saraiva de Melo Supervisor: Prof. Ricardo Jorge Fernandes Chaves Member of the Committee: Prof. Alberto Manuel Ramos da Cunha

January 2021

## Abstract

The focus of this research pretends to acknowledge the concept and structure of a typical side-channel attack and its variations. In a second phase, to dive into cache side-channel attacks that use timing records as side-channel information, for uncovering the secret key used by a victim cryptographic application. Thus, we implement an enhanced attack, based on Prime + Probe strategy, relying on the time differences between L1-D and the other cache levels latency. Our attack requires an unprivileged attack process running in the same CPU core as our victim, using SMT technology. The attack process can choose the plaintext values to input into our victim. Our victim application uses the inputted data to perform an AES encryption using OpenSSL functions.

Additionally, we evaluate the success of the performed attack, using the amount of key information discovered, according to different vectors, such as the amount of side-channel information produced.

## **Keywords**

Cache; Side-channel attack; AES.

## Resumo

O propósito desta pesquisa visa entender o conceito e estrutura de um típico ataque side-channel e respectivas variações. Numa segunda fase, aprofundar os ataques side-channel na cache que usam registos temporais como informação side-channel, para descobrir uma chave secreta que vai ser usada por uma aplicação criptográfica víctima. Assim, nós implementámos um ataque com base na estratégia Prime + Probe, que usa as diferenças temporais na latência entre a cache L1-D e outros níveis de cache. O nosso ataque requer um processo não privilegiado atacante a correr no mesmo núcleo CPU que a nossa víctima, usando a tecnologia SMT. O processo atacante pode escolher o valor do texto de input na nossa víctima. A nossa víctima usa o texto recebido para realizar cifras AES usando as funções do OpenSSL.

Adicionalmente, nós avaliamos o sucesso do ataque, usando a quantidade de informação da chave secreta descoberta, de acordo com os diferentes vectores, tal como a quantidade de informação sidechannel.

## **Palavras Chave**

Cache; ataques side-channel; AES.

## Contents

| 1 | Intro | duction                                             | 1  |

|---|-------|-----------------------------------------------------|----|

|   | 1.1   | Side-channel Attack Concept                         | 3  |

|   | 1.2   | Side-channel Attack History                         | 3  |

|   | 1.3   | Goals                                               | 4  |

|   | 1.4   | Organization of the Document                        | 4  |

| 2 | Bac   | ground                                              | 5  |

|   | 2.1   | Caches                                              | 7  |

|   |       | 2.1.1 Structure                                     | 7  |

|   |       | 2.1.2 Associativity                                 | 8  |

|   |       | 2.1.3 Replacement Policies                          | 8  |

|   |       | 2.1.4 Writing Policies                              | 8  |

|   |       | 2.1.5 Cache Inclusion Policies                      | 9  |

|   | 2.2   | Simultaneous Multithreading                         | 9  |

|   | 2.3   | CPU Dynamic Frequency Scaling                       | 9  |

|   | 2.4   | Cryptographic Operations                            | 10 |

|   |       | 2.4.1 Advanced Encryption Standard (AES)            | 10 |

|   |       | 2.4.1.A Key Expansion                               | 11 |

|   |       | 2.4.1.B State Transformations                       | 11 |

|   |       | 2.4.1.C Algorithm                                   | 12 |

|   |       | 2.4.2 AES Implementations                           | 13 |

| 3 | Stat  | e of the Art                                        | 15 |

|   | 3.1   | Side-Channel Attack                                 | 17 |

|   | 3.2   | Types of Side-channel attacks                       | 17 |

|   | 3.3   | Timing Cache Side-Channel Attack on AES - Structure | 18 |

|   |       | 3.3.1 Online Phase                                  | 18 |

|   |       | 3.3.2 Offline Phase                                 | 18 |

|   | 3.4   | Types of Timing Cache Side-channel Attacks on AES   | 19 |

|   |      | 3.4.1    | Evict + Time Attack             | 19 |

|---|------|----------|---------------------------------|----|

|   |      | 3.4.2    | Prime + Probe Attack            | 21 |

|   |      | 3.4.3    | Flush + Flush Attack            | 23 |

|   | 3.5  | Counte   | ermeasures                      | 24 |

|   |      | 3.5.1    | Hardware Based Solutions        | 24 |

|   |      | 3.5.2    | Software Based Solutions        | 25 |

|   | 3.6  | Summ     | ary                             | 26 |

| 4 | Prop | bosed S  | Solution                        | 27 |

|   | 4.1  | Propos   | sed Attack                      | 29 |

|   | 4.2  | Proble   | m                               | 29 |

|   | 4.3  | Attack   | Structure                       | 30 |

|   | 4.4  | CPU a    | und OS                          | 30 |

|   | 4.5  | OpenS    | SSL                             | 31 |

|   | 4.6  | Hardw    | are Requirements                | 31 |

|   | 4.7  | Measu    | Irement Concept                 | 32 |

|   |      | 4.7.1    | Theoretical Alignment           | 32 |

|   |      | 4.7.2    | Implementation details          | 33 |

|   |      | 4.7.3    | Implications                    | 34 |

|   |      | 4.7.4    | Measurement Technology          | 35 |

|   | 4.8  | 1st Ph   | ase - L1-D T-box Mapping        | 35 |

|   |      | 4.8.1    | Applications Involved           | 35 |

|   |      | 4.8.2    | Description                     | 35 |

|   | 4.9  | 2nd Pł   | nase - Online Phase             | 42 |

|   |      | 4.9.1    | Applications Involved           | 42 |

|   |      | 4.9.2    | Description                     | 42 |

|   | 4.10 | 3rd Ph   | ase - Offline Phase             | 43 |

|   |      | 4.10.1   | Applications Involved           | 43 |

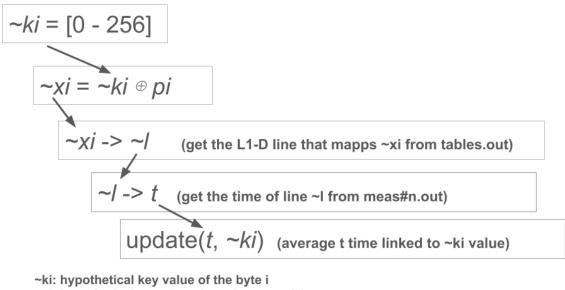

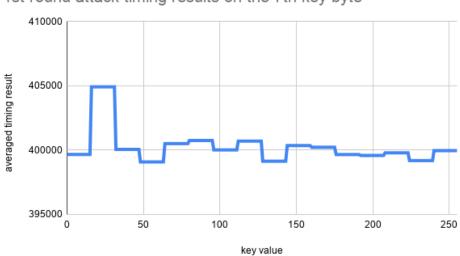

|   |      | 4.10.2   | 1st Round Attack                | 44 |

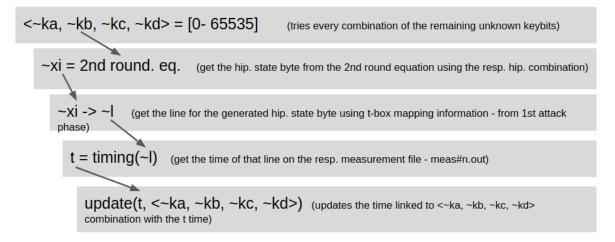

|   |      | 4.10.3   | 2nd Round Attack                | 46 |

| 5 | Eval | luation  | and Results                     | 51 |

|   | 5.1  | Result   | s Structure                     | 53 |

|   | 5.2  | Attack   | Variables                       | 53 |

|   | 5.3  | Criteria | a Vectors                       | 54 |

|   |      | 5.3.1    | Criteria Vector 1 Justification | 54 |

|   |      | 5.3.2    | Criteria Vector 2 Justification | 55 |

| Α | Cod | e of Project           | 69 |

|---|-----|------------------------|----|

|   | 6.2 | Future Work            | 64 |

|   | 6.1 | Conclusion             | 63 |

| 6 | Con | clusion                | 61 |

|   | 5.7 | Countermeasures        | 59 |

|   | 5.6 | Conclusive Results     | 58 |

|   | 5.5 | Attack Timing Duration | 58 |

|   | 5.4 | Tests                  | 55 |

# **List of Figures**

| 2.1  | CPU and volatile memory levels from [1]                                                                | 7  |

|------|--------------------------------------------------------------------------------------------------------|----|

| 2.2  | AddRoundKey                                                                                            | 12 |

| 2.3  | MixColumns                                                                                             | 12 |

| 2.4  | ShiftRows                                                                                              | 12 |

| 2.5  | SubBytes                                                                                               | 12 |

| 2.6  | Cache block containing all the first 16 elements of the T-box table $T_1$                              | 14 |

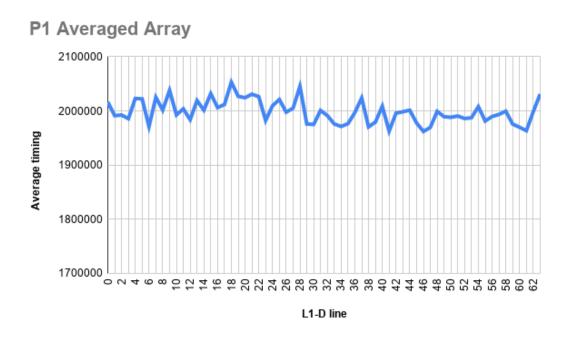

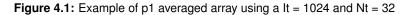

| 4.1  | Example of p1 averaged array using a It = 1024 and Nt = 32                                             | 38 |

|      |                                                                                                        |    |

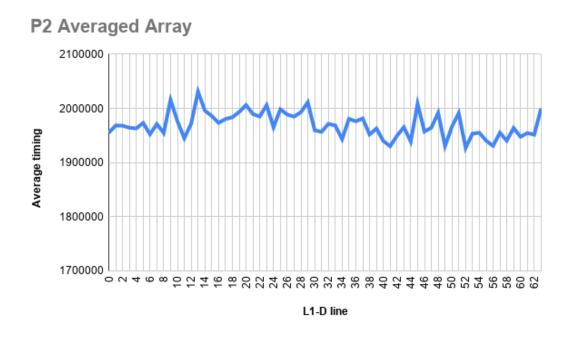

| 4.2  | Example of p2 averaged array using a $It = 1024$ and $Nt = 32$                                         | 38 |

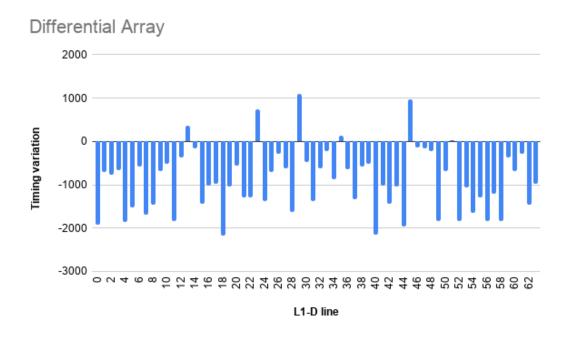

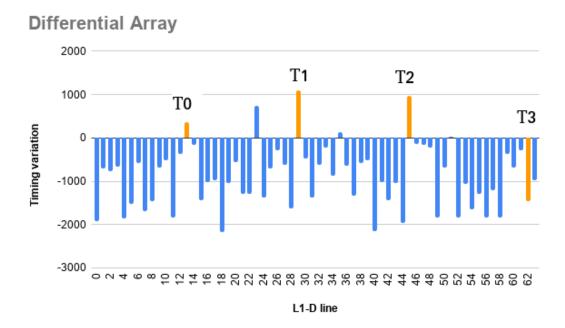

| 4.3  | Timing variations between p1 and p2 averaged arrays                                                    | 39 |

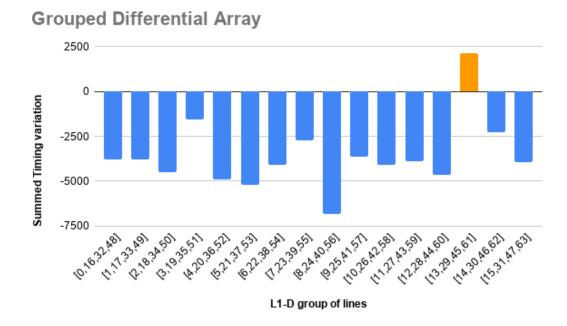

| 4.4  | Differential Array grouped by lines 16 units apart                                                     | 40 |

| 4.5  | Differential Array with the chosen group of lines highlighted                                          | 40 |

| 4.6  | Cache block containing all the first 16 elements of the T-box table $T_1$ (offset = 0)                 | 41 |

| 4.7  | Cache block half containing the last elements of table $T_0$ and the first of table $T_1$ (offset = 8) | 41 |

| 4.8  | 1st Round Attack Sub-phase                                                                             | 45 |

| 4.9  | 1st Round Attack Sub-phase, on the 7th key byte                                                        | 46 |

| 4.10 | 2nd Round Attack Sub-phase                                                                             | 48 |

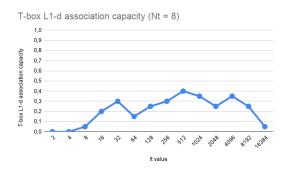

| 5.1  | Test 1, Nt = 8                                                                                         | 55 |

|      |                                                                                                        |    |

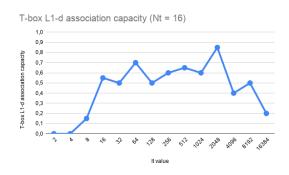

| 5.2  | Test 1, Nt = 16                                                                                        | 55 |

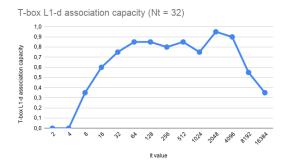

| 5.3  | Test 1, Nt = 32                                                                                        | 56 |

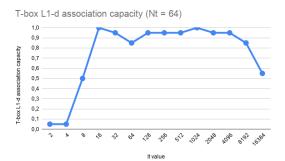

| 5.4  | Test 1, Nt = 64                                                                                        | 56 |

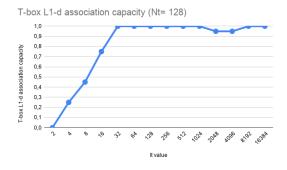

| 5.5  | Test 1, Nt = 128                                                                                       | 56 |

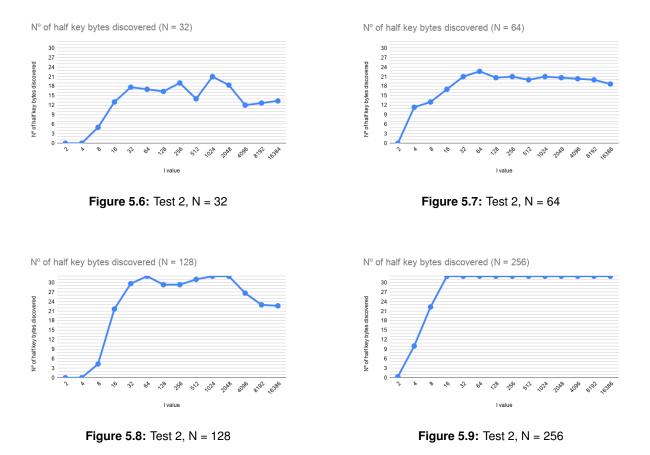

| 5.6  | Test 2, N = 32                                                                                         | 57 |

| 5.7  | Test 2, N = 64                                                                                         | 57 |

| 5.8  | Test 2, N = 128                                                                                        | 57 |

| 5.9  | Test 2, N = 256                                                                                        | 57 |

## **List of Tables**

| 2.1 | The secret keys and respective expanded key size | 11 |

|-----|--------------------------------------------------|----|

| 4.1 | Details of the CPU used                          | 30 |

| 4.2 | Operative System used                            | 31 |

| 4.3 | Files and phases of the attack                   | 49 |

| 5.1 | Attack's phase duration                          | 58 |

# **List of Algorithms**

| 2.1 | AES encryption pseudocode | 12 |

|-----|---------------------------|----|

| 4.1 | Process 1 pseudo-code     | 33 |

| 4.2 | Process 2 pseudo-code     | 34 |

# Listings

| A.1 | atk.c      | 69 |

|-----|------------|----|

| A.2 | atk_enc.c  | 75 |

| A.3 | vic_enc.c  | 77 |

| A.4 | crypto.py  | 79 |

| A.5 | aes.h      | 89 |

| A.6 | aes_core.c | 90 |

| A.7 | Makefile   | 98 |

## Acronyms

- AES Advanced Encryption Standard

- CPU Central Processing Unit

- **DES** Data Encryption Standard

- **ECB** Electronic CodeBook

- OS Operative System

- LLC Last Level Cache

- PAPI Programming Application Performace Interface

- SCA Side-channel Attack

- SMT Simultaneous MultiThreading

- RSA Rivest-Shamir-Adleman

- VPN Virtual Private Network

#

# Introduction

#### Contents

| 1.1 | Side-channel Attack Concept  | 3 |

|-----|------------------------------|---|

| 1.2 | Side-channel Attack History  | 3 |

| 1.3 | Goals                        | 4 |

| 1.4 | Organization of the Document | 4 |

Nowadays, information is becoming more and more valuable in the world we live in. For that reason, cryptography plays the role of keeping information secure, by providing confidentiality, availability, and its authentication. It protects data against security threats that may cause severe impacts on users and industries. Like many other security publications, this research advertises for the different types of side-channel attacks and respective impact on the crypto-systems. In this thesis we proposed the implementation of an enhanced Side-channel Attack (SCA). We assess the success of our attack, considering different success criteria and capturing the respective criteria score for a given amount of attack's resources used. Additionally, we assess the attack's limitations, considering different success criteria.

#### 1.1 Side-channel Attack Concept

Computational systems can unintentionally leak information that in a first instance can be considered as innocent information. However, someone with malicious intentions can analyse it, along with other information, to compromise the system's security-critical data. Therefore, side-channel attacks correlate the variations of the leaked (side-channel) information against the respective input/output from a system's cryptographic computation. The main purpose of this attack is to discover a secret such as a cryptographic secret key used by a victim application, compromising this way, the system's security-critical data. A general side-channel attack is divided into two phases: an online phase, where the side-channel information is extracted, and an offline phase where it is correlated and processed. The leaked information consumed by these attacks can take different forms: the type of sound emitted, the amount of power consumption or the duration of the computation imposed by the different memory level's latencies. A side-channel attack is considered a low-level cryptographic attack.

#### 1.2 Side-channel Attack History

The first appearance of a side-channel vulnerability takes places at the middle of sec. XX. In 1943, the Bell Telephone model 131-B2, a top secret encrypted teletype terminal used by the American Army and Navy, was found to be leaking signals, [2]. This device was placed on a lab along with a freestanding oscilloscope that had developed an habit of spiking every time the teletype encrypted a letter. Every encrypted letter would then emit a specific electromagnetic radiation that would be captured by the oscilloscope, explaining the caused spikes. In the following years there are some occurrences of this type of attack mainly using electromagnetic and acoustic information. Studies on the side-channel attacks take place in the late of sec XX. Firstly, mainly on attacks using power consumption information, such as [3] and recently timing information exploiting the Data Encryption Standard (DES) computation im-

plementation such as [4], which exploits cache hit ratio in large S-box ciphers. Yet in DES, [5] describes theoretical attacks using cache misses with very high temporal resolution and [6]: describes attacks using timing effects due to collisions in the memory lookups inside the cipher. Other attacks on Rivest-Shamir-Adleman (RSA) and Advanced Encryption Standard (AES) implementations, such as [7], [8], have also been proposed.

#### 1.3 Goals

We can list two different types of goals. The first set of goals aim at understanding the environmental conditions required by a specific cache side-channel attack. Conditions such as the Central Processing Unit (CPU) micro-architecture and cryptographic implementation used. The second set of goals go through discovering the type and the amount of attack resources required for the attack's success. The attack's success always depends on a given criteria.

#### 1.4 Organization of the Document

This thesis is organized as follows: Chapter 1 contextualizes the side-channel attacks and its history, we also define a list of project goals to achieve. In Chapter 2 presents the background related to memory cache and cryptography fundamentals, particularly the AES cryptographic algorithm and most popular implementations. In Chapter 3 explores the most known SCA using timing to attack AES. Chapter 4 describe an enhanced implementation of a Prime + Probe based attack, as well as, the requirements, the problem environment and respective countermeasures. Chapter 5 analyse the attack's performance behaviour under different attack's conditions. Chapter 6 highlights important conclusive aspects acquired in this work and make reference to future related research opportunities.

# 2

## Background

#### Contents

| 2.1 | Caches                        | 7  |

|-----|-------------------------------|----|

| 2.2 | Simultaneous Multithreading   | 9  |

| 2.3 | CPU Dynamic Frequency Scaling | 9  |

| 2.4 | Cryptographic Operations      | 10 |

#### 2.1 Caches

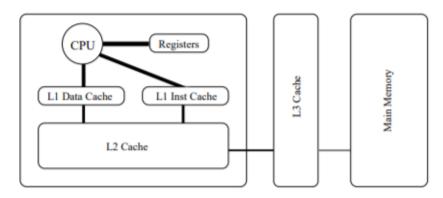

Figure 2.1: CPU and volatile memory levels from [1]

The different forms of memory used by most machines can be organized according to its access time: registers, cache memory, main memory (RAM) and secondary memory (disks), from the fastest to the slowest, Figure 2.1. All the mentioned forms are considered volatile memory except the last one, which is persistent, [9].

The cache serves as a small piece of high-speed memory, managed by machine's hardware. The cache keeps the CPU as busy as possible by minimizing the bottleneck of load/store latency to a lower memory level. Meanwhile, during the execution of a program if it is required to access a certain memory address, the cache is checked for such data and one out of two scenarios may happen, considering the cache as a whole: the target data is present in the cache and then the data is almost instantly read from there, this is called a "cache hit"; or the target data is not cached and needs to be accessed from a lower memory level, this is called a "cache miss". During a cache miss, the data fetched will be placed in the cache, which may involve evicting prior data due to lack of storage space in the cache. Thus, a cache miss costs more time and more electric energy than a cache hit, and these phenomenon are the major key for the accomplishment of cache side-channel attacks.

#### 2.1.1 Structure

Modern caches are divided into three levels L1, L2, L3, where the last one usually is shared among all cores of CPU. Additionally, L1 can be divided into 2 different cache structures L1-D for non-code data storage and L1-I for instruction storage. The CPU looks for the data by the same order: if there is a cache miss in a given cache level, the next cache level is consulted, until reaching the main memory. L3 is the largest cache level in terms of memory space followed by L2 and then L1. Since for consulting L3, we need to have a prior cache miss on L1 and L2, L3 is the most slower cache memory level. Followed by L2, which only requires a cache miss from L1. And finally, L1 which is the first cache level to be

consulted from all. In a single sentence, L1, L2, L3 have more space and its access is slower by the same order. So, the same phenomenon of cache hits and misses exists inside the cache hierarchy itself, where it is possible to exploit the access time to understand the required data location at the moment it was requested.

A given cache level is composed by a number of lines, given by *L*. Every line has a specific number of cache lines, given by *W*, where each cache line can store a fixed-size amount of data, called cache block of size *B* bytes. Altogether, the size of that cache level is given by  $L \cdot B \cdot W$  bytes. However, different cache organizations can be obtained by modifying *L*, *B* or *W*.

#### 2.1.2 Associativity

If a cache contains a single cache set, which means, every line has a unique cache line, the cache is called a direct mapped cache. Conversely, if a cache has a single line containing all the cache lines, where any cache block can be placed at any cache line from the cache, it is called a fully associative cache. Mixture of both architectures is also possible, in fact it is the most popular cache organization. These caches are called *n*-way set associative and have a specific number of cache sets, where each one contains *n* cache lines, [9].

#### 2.1.3 Replacement Policies

When fetching a memory block into the cache, after the cache set has been determined, there's the possibility of having no cache lines available. Replacement policies [9] that specify how to handle this situation. The most popular replacement policies are the following:

- Least Recently Used: Replaces the least recently used block in the cache set by the new block to be cached.

- Random: Chooses a random block in the cache set and replaces it by the new block to be cached.

#### 2.1.4 Writing Policies

Writing policies [9] define which memory hierarchy components a given block is written in and respective circumstances. These are the most known policies:

- Write-back: When a write occurs, the value is written only to the block in the cache. The modified block is written to a lower memory hierarchy level only if it is replaced by another one.

- Write-through: Data is written at the same time in main memory and cache. It keeps the data at any time consistent but the drawback manifests in the low performance it takes. One way to

improve the performance aspect is by implementing a write buffer. A writing makes the new value to be placed either on the cache and the write buffer. When a write to main memory completes, an entry in the write buffer is freed. If the write buffer is full when the processor reaches a write, the processor waits until that data is written in the main memory creating an empty position on the buffer.

#### 2.1.5 Cache Inclusion Policies

Different cache levels can be designed in different ways depending on whether the content of one cache level is present in other levels, [10]:

Inclusive cache: If all cache blocks in the higher level cache are also cached by a lower level cache, then the lower level cache is "inclusive" of the higher level cache.

Exclusive cache: If the lower level cache only caches the cache blocks that strictly are not present in the higher level cache, then the lower level cache is said to be "exclusive" of the higher level cache.

Non-inclusive Non-exclusive cache: If the contents of the lower level cache are neither inclusive nor exclusive of the higher level cache, then it is called "non-inclusive non-exclusive" cache

#### 2.2 Simultaneous Multithreading

Simultaneous multithreading is a technology implemented by most modern CPU that allows two hardware threads to run in the same CPU core at the same time, [11]. Consequently these two threads share the same group of memory hierarchy levels, which includes L1, L2 and L3. Intel CPU's often references this technology by "Hyperthreading" technology<sup>1</sup>.

#### 2.3 CPU Dynamic Frequency Scaling

It's a technique employed in modern architectures that allow the CPU's frequency to adapt "on the fly" to the actual computation need, [12]. It conserves power and reduces the amount of heat produced, since in moments it's not required a significant amount of computational effort, the CPU's underclocks and consequently saves energy. Our attack is very CPU intensive for a considerable amount of time, causing our CPU to overclock. This issue has to be addressed, since it impacts the data extracted by the attack, which happens to be in clock cycles. In other words, over time, we are getting higher clock cycles, which interferes with our measurements, and for that reason we need to employ a structural feature on the attack's code in order to silent this issue.

<sup>&</sup>lt;sup>1</sup> https://www.intel.com/content/www/us/en/gaming/resources/hyper-threading.html

#### 2.4 Cryptographic Operations

The concept of cipher relies on the use of mathematical transformations, in order to change data into a form that is not readily intelligible. The transformation and subsequent recovery of the data depends on the algorithm itself and on any number of keys.

**Encryption and Decryption** The process of transforming a comprehensible text (plaintext) into something fuzzy and hard to precept (ciphertext) is named encryption. The reverse process, which transforms the ciphertext into plaintext, is called decryption. In a general way, in both processes, it may or may not be involved the use of one or more keys, which dictate the exact transformations and substitutions the encryption/decryption algorithm must do.

**Block and Stream Ciphers** In cryptography, it is possible to distinguish different types of ciphers. A block cipher processes the plaintext input in fixed-sized blocks and produces a block of ciphertext of equal size for each plaintext block, example of ciphers such as AES [13], DES [14], RSA [2]. On the other hand, a stream cipher is always a symmetric cipher and it processes the input elements continuously, producing output one element at a time as it goes along. RC4 [15] is a notable example of this type of ciphers.

**Symmetric and Asymmetric Ciphers** Symmetric ciphers correspond to the set of algorithms capable of performing encryption and decryption by using the same key such as AES. Asymmetric ciphers use pairs of keys: public key, which is known for everybody, and a private key, which is known only to its owner. In such a system, somebody can encrypt a message using the receiver's public key, but that encrypted message can only be decrypted with the receiver's private key e.g. RSA.

#### 2.4.1 AES

The Advanced Encryption Standard, also known as Rijndael algorithm [13], is a block cipher algorithm using symmetric keys which was adopted by the National Institute of Standards and Technology, in 2001. This algorithm operates at a 128-bit block at a time, accepting a 128, 192 or 256-bit key and performing 10, 12, 14 rounds respectively.

The idea behind the AES algorithm is to pick 16-byte blocks of the input each time, also known as state. This state will receive a set of key dependent transformations and substitutions generating a final state, which represents the desired output.

#### 2.4.1.A Key Expansion

First of all, the AES algorithm requires its secret key to be expanded in order to generate enough round keys to be used in every round of the algorithm<sup>2</sup>. This process is called key expansion, or key scheduling. The larger a key is, the larger will be the expanded key, which means the more round keys will exist and thus the more rounds will be performed.

The following table presents the size of the expanded key, generated from the key expansion process given a different sized secret key.

| Secret Key Size (byte) | Expanded Key Size (byte) | Round Key Size (byte) | Nº of Rounds |

|------------------------|--------------------------|-----------------------|--------------|

| 16 (128-bit)           | 160                      | 16                    | 10           |

| 24 (192-bit)           | 192                      | 16                    | 12           |

| 32 (256-bit)           | 224                      | 16                    | 14           |

Table 2.1: The secret keys and respective expanded key size

Expanded key's properties relevant for the attack:

- The value of a 128-bit, 192-bit, 256-bit secret key corresponds respectively to the same first 128 bits, 192 bits and 256 bits of the respective generated expanded key. For instance: the part of the expanded key used to perform the very first AddRoundKey transformation corresponds exactly to the 128-bit key.

- The AES specification is structured in a way that allows discovering the whole secret key just simply by knowing any 128, 192, 256 consecutive bits from the expanded key<sup>3</sup>.

#### 2.4.1.B State Transformations

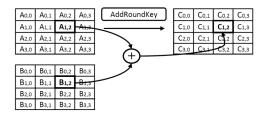

The set of transformations available are SubBytes, ShiftRow, MixColumn and AddRoundKey:

- SubBytes Substitute one byte by a different predefined one using a nonlinear function. So, in the end of the SubBytes operation, each position of the 4x4 state matrix has a new value.

- ShiftRow Shifts the 2nd, 3rd, 4th row of the state matrix by 1, 2, 3 positions to the left, respectively.

- MixColumn Each column of the state matrix becomes its multiplication in a  $GF(2^8)^4$  with the following matrix:

$$\begin{bmatrix} 2 & 3 & 1 & 1 \\ 1 & 2 & 3 & 1 \\ 1 & 1 & 2 & 3 \\ 3 & 1 & 1 & 2 \end{bmatrix}$$

(2.1)

<sup>&</sup>lt;sup>2</sup>More specifically in every AddRoundKey transformation, see Section 2.4.1.B

<sup>&</sup>lt;sup>3</sup>This happens to be particularly useful for the last round attacks.

<sup>&</sup>lt;sup>4</sup>Details of Galouis Field Multiplications in [16]

· AddRoundKey - Apply an exclusive OR operation between the state and the respective round key.

Figure 2.2: AddRoundKey

|         | A0,0 | A0,1 | A0,2 | A0,3 | ShiftRows | A0,0 | A0,1 | A0,2 | A0,3 |

|---------|------|------|------|------|-----------|------|------|------|------|

| Shift 1 | A1,0 | A1,1 | A1,2 | A1,3 |           | A1,1 | A1,2 | А1,3 | A1,0 |

| Shift 2 | A2,0 | A2,1 | A2,2 | A2,3 |           | A2,2 | A2,3 | A2,0 | A2,1 |

| Shift 3 | Аз,о | A3,1 | Аз,2 | Аз,з |           | Аз,з | Аз,о | A3,1 | A3,2 |

Figure 2.4: ShiftRows

Figure 2.3: MixColumns A0.0 A0.1 B0,1 B0,2 A0.2 Ao,: B0,3 SubBytes A1.0 A1,1 A1,2 B1.0 B1.2 B1.3 Br A2,0 A2,1 A2,2 A2,3 B2 B2,1 B2,2 B2,3 B3,0 B3,1 B3,2 B3,3 A3,0 A3,1 A3,2 A3,3 S

#### 2.4.1.C Algorithm

The AES encryption algorithm takes a 16-byte block as input, also known as plaintext, and performs a AddRoundKey transformation using the first round key. Then with the generated state, it is performed by the following order the transformation: SubBytes, ShiftRows, MixColumns and AddRoundkey. This set of transformations is applied for N - 1 times, where N represents the number of rounds defined by the size of the used secret key. So the state generated at the end of each round serves as input state for the next one. The N-th or last round executes by the same order the transformations: SubBytes, ShiftRows and AddRoundkey. At this point, the 16-byte state is returned and represents the output of this computation. For AES encryptions, it's inputted a plaintext to output a ciphertext, for decryptions the inverse operations are performed.

#### Algorithm 2.1: AES encryption pseudocode

```

\begin{array}{c|c} \textbf{begin} \\ state \longleftarrow plaintext \\ AddRoundKey(state, roundKey[0]) \\ \textbf{for } \underline{r=1,r<(Nrounds-1);r++} \ \textbf{do} \\ \\ & SubBytes(state) \\ ShiftRows(state) \\ MixColumns(state) \\ AddRoundKey(state, roundKey[r]) \\ \\ SubBytes(state) \\ ShiftRows(state) \\ AddRoundKey(state, roundKey[Nrounds]) \\ \end{array}

```

#### 2.4.2 AES Implementations

Cipher implementations invoke logical and arithmetic operations to replace the algebraic operations defined in the cipher itself. This means AES softwares can adopt different table implementations, according to their needs. The need of using these technologies come from the necessity of increasing the performance of the whole algorithm process. For that matter, it simplifies the algorithm, by replacing hard computations like in SubBytes operation or MixColumn for lookups to a precomputed-value table. That's exactly here where the success of the side-channel attacks come from. Remember these attacks do not attack the algorithm itself, but rather its implementation.

Table implementations may differ from each other in terms of security and performance standards. We present the most known table implementations, which are S-box [7], [3] and T-box [8] using a 128-bit secret key:

**S-box** S-Box implementation aims to make SubBytes transformation faster, improving the overall AES computation performance. Keep in mind according to the AES specification this transformation resorts to the execution of non-linear function calls, which represents a heavy computation. Then, SubBytes is accomplished using a lookup to a precomputed value table known as S-box (256-bytes). The table receives a 1-byte input and outputs a 1-byte value. Thus, the SubBytes step consists in performing 16 table lookups to S-box for each round. S-box helps the AES computations to gain some performance advantage but not as much as T-box technology.

**T-box** As previously mentioned, ShiftRow and SubBytes operations can switch order inside the respective round without interfering on the end result. Taking this into consideration, it's possible to join both SubBytes and MixColumn transformations and replace them by lookups to a set of computed value tables.

The encryption process using T-box, will be structured in the following way: for each round a ShiftRow will be applied to the received state matrix and T-box lookups will be performed in order to accomplish SubBytes and then MixColumn transformations. Finally, it is applied a XOR operation to the resulting matrix against the round key - AddRoundKey. The tables used will be  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ . In particular, for the last round, since there is no MixColumn phase, T-box implementation has a table  $T_4$  similar to S-box table, to be used only by SubBytes transformation. Every mentioned table will contain 256 4-byte elements (1 KB in total). This means it receives a 1-byte input and outputs a 4-byte value. Typically, all the T-box tables are stored contiguously in memory, occupying a total size of 8 KB.

$T_0, T_1, T_2, T_3$  configuration is described in the following way:

$$T_{0}[a] = \begin{bmatrix} 2 \bullet s[a] \\ s[a] \\ s[a] \\ 3 \bullet s[a] \end{bmatrix} T_{1}[a] = \begin{bmatrix} 3 \bullet s[a] \\ 2 \bullet s[a] \\ s[a] \\ s[a] \end{bmatrix} T_{2}[a] = \begin{bmatrix} s[a] \\ 3 \bullet s[a] \\ 2 \bullet s[a] \\ s[a] \end{bmatrix} T_{3}[a] = \begin{bmatrix} s[a] \\ s[a] \\ 3 \bullet s[a] \\ 2 \bullet s[a] \\ 2 \bullet s[a] \end{bmatrix}$$

(2.2)

For an AES using 128-bit secret and consequently having 10 rounds, this is how the first 9 rounds using T-box are computed, by updating the intermediate state as it follows, for r = 0, ..., 8:

$$\begin{aligned} x_{0}^{r+1}, x_{1}^{r+1}, x_{2}^{r+1}, x_{3}^{r+1} \leftarrow T_{0}[x_{0}^{r}] \oplus T_{1}[x_{5}^{r}] \oplus T_{2}[x_{10}^{r}] \oplus T_{3}[x_{15}^{r}] \oplus K_{0}^{r+1} \\ x_{4}^{r+1}, x_{5}^{r+1}, x_{6}^{r+1}, x_{7}^{r+1} \leftarrow T_{0}[x_{4}^{r}] \oplus T_{1}[x_{9}^{r}] \oplus T_{2}[x_{14}^{r}] \oplus T_{3}[x_{3}^{r}] \oplus K_{1}^{r+1} \\ x_{8}^{r+1}, x_{9}^{r+1}, x_{10}^{r+1}, x_{11}^{r+1} \leftarrow T_{0}[x_{8}^{r}] \oplus T_{1}[x_{13}^{r}] \oplus T_{2}[x_{2}^{r}] \oplus T_{3}[x_{7}^{r}] \oplus K_{2}^{r+1} \\ x_{12}^{r+1}, x_{13}^{r+1}, x_{14}^{r+1}, x_{15}^{r+1} \leftarrow T_{0}[x_{12}^{r}] \oplus T_{1}[x_{1}^{r}] \oplus T_{2}[x_{6}^{r}] \oplus T_{3}[x_{11}^{r}] \oplus K_{3}^{r+1} \end{aligned}$$

$$(2.3)$$

The element outputted by  $T_i[x]$  is a 4-byte value which is then XORed with each other and the corresponding part of the respective round key. Each  $K_i^{r+1}$  is also 4 bytes from the expanded key. Thus, from each row a 4-byte value is outputted, where each state byte corresponds to the respective byte from this 4-byte value. The next round receives as input the state bytes generated in the previous round.

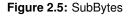

Each table lookup  $T_i[x]$  outputs the x - th element of the table  $T_i$  by loading to the cache block containing that particular element. To that cache block containing consecutive table elements we give the name of "table block". The number of table elements that fit inside a cache block is given by the name of *delta*.

For instance, for 64 byte cache line, this T-box implementation would have a delta = 16, which means the respective cache blocks would contain 16 4-byte table elements.

| T1[0] | т1[1] | т1[2] | т1[3] | т1[4] | T1[5] | т1[6] | т1[7] | т1[8] | т1[9] | T1[10] | т1[11] | T1[12] | T1[13] | T1[14] | T1[15] |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|

Figure 2.6: Cache block containing all the first 16 elements of the T-box table  $T_1$

The last round is computed by the following way, where :

$$c_{0}, c_{1}, c_{2}, c_{3} \leftarrow T_{4}[x_{0}^{9}] \oplus k_{0}^{10}, T_{4}[x_{5}^{9}] \oplus k_{1}^{10}, T_{4}[x_{10}^{9}] \oplus k_{2}^{10}, T_{4}[x_{15}^{9}] \oplus k_{3}^{10}$$

$$c_{4}, c_{5}, c_{6}, c_{7} \leftarrow T_{4}[x_{4}^{9}] \oplus k_{4}^{10}, T_{4}[x_{9}^{9}] \oplus k_{5}^{10}, T_{4}[x_{14}^{9}] \oplus k_{6}^{10}, T_{4}[x_{3}^{9}] \oplus k_{7}^{10}$$

$$c_{8}, c_{9}, c_{10}, c_{11} \leftarrow T_{4}[x_{8}^{9}] \oplus k_{8}^{10}, T_{4}[x_{13}^{9}] \oplus k_{9}^{10}, T_{4}[x_{2}^{9}] \oplus k_{10}^{10}, T_{4}[x_{7}^{9}] \oplus k_{11}^{10}$$

$$c_{12}, c_{13}, c_{14}, c_{15} \leftarrow T_{4}[x_{12}^{9}] \oplus k_{12}^{10}, T_{4}[x_{1}^{9}] \oplus k_{13}^{10}, T_{4}[x_{6}^{9}] \oplus k_{14}^{10}, T_{4}[x_{11}^{9}] \oplus k_{15}^{10}$$

$$(2.4)$$

$c_i$  represents the ciphertext byte,  $k_i$  represents the respective last round key byte.

# 3

## State of the Art

#### Contents

| 3.1 | Side-Channel Attack 1                               | 7 |

|-----|-----------------------------------------------------|---|

| 3.2 | Types of Side-channel attacks                       | 7 |

| 3.3 | Timing Cache Side-Channel Attack on AES - Structure | 8 |

| 3.4 | Types of Timing Cache Side-channel Attacks on AES   | 9 |

| 3.5 | Countermeasures                                     | 4 |

| 3.6 | Summary                                             | 6 |

This section introduces the concept of side-channel information attack. In a first stage, it describes the idea behind most known types of side-channel attacks based on the type of side-channel information consumed. Then, it focuses on the cache timing attacks used to exploit AES implementation. Detailing the structure and the idea underneath most popular attacks in the field. A list of counter measures for these attacks is also presented.

#### 3.1 Side-Channel Attack

A side-channel attack like any other computer attack, consists in discovering a secret in the system for the advantage of an attacker. The most common example of a secret is the key used by a victim in order to perform a cryptographic computation over some information for local storage or network dispatch purposes, [8]. A side-channel attack strategy relies on extracting information of the system that is not meant to be leaked, which is called by side-channel information. This information is then cryptoanalysed achieving partially or entirely our goal. Given the procedure of a typical side-channel attack, we may easily divide it in two different phases: An online phase, where the attacker needs the victim to be performing some cryptographic computation for extracting the side-channel information; and an offline phase, which no longer requires the presence of the victim, and where the side-channel information is processed.

#### 3.2 Types of Side-channel attacks

A side-channel information attack is primarily defined by the type of side-channel information extracted and processed. Either side-channel information attacks that use timing [8], [17] or power consumption [3] or even acoustic information [18] work relatively the same way. The variance of the side-channel information gives them clues about the cache state at a given moment. Thus, the attacker gets an idea which table blocks were used for a particular cryptographic process. Depending on the attack, this information along with other public information such as the algorithmic cryptographic equations, microarchitectural details or plaintexts/ ciphertexts values, allows the attacker to reveal the victim's secret key, [19]. For this reason, we can acknowledge the existence of different attack families based on the type of side-channel information used. Inside each attack family we might discriminate each attack based on other characteristics such as the online technique used, the target cryptographic implementation and others.

#### 3.3 Timing Cache Side-Channel Attack on AES - Structure

This section focuses on the structure of cache side-channel attacks that use timing information and target AES cryptographic implementations.

#### 3.3.1 Online Phase

The online phase manages all the extraction of the side-channel information gathered by the attack. The attacker needs the presence of the victim in order to extract side-channel information. The type of actions the attacker is able to perform correspond only to legal moves by the attacker. From a high perspective, the set of actions at the attacker's disposal include:

- 1) Calling any AES computation for caching certain T-box / S-box table blocks

- · 2) Loading any attacker's data with the purpose to evict certain T-box / S-box table blocks

- 3) Timing any previous actions 1) and/or 2)

In a general way, these actions allow the attacker to get an idea of the contents that are inside the cache at a given moment, as well as, to set the cache state to custom state.

For instance, if we consider loading some consecutive attacker's data cache blocks and timing every load performed. We might verify that in fact some specific loads took longer than others. The attacker understands which attacker's cache blocks were cached and those whose were not in the moment the set of loads was performed. Consequently, the attacker can infer about which T-box/S-box blocks were cached by the victim. The side-channel information corresponds to the time duration measured in by the loads performed by the attacker.

These types of actions have to be performed many times using distinct victim cryptographic executions in order to create a considerable amount of side-channel information that allows the attacker to break the secret. The more side-channel information the attacker has, the better for reducing the expression of the inherent external<sup>1</sup> and internal noise<sup>2</sup>.

An online technique corresponds to the set of actions the attacker uses for materializing its own attack's online phase.

#### 3.3.2 Offline Phase

The offline phase manages all the crypto-analysis and processing of the side-channel information gathered during the online phase. The side-channel information is correlated with some micro-architectural

<sup>&</sup>lt;sup>1</sup>The noise from external programs

<sup>&</sup>lt;sup>2</sup>The noise from the same program

details and AES specification equations, which are publicly known, giving to the attacker information about the value of the secret key. Also, it's possible to encounter some cases of offline phases simulating victim's encryptions / decryptions, extracting respectively the plaintext or the ciphertext for key hypothesis testing.

This phase is strictly dependent on how the side-channel information was fabricated and what it represents in the context of the attack. The identity of an offline phase is usually defined by which are the equations exploited by it.

All the most popular offline techniques in this type of side-channel attacks will be addressed ahead.

# 3.4 Types of Timing Cache Side-channel Attacks on AES

In this section we present the most popular timing attacks that target T-box based AES implementations. We present each attack by describing its online phase, followed by the offline phase, respective assumptions and results. At the end of each type of attack we approach other variants of the related attacks.

#### 3.4.1 Evict + Time Attack

This attack was proposed in [8]. Its general idea relies on the time variation between two similar encryptions that inherit different cache states.

**Online phase** Its online technique can be divided in three stages:

- First Encryption Phase: Attacker triggers a single victim encryption using a certain known random plaintext and secret (unknown) key, caching all the blocks that contain the table elements accessed during this encryption.

- Line Eviction Phase: At this point, the attacker chooses a particular table block that he wants to test whether it was used or not during the first encryption. For this, it is known that if that particular table block is cached, it can only reside in one certain line. So, the attacker chooses the respective line and evicts its content. To perform the cache set eviction, the attacker needs to load new blocks (non-table blocks) from memory addresses that are mapped by the target line in order to expel the prior content on it. In a more practical view, this translates into fetching *W* blocks (N \* S) bytes apart<sup>3</sup> to the target table block in memory, where  $N \in 1, 2, 3...$

- Second Encryption and Timing Phase: Now the attacker will trigger a second victim encryption in the exact same way as the first one, this is, using the same known plaintext, and by default

$<sup>{}^{3}</sup>W$  - the number of the cache level associativity; S - cache set size

the same secret key. Attackers will also time this encryption in order to extract timing information useful for the recovery of the secret key. At the end of this process, the following triplet information is extracted: < plaintext p; line evicted l; 2nd enc. duration d >.

It is up to the attacker to repeat the same process again and again, gathering triplets having the same or not attack input.

**Offline phase** On the offline phase, the attacker will start by plotting triplets with the same plaintext, noticing that different lines have different 2nd encryption duration.

- For the lines with higher 2nd encryption duration: It means the table blocks mapped by the same respective lines were required during the 2nd encryption, always causing a cache miss, since they were evicted from the cache in the line eviction phase, delaying the overall encryption time.

- For the rest of the lines: It means the table blocks mapped by the same respective lines were not required during the 2nd encryption, causing no cache miss, and thus not penalizing the overall encryption time.

AES specification equations that generate the 1st and 2nd round state bytes are relatively simple equations that tell the relation between plaintext information with key information and table elements (from a certain table block), Equation (4.6) and Equation (4.8). On the other side, the attacker is aware of the plaintext and the used table blocks (and consequently the unused ones). This allows to the attacker to exclude the key values that when placed on the equations they access table blocks detected as blocks from lines with a low 2nd encryption duration. The remaining key bytes not excluded represents the key discovered by this process. Note that a particular table block is used during an encryption, when at least one table element from that same block was used during the encryption.

**Assumptions** It assumes the attacker's knowledge of the associativity number, cache line size, number of lines and the lines that map the different table blocks of the target cache level. Besides, the attacker has the ability to trigger victim encryptions.

**Results** For the [8] attack, the chosen architecture was a 2GHz Athlon 64 CPU targeting the Last Level Cache (LLC). The attacker was able to trigger victim's encryptions that received a text inputted by the attacker and the victim's secret key to be discovered by the attacker. The victim application would rely on these encryptions by performing OpenSSL function calls, in particular 128-bit AES encryptions on Electronic CodeBook (ECB) mode to the OpenSSL 0.9.8 cryptographic library<sup>4</sup>. In order to discover

<sup>&</sup>lt;sup>4</sup>This OpenSSL version keeps its tables static in the memory, which allow to be loaded by the same lines over different cryptographic calls

the full 128-bit victim secret key, the attacker would require to trigger at least 500,000 different plaintext encryptions, which translates in 30 seconds for the online phase, assuming the full knowledge of the table addresses.

#### 3.4.2 Prime + Probe Attack

This attack was proposed in [8]. Its general idea relies on the timing variation that the attacker takes to access its data after a cryptographic computation by the victim.

**Online phase** A typical Prime + Probe online phase can be divided in three stages:

- Prime phase: The attacker begins by loading a contiguous byte array with the target's cache size named by *A* array.

- Encryption Phase: The attacker triggers a victim encryption with a known random plaintext and a secret (unknown) key, eventually, evicting some array blocks on the cache.

- Probe Phase: For each line of the target cache level, the attacker fills<sup>5</sup> it with the respective A cache blocks and measures the computation time. At the end, the attacker has the triplet information:cplaintext p, line l, measured time t >.

It's up to the attacker to repeat this measurement process using different plaintexts in order to gather different triplets. The higher the amount of these triplets the better the quality the side-channel information has.

**Offline Phase** On the offline phase, the attacker will start by plotting triplets with the same plaintext, noticing lines l do have different measured times t associated:

- For the lines with higher *t*: it means the table blocks mapped by the same respective lines were evicted when the *A* cache blocks mapped by the same line were loaded during the Probe phase. These cache misses are responsible for delaying the duration of the probe phase timing computation.

- For the rest of the lines: it means the table blocks mapped by the same respective lines were not loaded by the victim, which made no *A* cache blocks to be evicted. During the probe phase, the accesses to the *A* cache blocks only caused cache hits, which made the respective measured *t* time to be small.

<sup>&</sup>lt;sup>5</sup>Access data that is mapped by the same line of the cache, likewise in Evict + Time attack

The Prime + Probe attack also makes usage of AES specification equations Equation (4.6) and Equation (4.8), that generate the 1st and 2nd round state bytes. Again, they tell the relation between plaintext information with key information and table elements. For each encryption, the attacker is aware of the plaintext values and respective side-channel information that tells which table blocks were required (and those not required) by the victim during the process. Likewise in Evict + Time attack, the attacker performs a key hypothesis testing. It is placed a hypothetical key value into the equations and it is checked whether or not they access table blocks previously detected as blocks not used. Every hypothetical key value is excluded if they match the previous statement. The remaining key bytes not excluded represent the key discovered by this process. Note that, this measurement technique is more efficient than Evict + Time, since in a single measurement, the attacker gets to know which lines are used by cryptographic tables for an encryption with a given input.

**Assumptions** It assumes the attacker's knowledge of the associativity number, cache line size, number of lines of the target cache level and the lines that map the different table blocks of the target cache level. Besides, the attacker has the ability to trigger victim encryptions.

**Results** The chosen architecture was a 2GHz Athlon 64 CPU targeting the last level cache (LLC). The attacker was able to trigger victim encryptions that received a text inputted by the attacker and the victim's secret key to be discovered by the attacker. The victim application would rely on these encryptions by performing OpenSSL function calls, in particular 128-bit AES encryptions on ECB mode to the OpenSSL 0.9.8 cryptographic library. In order to discover the full 128-bit victim secret key, the attacker would require to trigger at least 300 different plaintext encryptions, which translates in 65 milliseconds seconds of online phase plus 3 seconds of offline phase.

**Other related attacks** Related to the Prime + Probe attack, there is an attack under the name of "asynchronous" attack which is presented on [8]. In the attack setup, we consider a victim application that performs encryptions only when the user is authenticated. This way, the attacker is not able to trigger any victim encryption and consequently not knowing the plaintext used in each one.

The attack requires a CPU Simultaneous MultiThreading (SMT) setup enabled, which allows a concurrent execution of both attacker and victim processes on the same physical processor. Additionally, the attacker needs to be sure about the non-uniformity<sup>6</sup> of the plaintexts and its type, e.g.: english text, numerical data, machine code.

The attacker then starts by timing the process of filling a given line of the respective cache level. Hopefully, at the same time, the victim starts to perform encryptions, which means it will cache the required table blocks.

<sup>&</sup>lt;sup>6</sup>Some plaintexts byte values are more often used than others

These table blocks are going to replace the attacker's data blocks, which interferes with the attacker's time measurements. Consequently, the attacker understands which are the lines (or the table blocks) that take more time.

Since some plaintext byte values are used more frequently than others, it means some table blocks required for the 1st round will be cached more than others. Then, our attacker is able to connect these table blocks with the most used plaintext byte values. This type of attack does not let the attacker to discover more than half of the secret key. But it represents a strong type of attack.

## 3.4.3 Flush + Flush Attack

This attack was retrieved from [17]. Flush + Flush measurement relies on the temporization of the instruction called clflush. This instruction can be used at all privilege levels. It receives an address and then removes from every level of the cache hierarchy the cache block referenced by that address.

Online Phase A typical Flush + Flush measurement can be divided in 3 stages:

- First Flush Phase: The attacker performs a clflush using any given table address that references a table block (containing certain table elements).

- Encryption Phase: Attacker triggers a victim encryption using a known random plaintext over a secret (unknown) key.

- Second Flush Phase: The attacker times a clflush instruction using the previous table address. In the end, the attacker has the triplet information:< plaintext *p*, table block *t*, measured time *t* >.

**Offline Phase** It's up to the attacker to repeat this measurement process using different plaintexts in order to gather different triplets. Likewise in the previous attacks, the higher the amount of these triplets means more side-channel information available to be consumed. This helps reducing the complexity of the crypto-analysis and the impact of internal and external noise during the attack process.

For each gathered triplet, one out of two options can occur:

- If the execution time of the clflush instruction is measured to be too long, this implies that the encryption accessed the probing cache line or the sensitive data.

- If the execution time of the clflush instruction is short, it means the victim did not access the probing cache line.

The discovery of part of the victim's secret key only resorts on the usage of the AES equations that generate the state bytes of the 1st round, Equation (4.6). However, the AES equations that generate the

state bytes of the 2nd round, Equation (4.8), theoretically could be used to uncover the remaining key bits.

**Assumptions** It assumes the attacker's knowledge of each table block address to be inputted in the clflush instruction. Plus the ability for the attacker to trigger victim encryptions.

**Results** The chosen architecture was a Haswell i7-4790 CPU targeting the last level cache (LLC). The attacker was able to trigger victim encryptions that received a text inputted by the attacker and the victim's secret key to be discovered by the attacker. Our victim application would rely on these encryptions by performing OpenSSL function calls, in particular 128-bit AES encryptions on ECB mode to a T-box based OpenSSL version. In order to discover the 64 out of 128-bit victim secret key, the attacker would require to trigger at least 350 different plaintext encryptions, which translates in 163 seconds of online phase. The major advantage of this type of attack resides on the difficulty to be detectable by the victim. The full-key extraction is theoretically possible, however it is not presented by the author.

**Other related attacks** There is a similar attack called Flush + Reload attack from [20], however this one is out of the scope of this section, since it targets RSA implementations. Flush + Reload attack relies on the time variation the process of reloading a given cache block takes (previously evicted from the cache resorting on the clflush instruction). In comparison to the Flush + Flush attack, the unique distinction is that it times the reload instruction over a target table block instead of performing the 2nd flush over it.

# 3.5 Countermeasures

There are many solution approaches in order to mitigate these types of attacks. We divide these solutions in 2 different groups: hardware based solutions and software based solutions.

#### 3.5.1 Hardware Based Solutions

Canteaut et al. [19] and Ruby Lee [21] explore the hardware solution approach, listing a set of secure cache architectures, that aim to mitigate or reduce the success of cache-side channel attacks.

#### **Partitioning Based Architectures**

• Static Partitioning Cache: It separates the cache for the victim and for the attacker. In other words, there's a cache for user mode and another for supervisor mode.

- Partition Locked Cache: A cache where protected cache blocks cannot be replaced by nonprotected blocks, this can be achieved using a protection bit. Thus, the attacker cannot evict table blocks(protected) using his own data (non-protected), which happens to be an important move for most of these attacks.

- Non-monopolizable Cache: Cache is separated by the cache way, contrary to Static Partitioning which divided the cache by the cache set. Specific different ways from the cache are assigned individually to the attacker and victim.

#### **Randomized based Architectures**

- Fully Associative Cache using random as replacement policy: Allowing any block to be placed anywhere in the cache in a not-predictable cache line.

- Random Eviction Cache: Typical cache with an extra behaviour, which consists in evicting a random block from the cache when a certain number of memory accesses is achieved.

- A typical cache but when required to fetch a memory block M, in reality it fetches one memory in the neighbourhood of M, including M.

#### Others

Disabling CPU's caching mechanism or excluding cache from CPU's represents a brutal countermeasure. In this particular situation, the effect on performance would be devastating. Increasing the size of the cache line makes the attack difficult since *delta* also increases, i.e. the number of elements per table block increases. This represents a larger number of possibilities and then more samples and more time would be consumed. In particular for defending against "asynchronous" attacks <sup>7</sup>, disabling interrupts and stopping simultaneous threads would be an option to consider.

#### 3.5.2 Software Based Solutions

Tromer et al. [8] and Bernstein [7] introduce some interesting software-based countermeasures that AES implementers can take in consideration.

- During an encryption/decryption process, replace the table lookups part by a set of logical operations in order to get the same result. Using T-box or S-box imply loading table blocks into the cache, leaking side-channel information. To prevent this, the values T-box or S-box can be computed.

- Use lookup tables and place them on registers, in the case there's enough room for them (e.g.: PowerPc AltiVec), however the performance is degraded.

<sup>&</sup>lt;sup>7</sup>Attack introduced in Section 3.4.2

- Consider using alternative AES table architectures of reduced size: S-box (256-byte table); S-box table and a table composed by  $2\times$ S-box values (two 256-byte tables);  $T_0$  (1024-byte table) and recreate  $T_1, T_2, T_3$  by doing rotations,  $T_0...T_3$  compressed into one table with non-aligned lookups (2048-byte). Using smaller tables reduces the efficiency of some attacks.

- Adding extra noise to an AES computation by doing extra table accesses e.g.: Performing a second encryption in order to interfere with the side-channel information leaked by the main encryption computation.

- Cache state normalization by loading all the lookup tables right before an encryption start, could easily defeat the big majority of timing attacks: Evict+Time and Prime+Probe based attacks.

In counterpart, all of the solutions mentioned above bring downgraded cryptographic performances some more than others.

# 3.6 Summary

From the discussion made so far, we acknowledged the concept of a side-channel attack, which consists in discovering a secret from the system using and processing information leaked by it. There are different side-channel attacks, according to the type of information consumed by them, such as acoustic, power consumption and timing information. Inside timing cache SCA, we presented its typical structure, which is divided in an online phase and an offline phase. In the online phase the attacker is able to perform a set of actions, such as triggering victim encryptions, timing any computation and changing any cache level state. A set of these actions aligned by a strategy, allow the attacker to extract side-channel information to be consumed in the offline phase, fulfilling the attacker's goal. We presented the most popular cache SCA, from the ones that use timing information and target T-box AES implementation. In a very simple way, the side-channel information from each attack has different causes:

Evict + Time from the timing measurements of victim encryption duration;

Prime + Probe from measuring the duration of changing the cache level state, such as a filling a certain line;

Flush + Flush from the duration it takes to issue a clflush instruction.

Additionally, we present a set of countermeasure solutions that can be divided in two groups: software and hardware based. These solutions reduce the impact of timing cache SCA, however all come with downgraded cryptographic performances.

# 4

# **Proposed Solution**

# Contents

| 4.1  | Proposed Attack                |

|------|--------------------------------|

| 4.2  | Problem                        |

| 4.3  | Attack Structure               |

| 4.4  | CPU and OS                     |

| 4.5  | OpenSSL                        |

| 4.6  | Hardware Requirements          |

| 4.7  | Measurement Concept            |

| 4.8  | 1st Phase - L1-D T-box Mapping |

| 4.9  | 2nd Phase - Online Phase 42    |

| 4.10 | ) 3rd Phase - Offline Phase    |

We start this chapter by highlighting the main characteristics of the implemented attack. This helps understanding the place of our attack among the others. Then we clarify which knowledge about the problem, by convention, does the attacker have and the set of actions he is allowed to perform. We break down the attack's structure into three different phases, and the constitution of both attacker and victim applications. Additionally, we tell for each phase which programs from which applications are required. Following this, we describe the system and hardware context where we implemented the attack, such as the CPU, Operative System (OS), AES implementation (OpenSSL) and others. Lastly, we describe succinctly each attack's phase.

# 4.1 **Proposed Attack**

This section represents the fingerprint of the presented attack, containing its main characteristics. The implemented attack corresponds to a cache side-channel attack that targets the AES implementation in particular T-box tables. This attack is fuelled by timing information which means different access data computations are performed and respective time is captured. Then, each computation time tells the attacker whether or not the cache levels below L1-D were accessed or not. For this reason, our attack aims at the L1-D cache level. This attack uses the Prime + Probe technique on its online phase. Like other Prime + Probe related attacks, our offline phase exploits the AES equations that generate the 1st and 2nd round state bytes. Our attack is capable of uncovering the whole AES victim's secret key.

Unlike most related side-channel attacks, this one does not require the previous knowledge of the Tbox mapping on L1-D or even brute force all the possible positions the T-box might have during the online phase. Specifically, our attack includes a phase that is only meant to solve this problem in particular. This can be considered an enhancement that we bring to the existing Prime + Probe attacks. The original part of this attack is because it relies on the usage of the difference between L1-D and L2 access latencies, contrary to most of attacks which is between LLC and the memory.

# 4.2 Problem

This section contextualizes the problem the implemented attack is intended to solve. We mention the existing applications and each other's role in the attack:

First, we acknowledge the existence of a victim application that ciphers a plaintext that can be inputted by a user or a program. This application contains an inner secret key that is passed along the received plaintext to call an AES encryption function. That encryption function belongs to the OpenSSL application, which is a cryptographic library containing a large set of cryptographic functions to be used by external users or programs. Victim application is a custom software and it can be compared to applications such as dmcrypt<sup>1</sup> or a simple Virtual Private Network (VPN) software.

The attacker application materializes the strategy used to uncover the secret key from the victim. In other words, our attacker application can have two distinct interactions: The first one, resides on the ability to trigger victim application executions, inputting any desired plaintext. The second, resides on calling OpenSSL encryption functions, inputting any desired plaintext and any key value, like it happens with the victim application. The gathered side-channel information is then crypto-analysed, revealing the victim's secret key value.

# 4.3 Attack Structure

This section briefly describes each phase of the attack.

- 1) 1st phase L1-D T-Box Mapping phase: the attacker application performs OpenSSL encryptions<sup>2</sup> to discover which L1-D lines map each T-box element.

- 2) 2nd phase Online phase: the attacker application triggers victim executions inputting a given plaintext in order to extract side-channel information.

- 3) 3rd phase Offline phase: attacker application gathers the information from 1) and 2) and exploits the AES equations that generate the state bytes for the 1st and 2nd round in order to uncover the victim application secret key.

# 4.4 CPU and OS

The attack was implemented under a machine using the following CPU and OS:

| CPU                          | Intel(R) Core(™) i7-8565U CPU @ 1.80 GHz |

|------------------------------|------------------------------------------|

| Physical Cores               | 4                                        |

| Logical Cores                | 8                                        |

| Simultaneous MultiThreading  | Yes                                      |

| Turbo Boost Technology       | Yes                                      |

| Base CPU Freq.               | 1.80 GHz                                 |

| Max CPU Freq.                | 4.60 Ghz                                 |

| L1-D Size                    | 32KB                                     |

| L1-D cache line size         | 64B                                      |

| L1-D associativity           | 8                                        |

| L1-D lines                   | 64                                       |

| Write-policy                 | write-back                               |

| Instruction set architecture | x86/64                                   |

#### Table 4.1: Details of the CPU used

<sup>&</sup>lt;sup>1</sup>https://gitlab.com/cryptsetup/cryptsetup/-/wikis/DMCrypt

<sup>&</sup>lt;sup>2</sup>More information in Section 4.5

Table 4.2: Operative System used

OS Ubuntu 18.04.5 LTS

# 4.5 OpenSSL

This section gives a more technical description of the OpenSSL version used in this solution. OpenSSL is the system cryptographic software that contains the AES implementation that can be used by applications and users. For this attack, we are using the OpenSSL 0.9.8, containing 4 encryption T-box tables, each containing 256 4-byte elements (4KB of table information). This T-box technology keeps the tables static in memory, which means different calls to OpenSSL will always load the tables into the same L1-D lines<sup>3</sup>. Additionally, this type of T-box implementation positions its tables consecutively and contiguously in memory. In practical terms, it means  $T_0$ ,  $T_1$ ,  $T_2$  and  $T_3$  tables are placed in memory by the same order. The targeted encryptions are the AES 128-bit encryptions and the encryption mode is the ECB.

The OpenSSL files used either in the attacker and victim applications are:

- aes.h header file containing the called functions declarations can be viewed in Listing A.5.

- libcrypto.so shared object containing the implementations of the functions called. The respective C program is under the name of aes\_core.c presented in Listing A.6.

The OpenSSL functions either used by attacker and victim applications are:

- AES\_set\_encrypt\_key(secret\_key,key\_bits\_size,round\_key): receives a secret key and generates respective expanded key (as known as round key).

- AES\_encrypt(plaintext,ciphertext,round\_key) : triggers and encryption, receiving a 16-byte plaintext block and a round key, and outputting the respective ciphertext.

# 4.6 Hardware Requirements

This section represents the physical demands that have to be assured in order to provide the proper environment for our attack. The list of demands is presented above:

Application processes run in the same CPU core: It's required for both attacker and victim applications to run in the same core<sup>4</sup>, this is possible either using a uni-core system, or force both processes to run on the same core on a multi-core CPU. This requirement guarantees processes share the L1-D cache for the whole execution.

<sup>&</sup>lt;sup>3</sup>This is documented in https://www.openssl.org/docs/ and it is proved by our 1st attack phase

<sup>&</sup>lt;sup>4</sup>During the L1-D T-box mapping and Online phases

• Simultaneous Multithreading active: The CPU core where the applications run require to have the SMT technology enabled. This represents the only way for the attacker (atk.c) to be able to extract relevant side-channel information from atk\_enc.c and vic\_enc.c since they share the same L1-D at the same time. This requirement is guaranteed by the CPU used, since by convention the CPU already has SMT technology enabled.

# 4.7 Measurement Concept

The secret of this attack relies on timing certain computations. Considering the difference latencies between L1-D and other cache levels, each computation duration tells the attacker whether or not the L2 cache or lower was accessed meanwhile. If we try to time two similar computations that access different but the same sized data, and the first computation takes less time than the second. Then we can conclude the second one accessed a lower cache level which justifies the time difference. This section explains the concept of a measurement both on a theoretical and practical perspective. A measurement represents an atomic process that allows the attacker to retrieve some information from the victim. Both L1 T-box map and measurement phases resort on the usage of measurements aligned with each one strategy.

#### 4.7.1 Theoretical Alignment

The measurement concept considers two distinct processes, running at the same time sharing the same CPU core. Consider the characteristics of our CPU which includes the SMT and dynamic frequency scaling technology for the sake of this explanation.

- **Process 1** performs the same AES encryptions of a given plaintext p and key k

- **Process 2** continuously fills each L1-D line by loading the necessary array cache blocks until process 1 finishes.

Process 2 contains an array with the size of the L1-D cache. Thus, a "L1-D line fill" corresponds to loading for W elements<sup>5</sup> from this very array with S bytes<sup>6</sup> apart from the next one. This way we can guarantee the whole line only contains process 2 data.

After the process 2 fills a specific line with its data, process 1 will access some T-box elements evicting or not some cache blocks of that specific line. At this moment, the state of this L1-D line can either contain only process 2 cache blocks or process 1 and 2 cache blocks. Thus, process 2 performs

$<sup>{}^5</sup>W$  corresponds to the number of cache sets of L1-D cache

$<sup>^6</sup>S$  : The cache set size of L1-D cache

once again a line fill and times it. The time resulted from the previous computation tells us if the process 1 loaded T-box cache blocks in that line:

- If the time is low: we conclude there were no cache misses during the process of filling that specific line. Which means no process 2 cache blocks were evicted and for that reason no T-box elements that are mapped in that line were not required by the process 1.

- If the time is high, we conclude there was at least one cache miss during the process of filling that specific line. Which means at least one process 2 cache block was evicted and for that reason at least 1 T-box cache block that is mapped in that line was required by the process 1.

Expanding this procedure for every L1-D line, it's possible to understand which lines are being used by 1 and those who are not. Thus, each measurement produces a timing array, where each index corresponds to the L1-D line and each element to the respective timing value acquired.

#### 4.7.2 Implementation details

A measurement already considers the execution of the process 2 in the system. Process 2 forks<sup>7</sup> itself creating a child and runs the executable of the process 1, passing as argument a given 16-byte plaintext p. At this time we have 2 different hardware threads running in our core, sharing the same cache levels:

**Process 1** Process 1 generates its round key using an OpenSSL function and encrypts the plaintext *p* received by the process 2 using that same expanded key (round key) over REPETITIONS times. The longer REPETITIONS is, the more encryptions will be made, which means process 2 and 1 will execute in parallel longer, producing more high quality side-channel information. Encrypting a given plaintext for REPETITIONS times is theoretically the same as performing an encryption of a plaintext constituted by REPETITIONS sequential 16-byte plaintexts.

| Algor | Algorithm 4.1: Process 1 pseudo-code                     |  |  |  |  |  |

|-------|----------------------------------------------------------|--|--|--|--|--|

| begi  | begin                                                    |  |  |  |  |  |

| r     | $roundKey \longleftarrow set_encrypt_key(key)$           |  |  |  |  |  |

| f     | for $\underline{r=0}; r < REPETITIONS; r++$ do           |  |  |  |  |  |

|       | $\ciphertext \leftarrow encrypt(plaintext,roundKey,128)$ |  |  |  |  |  |

**Process 2** Process 2 starts by timing the computation that consists in filling a given L1-D line over INNER times, for every L1-D line. In the end of this process we keep an array containing each L1-D

<sup>&</sup>lt;sup>7</sup>Fork system call is used for creating a new process, the generated child executes the instruction next to the fork() call process

line computed timing. This whole process can be repeated until the process 1 finishes, producing an averaged L1-D lines duration array.

- The creation of the INNER loop, in Algorithm 4.2 comes from the need of overcoming the lack of timing resolution our timer presents. This is, our timer has not the capacity to distinguish a line fill whether there are cache misses or not. Using all the fill repetitions of INNER loop, we amplify that timing difference, since now we have more L1 cache misses.