# Exploiting non-conventional DVFS on GPUs: application to Deep Learning

### **Francisco Soares Mendes**

Thesis to obtain the Master of Science Degree in

### **Electrical and Computer Engineering**

Supervisor(s): Doutor Nuno Filipe Valentim Roma Doutor Pedro Filipe Zeferino Tomás

### **Examination Committee**

Chairperson: Doutora Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Doutor Nuno Filipe Valentim Roma Member of the Committee: Doutor Luís Miguel Teixeira D'Avila Pinto da Silveira

October 2020

ii

### Declaration

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

### Acknowledgments

I would like to express my sincere gratitude to my mentors and thesis supervisors, Professor Nuno Roma and Professor Pedro Tomás, for all the discussions about computer hardware, for always setting the bar high and for all their helpful insight and guidance through the development of the work presented in this thesis. Furthermore, I would like to thank INESC-ID for providing me the tools to develop the experimental results for this dissertation.

First, I must thank my grandfathers Filipe and António, my uncle João and my father for always inspiring me to get my "hands dirty" and be practical and objective when trying to solve a problem.

I would also like to thank my dear friends André Meneses, André Pereira, Edgar, Gonçalo, Ivan, Pedro and Rodrigo for all the good times that we spent, and for each of them always having an interesting and different topic to talk about.

Finally, I must express my very profound gratitude to my family, who always believed in me, especially: to my sister, Rita, for all the insightful conversations and especially, for all the bits of advice about really everything that I need; to my parents, for all the love, support, care, attention and opportunities that you provide me; and to my girlfriend, Margarida, for tickling me on her unique way to aspire higher.

I've got a sense that all of you build a little bit of a stepping stone on which I can climb to look further ahead.

This work was partially supported by national funds through Fundação para a Ciência e a Tecnologia (FCT) under projects UIDB/CEC/50021/2020 and PTDC/EEI-HAC/30485/2017.

### Resumo

Atualmente, as unidades de processamento gráfico (do inglês GPUs) são um dos principais dispositivos computacionais usados para acelerar aplicações de cariz paralelo. Contudo, esse imenso desempenho acarreta um alto consumo energético. Diversas soluções podem ser adotadas para aumentar a eficiência energética desses dispositivos. Porém, o escalonamento de tensão-frequência (T-F) tem sido a solução que obtém o melhor resultado, permitindo melhorar as métricas de eficiência energética de forma automática e independente do tipo de aplicações a serem executadas.

As implementações atuais de escalonamento dinâmico de tensão e frequência (do inglês DVFS) em GPUs são unidimensionais, ajustando a frequência dentro dos pares padrão de tensão-frequência. No entanto, este ajuste é insuficiente, pois não garante o par T-F mais adequado à aplicação a ser executada. Esta dissertação apresenta uma nova metodologia para caraterizar o impacto do DVFS não convencional em GPUs, capaz de colmatar o carácter unidimensional das implementações actuais. Para atingir este objetivo, a abordagem proposta define um espaço de parametrização que determina a faixa de tensão tolerável para cada frequência. A mesma foi testada em duas GPUs da AMD com os resultados a mostrarem que estes dispositivos, em particular, são ambos capazes de operar em segurança com até menos 20% do valor padrão de tensão. Este espaço de parametrização definido foi então usado pelo mecanismo de otimização T-F desenvolvido para selecionar automaticamente a configuração de maior eficiência energética. Quando aplicado a aplicações de Aprendizagem Profunda e, especificamente, Redes Neurais Convolucionais, o mecanismo de otimização proposto demonstra ser capaz de melhorar a eficiência energética da GPU em até 44% sem qualquer deterioração relevante da precisão do modelo de rede neural a ser treinado.

**Palavras-chave:** Unidade de Processamento Gráfico, Escalonamento Dinâmico de Tensão e Frequência, Redução da Tensão, Mecanismo de Optimização, Aprendizagem Profunda, Redes Neuronais Profundas.

### Abstract

Nowadays, Graphics Processing Units (GPUs) are the primary computational devices used to accelerate highly parallel applications. However, this immense performance comes at the cost of high energy consumption. Several solutions can be adopted to increase the energy-efficiency of these devices. Though, Voltage-Frequency (V-F) scaling has been the one that achieves the best results, by allowing to automatically improve this metric and independently of the workload. However, current implementations of Dynamic Voltage and Frequency Scaling (DVFS) on GPUs are still one-dimensional, by simply adjusting frequency while relying on default voltage settings. To overcome this limitation, this dissertation introduces a new methodology to fully characterize the impact of non-conventional DVFS on GPUs. To attain this objective, the proposed approach defines a Usable Execution Space (UES) that determines the tolerable voltage range allowed by each frequency. The conducted experimental evaluation, using two out-of-the-shelf AMD GPUs, demonstrated that these particular devices are able to be safely undervolted by more than 20%. The devised UES is then used by a conceived V-F optimization mechanism, which was created to automatically select the most energy-efficiency configuration. When applied to Deep Learning applications and, specifically, Convolutional Neural Networks (CNNs), the proposed optimization mechanism can improve the GPU energy efficiency by up to 44% without any measured deterioration of the CNN model accuracy.

**Keywords:** Graphics Processing Unit, Dynamic Voltage and Frequency Scaling, Undervoltage, Optimization Mechanism, Deep Learning, Deep Neural Networks.

## Contents

|   | Ackr  | nowledg  | gments                                             | v    |

|---|-------|----------|----------------------------------------------------|------|

|   | Res   | umo .    |                                                    | vii  |

|   | Abst  | tract .  |                                                    | ix   |

|   | List  | of Table | 98                                                 | xv   |

|   | List  | of Figu  | res                                                | xvii |

|   | List  | of Acro  | nyms                                               | xxi  |

| 1 | Intro | oductio  | n                                                  | 1    |

|   | 1.1   | Objec    | tives                                              | 2    |

|   | 1.2   | Main (   |                                                    | 2    |

|   | 1.3   | Disser   | rtation Outline                                    | 3    |

| 2 | Bac   | kgrour   | ıd                                                 | 5    |

|   | 2.1   | Gener    | al Purpose Computing on GPUs                       | 5    |

|   |       | 2.1.1    | General Overview of a GPU Architecture             | 6    |

|   |       | 2.1.2    | GPU programming model                              | 7    |

|   | 2.2   | CMOS     | S Circuit Characterization                         | 7    |

|   |       | 2.2.1    | Propagation delay and circuit critical path        | 8    |

|   |       | 2.2.2    | Voltage guardband, PVT Variation and Aging         | 10   |

|   |       | 2.2.3    | Power Consumption                                  | 12   |

|   | 2.3   | Dynar    | nic Voltage and Frequency Scaling                  | 13   |

|   |       | 2.3.1    | Control Mechanism                                  | 14   |

|   |       | 2.3.2    | GPU DVFS Characterization                          | 17   |

|   |       | 2.3.3    | DVFS Optimization                                  | 19   |

|   |       | 2.3.4    | Decoupled V-F - Non-conventional DVFS optimization | 21   |

|   | 2.4   | Under    | voltage and Imprecision tolerant applications      | 23   |

|   | 2.5   | Summ     | nary                                               | 24   |

| 3 | GPL   | J archit | tectural characterization to decoupled V-F         | 25   |

|   | 3.1   | Chara    | cterization Benchmarks                             | 26   |

|   | 3.2   | Exper    | imental Setup and Methodology                      | 32   |

|   |       | 3.2.1    | Voltage and Frequency control API                  | 33   |

|   |     | 3.2.2   | Testing procedure                                                | 34 |

|---|-----|---------|------------------------------------------------------------------|----|

|   | 3.3 | Limitin | g components to the voltage exploration space                    | 34 |

|   |     | 3.3.1   | DRAM                                                             | 35 |

|   |     | 3.3.2   | Cache                                                            | 35 |

|   |     | 3.3.3   | Shared Memory                                                    | 36 |

|   |     | 3.3.4   | Arithmetic and Logic Unit                                        | 36 |

|   |     | 3.3.5   | Non-linear Operations                                            | 37 |

|   |     | 3.3.6   | Branches                                                         | 39 |

|   |     | 3.3.7   | Reduction                                                        | 39 |

|   |     | 3.3.8   | General Comments and Remarks                                     | 40 |

|   | 3.4 | Effect  | of a decoupled V-F scaling on performance and energy consumption | 42 |

|   |     | 3.4.1   | DRAM                                                             | 42 |

|   |     | 3.4.2   | Cache and Shared Memory                                          | 43 |

|   |     | 3.4.3   | Arithmetic and Logic Unit                                        | 44 |

|   |     | 3.4.4   | Non-linear Operations                                            | 46 |

|   | 3.5 | Tempe   | erature Model                                                    | 47 |

|   | 3.6 | Summ    |                                                                  | 48 |

| 4 | Dec | oupled  | V-F Optimization Mechanism                                       | 49 |

|   | 4.1 | Decou   | pled V-F Optimization Mechanism description                      | 50 |

|   |     | 4.1.1   | Architecture and Execution Overview                              | 50 |

|   | 4.2 | Optim   | ization Mechanism Implementation                                 | 55 |

|   | 4.3 | Library | y description                                                    | 56 |

|   | 4.4 | Summ    | nary                                                             | 58 |

| 5 | Арр | licatio | n to Deep Learning                                               | 59 |

|   | 5.1 | Deep    | Learning Overview                                                | 59 |

|   |     | 5.1.1   | Deep Neural Networks                                             | 60 |

|   |     | 5.1.2   | DNN Architectures                                                | 60 |

|   |     | 5.1.3   | Training and Inference                                           | 62 |

|   |     | 5.1.4   | High-Level Libraries and Software Frameworks                     | 62 |

|   | 5.2 | DNN F   | Performance and Energy Efficiency Improvement                    | 63 |

|   | 5.3 | Non-c   | onventional V-F on CNNs                                          | 64 |

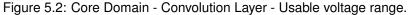

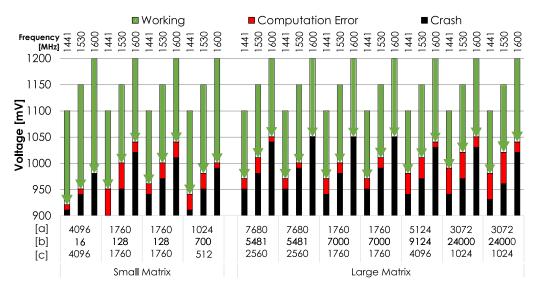

|   |     | 5.3.1   | Convolution Layer                                                | 64 |

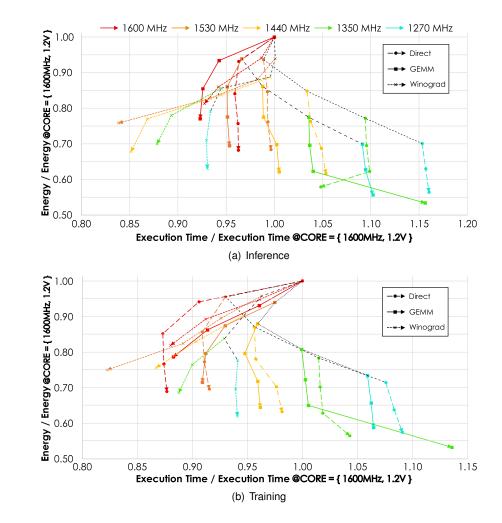

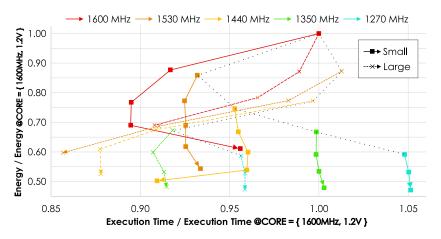

|   |     | 5.3.2   | Fully-Connected Layer                                            | 67 |

|   |     | 5.3.3   | Error Analysis                                                   | 68 |

|   | 5.4 | CNN t   | raining and inference with non-conventional V-F                  | 70 |

|   |     | 5.4.1   | Feasibility Assessment                                           | 70 |

|   |     | 5.4.2   | Optimization algorithm adaptation to CNN training                | 72 |

|   |     | 5.4.3   | Experimental Results                                             | 76 |

|     | 5.5   | Summary                                               | 78 |

|-----|-------|-------------------------------------------------------|----|

| 6   | Con   | clusions                                              | 81 |

|     | 6.1   | Future Work                                           | 82 |

| Bil | oliog | raphy                                                 | 85 |

| Α   | How   | to control and set the desired V-F pair with rocm-smi | 93 |

|     | A.1   | AMD Vega 10 Frontier Edition                          | 94 |

|     | A.2   | AMD Radeon 5700 XT                                    | 95 |

# **List of Tables**

| 2.1 | GPU core and memory performance levels for the AMD Vega 10 Frontier Edition GPU         | 14 |

|-----|-----------------------------------------------------------------------------------------|----|

| 3.1 | Devised set of kernels to characterize GPU to Non-Conventional DVFS                     | 26 |

| 3.2 | Considered GPUs in the conducted experimental characterization.                         | 32 |

| 5.1 | Convolution Parameters                                                                  | 64 |

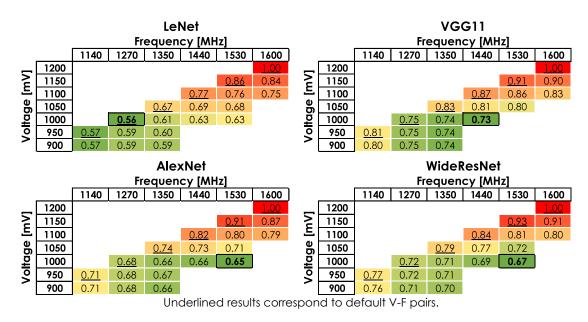

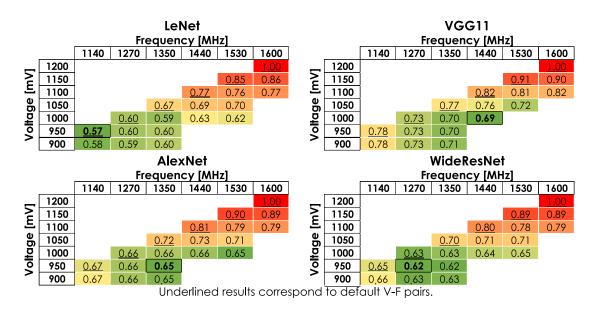

| 5.2 | Comparing CNN training test set accuracy with the application of different undervoltage |    |

|     | levels                                                                                  | 71 |

| 5.3 | Evaluation of performance, energy, and EDP when applying non-conventional DVFS in       |    |

|     | the training of neural networks.                                                        | 74 |

| 5.4 | Mode of selected V-F configurations at the end of each optimization stage               | 78 |

| A.1 | Vega 10 GPU core performance levels general configuration.                              | 94 |

| A.2 | Radeon 5700 XT GPU core V-F pairs general configuration.                                | 96 |

# **List of Figures**

| 2.1  | AMD's Graphics Core Next logical organization                                                          | 6  |

|------|--------------------------------------------------------------------------------------------------------|----|

| 2.2  | a) CMOS inverter. b) Noise margin definitions: $NM_L = V_{IL} - V_{OL}$ and $NM_H = V_{OH} - V_{IH}$ . | 8  |

| 2.3  | Logic gate propagation delay: $tp_{HL}$ - propagation delay high to low; $tp_{LH}$ - propagation       |    |

|      | delay low to high                                                                                      | 8  |

| 2.4  | First order RC circuit and its corresponding temporal response to step input.                          | 9  |

| 2.5  | Critical path between two registers (red dashed line)                                                  | 9  |

| 2.6  | Voltage guardband ensures reliability by making the transistors switching faster                       | 10 |

| 2.7  | Voltage guardband ensures operation reliability by effectively inserting some extra timing             |    |

|      | margin.                                                                                                | 11 |

| 2.8  | GPU Core voltage frequency curve, red dots indicate the default user-defined voltage                   |    |

|      | frequency pair - AMD Radeon 5700 XT.                                                                   | 14 |

| 2.9  | Interval-based DVFS procedure.                                                                         | 15 |

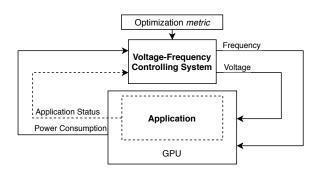

| 2.10 | AMD/NVIDIA DVFS control mechanism.                                                                     | 16 |

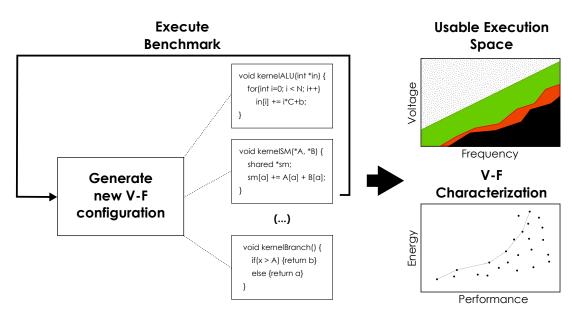

| 3.1  | Overview of the methodology and its objective outputs                                                  | 26 |

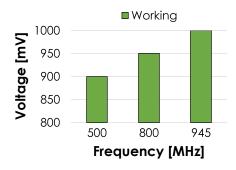

| 3.2  | Vega 10 - DRAM domain - Usable voltage for each frequency configuration.                               | 35 |

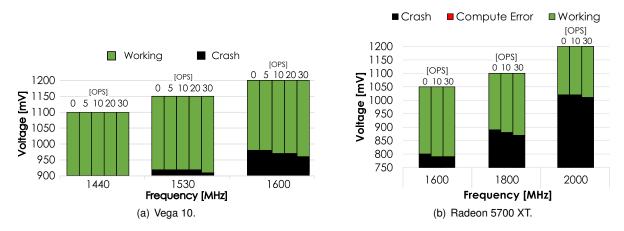

| 3.3  | Core domain - Cache L2 - Usable voltage for each frequency configuration with varying                  |    |

|      | cache stress ( <i>OPS</i> value)                                                                       | 36 |

| 3.4  | Core domain - Shared Memory - Usable voltage range for each frequency configuration                    |    |

|      | with varying shared memory stress (OPS parameter)                                                      | 37 |

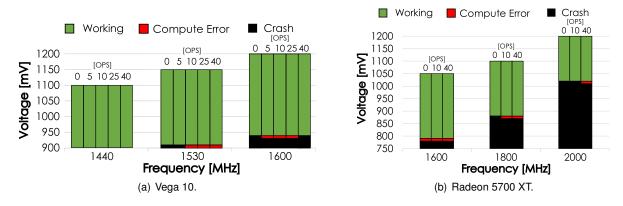

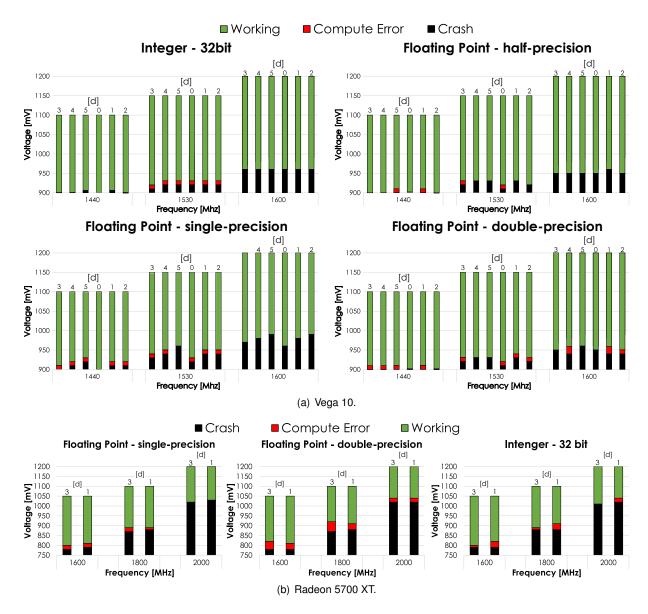

| 3.5  | Core domain - ALU-MAC - Usable voltage margins for the different data types and operand's              |    |

|      | precision.                                                                                             | 38 |

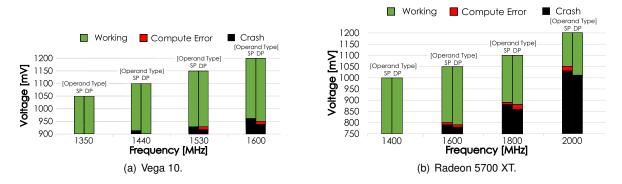

| 3.6  | Core domain - Special Function Unit - Usable voltage for each frequency configuration                  |    |

|      | with varying operand type: SP - Single Precision Floating-Point, DP - Double Precision                 |    |

|      | Floating-Point.                                                                                        | 38 |

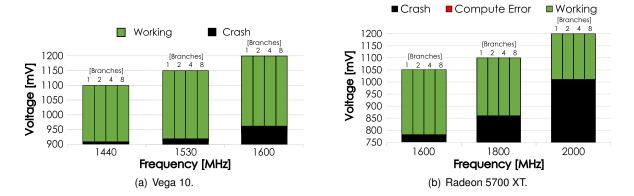

| 3.7  | Core domain - Branches - Usable voltage for each frequency configuration with varying                  |    |

|      | number of branches per iteration                                                                       | 39 |

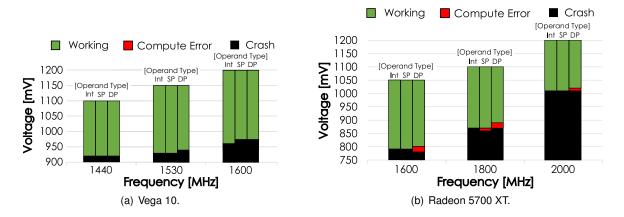

| 3.8  | Core domain - Reduction benchmark - Usable voltage for each frequency configuration                    |    |

|      | with varying operand type: Int - 32-bit Integer, SP - Single Precision Floating-Point, DP -            |    |

|      | Double Precision Floating-Point.                                                                       | 39 |

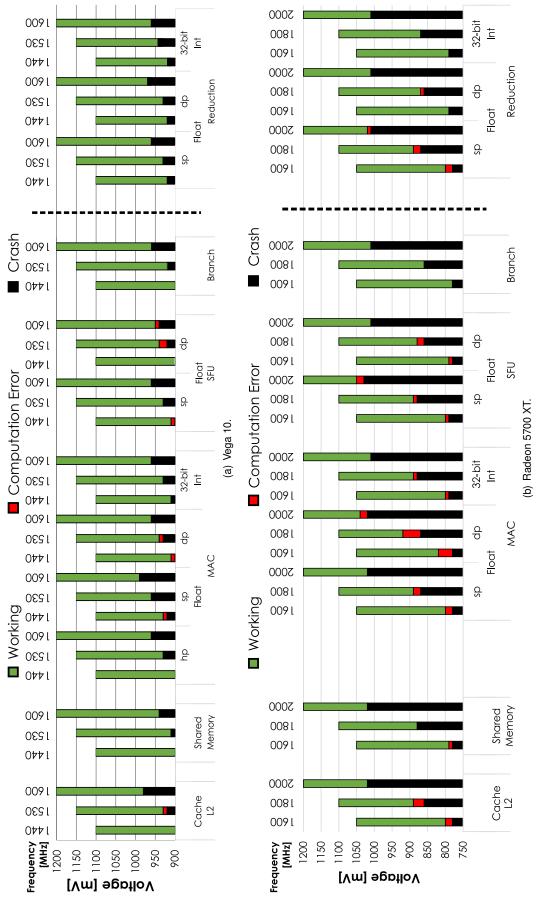

| 3.9  | Comparison of usable GPU core voltage ranges for all the considered architectural com-<br>ponents of the GPU.                                                        | 41 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 10 |                                                                                                                                                                      | 71 |

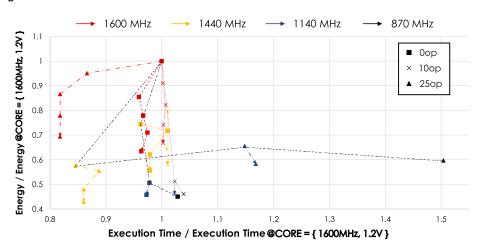

| 3.10 | Vega 10 - DRAM domain - DRAM benchmark - Normalized energy consumption and execution time. Each connected data point represents a $50mV$ undervoltage in relation to |    |

|      | the previous one.                                                                                                                                                    | 42 |

| 0.14 |                                                                                                                                                                      | 42 |

| 3.11 | Vega 10 - Core domain - DRAM - Normalized energy consumption and execution time.                                                                                     |    |

|      | The dashed line connects the default V-F configurations and each connected data point                                                                                | 43 |

| 0.40 | represents a $50mV$ undervoltage in relation to the previous one.                                                                                                    | 43 |

| 3.12 | Core domain - Cache L2 - Normalized energy and performance variations with OPS=0.                                                                                    |    |

|      | The dashed line connects the default F-V configurations.                                                                                                             | 44 |

|      | Core domain - Cache L2 - Obtained normalized Energy-Delay Product (EDP) with OPS=0.                                                                                  | 44 |

| 3.14 | Core domain - Shared Memory - Normalized energy consumption and execution time.                                                                                      |    |

|      | The dashed line connects the default F-V configurations and each connected data point                                                                                |    |

|      | represents a $50mV$ undervoltage in relation to the previous one.                                                                                                    | 45 |

| 3.15 | Core domain - Shared Memory - Obtained normalized Energy-Delay Product (EDP) with                                                                                    |    |

|      | OPS=0                                                                                                                                                                | 45 |

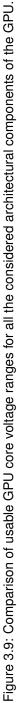

| 3.16 | Core domain - ALU-MAC - Normalized energy and performance chart for the benchmark                                                                                    |    |

|      | setup with different values of a for single precision floating-point (see Listing 3.5). The                                                                          |    |

|      | dashed lines connect the results for default F-V configurations.                                                                                                     | 45 |

| 3.17 | Core domain - ALU-MAC - Obtained normalized Energy-Delay Product (EDP) for $\tt d=1,3.$ .                                                                            | 46 |

| 3.18 | Core domain - Special Function Unit - Normalized energy and performance for single-                                                                                  |    |

|      | precision floating-point data type. The dashed lines connect the results for default F-V                                                                             |    |

|      | configurations.                                                                                                                                                      | 46 |

| 3.19 | Core domain - Special Function Unit - Obtained Energy-Delay Product (EDP) for single-                                                                                |    |

|      | precision floating-point data type                                                                                                                                   | 47 |

| 3.20 | Undervoltage capabilities with changing temperature condition and defined temperature                                                                                |    |

|      | model                                                                                                                                                                | 47 |

| 4.1  | V-F Optimization Mechanism Block Diagram.                                                                                                                            | 51 |

| 4.2  | User provided input example for the optimization mechanism (left) and correspondent                                                                                  |    |

|      | usable execution space chart (rigth). Black-shaded regions represent unusable operation                                                                              |    |

|      | points (GPU crash), while green shaded regions represent tested DVFS operating points.                                                                               | 51 |

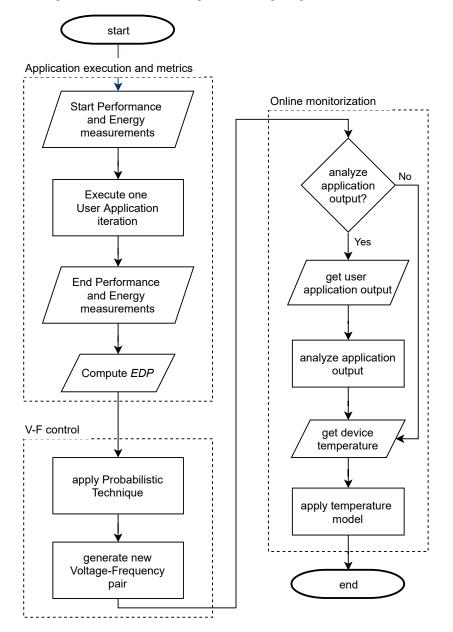

| 4.3  | Flowchart of each iteration of the Optimization Algorithm Execution.                                                                                                 | 52 |

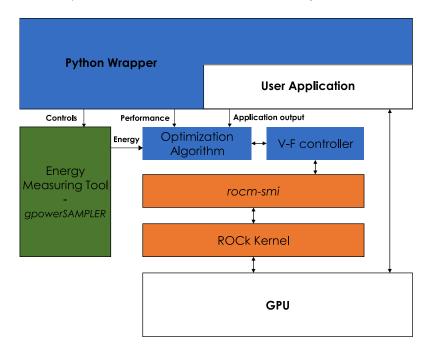

| 4.4  | Layer diagram of the developed V-F Optimization Mechanism. The blocks colored in blue                                                                                |    |

|      | represent the developed parts of the optimization mechanism developed in the context of                                                                              |    |

|      | this dissertation.                                                                                                                                                   | 56 |

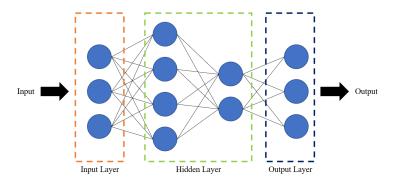

| 5.1  | Model of fully-connected (feed-forward) DNN                                                                                                                          | 60 |

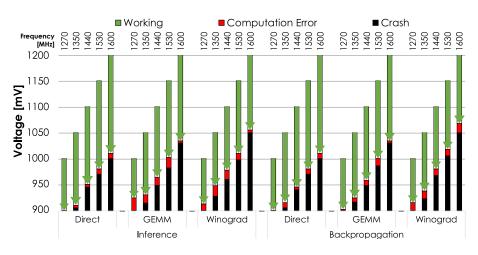

| 5.2  | Core Domain - Convolution Layer - Usable voltage range.                                                                                                              | 65 |

| 5.3  | Core domain - Convolution Layer normalized energy and performance chart to non-convention V-F configurations. | nal<br>66 |

|------|---------------------------------------------------------------------------------------------------------------|-----------|

| 5.4  | Core Domain - Convolution Layer - Obtained normalized Energy-Delay Product heat-map                           |           |

|      | for the three algorithms.                                                                                     | 67        |

| 5.5  | Core Domain - Fully-Connected Layer - Usable GPU core voltage range. [a], [b] and [c]                         |           |

|      | values represent matrix sizes (example $A_{a \times b} \cdot B_{b \times c}$ ).                               | 68        |

| 5.6  | Core Domain - Fully-Connected Layer normalized energy and performance chart to non-                           |           |

| 0.0  | conventional V-F configurations.                                                                              | 68        |

| 5.7  | Core Domain - Fully-Connected Layer - Obtained normalized Energy-Delay Product heat-                          |           |

| -    | map                                                                                                           | 69        |

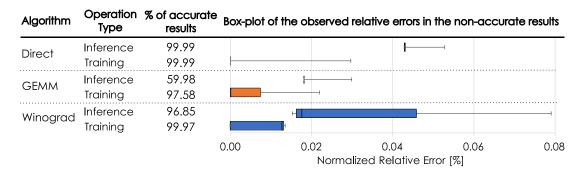

| 5.8  | Convolution Layer - Average percentage of accurate results and relative error distribution                    |           |

| 0.0  | of non-accurate outputs for the minimum usable core voltage across all considered core                        |           |

|      | frequency values.                                                                                             | 70        |

| 5.9  | Fully Connected Layer- Average percentage of accurate results and relative error distri-                      |           |

| 0.0  | bution of non-accurate outputs for the minimum usable core voltage across all considered                      |           |

|      | core frequency values.                                                                                        | 70        |

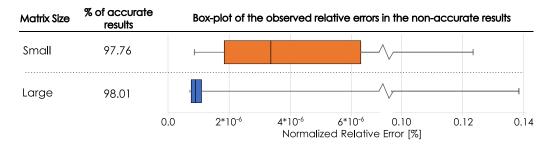

| 5.10 | Core domain - CNN models - superposition of all V-F configuration test set loss and model                     |           |

| 00   | accuracy                                                                                                      | 72        |

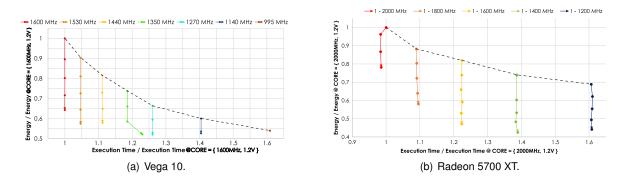

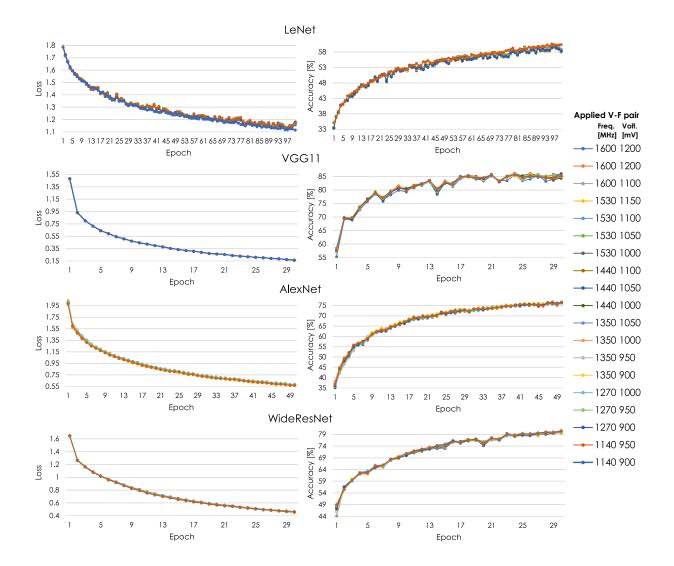

| 5.11 | Core domain - CNN models - Normalized energy consumption and execution time for                               | . –       |

|      | training + inference. The dashed line connects the default V-F pairs, and the diagonal                        |           |

|      | striped pattern indicates the plateau of minimum energy consumption.                                          | 73        |

| 5.12 | Core domain - CNN models - Obtained normalized Energy-Delay Product (EDP) for train-                          |           |

|      | ing + inference                                                                                               | 73        |

| 5.13 | Core domain - CNN models - Obtained normalized Energy-Delay Product (EDP) for infer-                          |           |

|      | ence phase                                                                                                    | 74        |

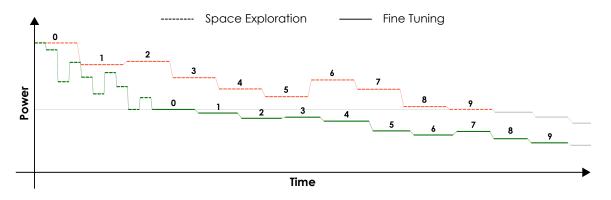

| 5.14 | Graphical representation of the power consumption overtime of the first ten training epochs                   |           |

|      | of a CNN model (numbers 0 to 9 represent the execution of training epochs). The orange                        |           |

|      | line represents the case where the training procedure is started at the Space Exploration                     |           |

|      | stage, and the green line represents the case where the training procedure is only started                    |           |

|      | on the Fine-Tuning stage.                                                                                     | 75        |

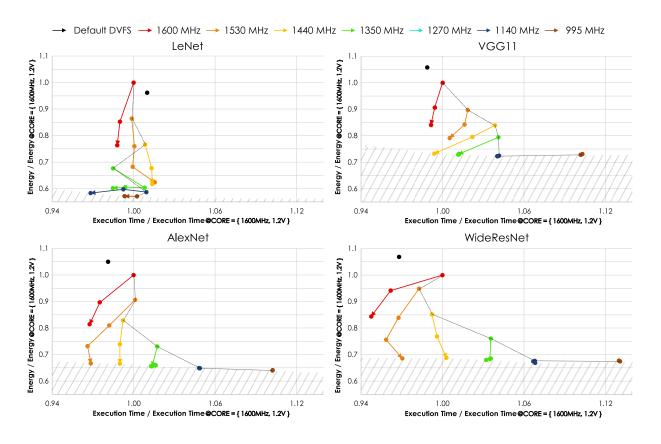

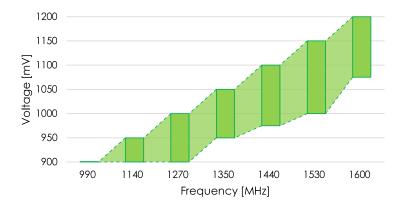

| 5.15 | Usable Execution Space for the Vega 10 GPU.                                                                   | 76        |

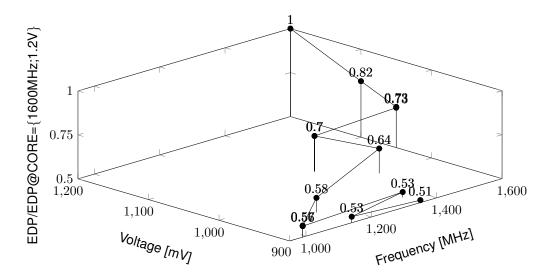

|      | WideResNet Space Exploration example - normalized EDP values for 20 epochs. Initial                           |           |

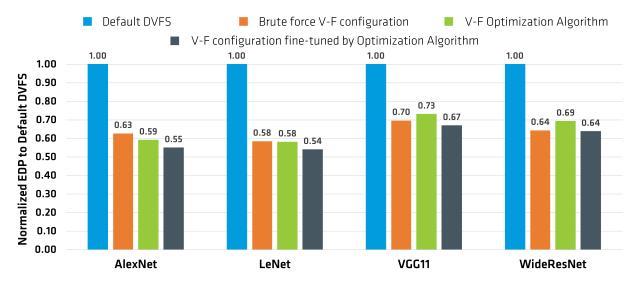

|      | value is 1600MHz and 1.2V.                                                                                    | 77        |

| 5.17 | Median normalized EDP of default DVFS vs training CNN with V-F optimization model                             | 78        |

|      |                                                                                                               |           |

| A.1  | Rocm-smi interface.                                                                                           | 93        |

| A.2  | Change in voltage curve to select a given V-F pair.                                                           | 95        |

## List of Acronyms

AFVS Adaptive Frequency and Voltage Scaling. ALU Arithmetic and Logic Unit. API Application Protocol Interface. **ApSA** Application-aware Scalable Architecture. **BTI** Bias temperature instability. CMOS Complementary metal-oxide-semiconductor. **CNN** Convolutional Neural Network. CPU Central Processing Unit. **CU** Computing Unit. **DL** Deep Learning. **DNN** Deep Neural Network. **DRAM** Dynamic Random-Access Memory. DVFS Dynamic Voltage and Frequency Scaling. **EDP** Energy Delay Product. GAN Generative Adversarial Network. GPGPU General Purpose Graphical Processing Unit. GPU Graphical Processing Unit. HCI Hot Carrier Injection. HSA Heterogeneous System Architecture. **MAC** Multiply and Accumulate. NCU Next Compute Unit. **PVT** Process, Voltage and Temperature. **RISC** Reduced Instruction Set Computer. **RMSE** Root Means Square Error. **RNN** Recurrent Neural Network. **ROC** Radeon Open Computing platform. SFU Special Function Unit. SGD Stochastic Gradient Descent. **SIMT** Single Instruction Multiple Threads. SM Streaming Multiprocessor.

**UPT** Unsupervised Pre-trained Network.

### **Chapter 1**

### Introduction

Graphical Processing Units (GPUs) were brought to life in the advent of computer graphics in the hopes of improving the capabilities of 3D games. However, the increased parallel computing capabilities exhibited by these devices made them highly appealing to running more general computational demanding applications, coining the term GPGPU - General-Purpose Graphical Processing Units.

Along this path, the development of new architectural generations of GPU devices has traditionally aimed at improving performance and throughput. However, having already reached the maximum supported power consumption and with device fabrication techniques being harder and harder to minimize, extra performance gains need to come while keeping the pace for a greater GPU energy-efficiency.

Researchers have been looking for ways to decrease power consumption to improve energy efficiency with some degree of success, with new architectural designs targeting, for example, operation with lower precision encoding (reduced number of bits) to reduce the number of combinatorial logic. Nevertheless, techniques such as Dynamic Voltage and Frequency Scaling (DVFS) are still the ones that are having a more direct impact on the industry, by being widely available on current out-of-the-shelf devices. These systems' working principle is to carefully select from a list of voltage-frequency (V-F) pairs, the one that should be used, in order to target the current GPU state. Since the dissipated power is directly proportional to the applied frequency and to the square of the applied voltage, the variation of these parameters directly and significantly impacts the devices' power and energy consumption.

In theory, DVFS systems are able to find the V-F configuration that achieves better energy efficiency. Nevertheless, practical implementations of such mechanisms seem to exhibit two flaws: i) they do not consider the running application characteristics and ii) use pre-defined V-F pairs that are conservatively selected by manufacturers. In particular, at each frequency level, the chosen voltage supply is set at a level that leaves a significant voltage margin in relation to the necessary one. Such margin is put in place to guarantee a safe operation under all conditions. However, recent studies prompt the idea that such conservative voltage margin is leaving a significant energy-efficiency gain on the table [1].

Supported on this observation, it has been recognized that the correct utilization of non-conventional V-F pairs may improve the energy-efficiency of already deployed GPUs.

One particular application domain that can significantly benefit from such energy-efficiency improvements is Deep Learning, and more specifically, Deep Neural Networks (DNNs). These algorithms are having a significant impact on industry and society by allowing for important breakthroughs in many application domains, such as computer vision, speech recognition, natural language processing, drug discovery, genomics, etc [2]. However, DNNs are usually characterized by significant computational burdens, particularly when considering the training of very deep and complex networks, dealing with high dimensional data, such as images and videos. Another important characteristic of DNNs is their tolerance to a certain degree of computation errors [3], without any significant change in the training and inference results.

Therefore, the creation of a novel DVFS system that explores and selects non-conventional V-F pairs by considering the specific target application characteristics can allow for a substantial decrease in the energy consumed to train and deploy Deep Learning applications [4].

### 1.1 Objectives

To uncover the use of non-conventional V-F scaling, this thesis focuses on the following objectives:

- Access the viability of using non-conventional V-F pairs on regular GPUs.

- Characterize the behavior of GPU architectures to non-conventional V-F pairs.

- Develop a dynamic non-conventional V-F controlling and optimization mechanism that improves the *performance*, *energy consumption* or *energy-efficiency* of GPUs.

- Safely apply non-conventional V-F scaling on Deep Learning applications, characterizing the behavior of the training procedure.

### 1.2 Main Contributions

The work conducted in the scope of this dissertation contributes to open the discussion of further improving the current GPU DVFS systems, by exploring the conservative voltage guardband put in place by device manufacturers. The developed work demonstrates that non-conventional voltage-frequency (V-F) pairs are mostly allowed by out-of-the-shelf devices, leading to great energy-efficiency benefits and, in some cases, even performance enhancements.

To demonstrate and validate the use of those new V-F configurations, a new methodology was developed to test each architectural component of the GPU, analyzing and evaluating its specific voltage margin and characterizing their energy-performance behavior when subject to such configurations. The methodology was tested in two different architectural generation devices, both of them exhibiting a high tolerance to undervoltage.

Furthermore, to more easily benefit from the usable execution space that was defined by executing the set of benchmarks that compose the formulated methodology, a new V-F optimization mechanism was devised. The mechanism makes use of the native code repetition patterns, usually observed in GPGPU applications, to improve the applied V-F pair iteratively, taking into account not only the GPU power consumption, utilization and temperature (as it is done by current DVFS systems) but also the running application characteristics. With the use of such a conceived optimization mechanism, it is possible to perform dynamic voltage and frequency scaling while taking into account each application's intrinsic behavior and benefiting from the energy-efficiency improvements granted by the non-conventional V-F pairs.

To evaluate the proposed methodology and optimization mechanism, it was applied to the training procedure of deep learning applications, specifically the training of convolutional neural networks. The conducted evaluation explored the voltage margins and behavior of the fundamental algorithms that compose this type of operations, the distribution of the computational error that appears when using the lowest allowed voltage by the architecture and finally, the energy-efficiency improvement that is achieved by the V-F optimization mechanism when targeting the execution of this type of algorithms. In particular, the description of the performed work targeting the training of neural networks helps to understand the complete flow of actions that should be taken to take full advantage of exploring the conservative voltage guardband put in place by device manufacturers, and with that, improve the energy-efficiency of current out-of-the-shelf GPUs.

The main scientific contributions of this work have been published for communication in the following conference:

F. Mendes, P. Tómas and N. Roma, "Exploiting non-conventional DVFS on GPUs: application to Deep Learning", IEEE 32nd International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD'2020), 2020.

### 1.3 Dissertation Outline

This dissertation is organized in 5 chapters and one appendix, with the following outline:

- Chapter 2 Background: This chapter presents a summary of the current state-of-the-art related to the subject in focus on this dissertation. First, it introduces an overview of general-purpose computing on GPUs, providing a summary of their architecture and programming model. It presents the key concepts that should be present when developing for this kind of devices and the standard programming interfaces between the GPU and the host CPU. A bottom-up approach is also drawn to present the fundamental concepts of frequency and voltage scaling on CMOS devices, and how they translate to the current DVFS systems presented in out-of-the-shelf GPUs. It finalizes by granting a sketch of how better exploring and going against the conventional voltage-frequency scaling allows for better energy efficiency of GPUs, being that the stepping stone of this dissertation.

- Chapter 3 GPU architectural characterization to decoupled V-F: In this chapter, the developed methodology to characterize the use of non-conventional V-F scaling is presented. The chapter starts by exploring each developed stressing component benchmark's motivation and objectives, and it follows by testing the methodology in two different GPU architectures. The methodology is used to: determine the minimum voltage allowed by each architectural component and evaluate the performance, energy consumption and energy efficiency, when prompting non-conventional V-F pairs on them. It finishes by experimentally testing the effects of temperature on the undervoltage capabilities of the GPU architecture.

- Chapter 4 V-F Optimization Mechanism: This chapter analyses and proposes a solution to dynamically adjust the frequency and voltage using the newly tested non-conventional V-F pairs. Programmers can execute their algorithms using this tool, while the most energy-efficient V-F

configuration is being discovered, targeting the current GPU state and performance metrics, and application output.

- Chapter 5 Application to Deep Learning: In this chapter, the previous two chapters' results are combined and used to apply the developed methodology on a deep learning application. This chapter has three objectives: showcase the practical advantages of extending the default voltagefrequency scaling with non-conventional V-F pairs on a target application; evaluate the use of the developed optimization mechanism, and, overall, the chapter indicates how a user should proceed to safely and beneficially use the work developed in this dissertation.

- Chapter 6 Conclusions: This final chapter presents the accomplished results from this work and the possible research directions to take in future work.

- Appendix A: This appendix presents all the necessary steps and commands to control the rocmsmi tool with the objective of setting the desired voltage-frequency pair on the target GPUs.

### **Chapter 2**

### Background

This chapter provides an overview of modern GPU architecture and respective programming models that allow the extensive use of these devices to execute more computationally intensive applications, followed by an analysis of techniques to improve the energy efficiency of the same.

The following sections present a bottom-up sequence of background and related work that supports this thesis — starting by the physical analysis of the digital circuits and the effects of V-F scaling and temperature on them. It continues by presenting the most common procedure to improve GPUs energy efficiency (DVFS) and finishes by exploring the techniques that will allow for further improvements to these device based on a complete decoupling between the applied voltage supply and operating frequency.

The relevance of the presented work emerges from the reduced number of studies on the effects of decoupled voltage scaling on GPUs, one of the objectives of this dissertation. The main reason is probably mainly due to lack of support for independently controlling these parameters on NVIDIA GPUs (until recently, the dominant player on the market [5, 6]) that is now allowed by the novel AMD software stack used on this work.

### 2.1 General Purpose Computing on GPUs

A GPU is a highly parallel programmable processor, that favours the execution of the same instruction on multiple data elements, belonging to the category of *Single Instruction Multiple Threads* - SIMT processors. When referring to GPUs, it is still common to be talking about their graphics capabilities. However, more and more programs are taking advantage of their highly parallel architecture to accelerate general purpose applications, leading to the connotation of this device as a GPGPU - General Purpose Graphical Processing Unit.

The development and deployment of GPGPU applications are only possible with the creation and adoption of standardized programming models and APIs that allow for hardware abstraction. This section provides a general overview of the GPU architecture, followed by the presentation of the most common and used software tools available for GPGPU programming.

### 2.1.1 General Overview of a GPU Architecture

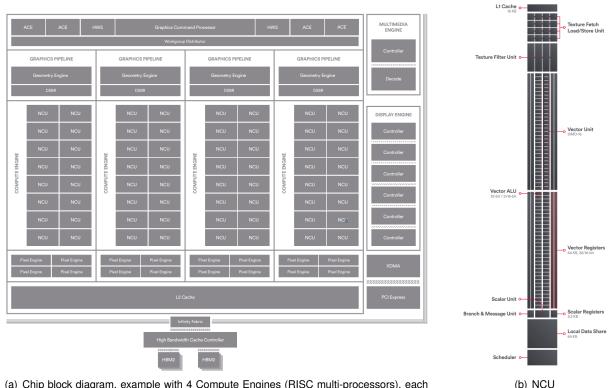

The architecture of a modern GPU, depicted in figure 2.1, can be roughly divided into computation and memory components. The computation part is usually composed of the vertex shader, the rendering engine, and the RISC processors. The vertex shader and rendering engine are included on the graphics pipeline and are not generally used on GPGPU applications. The RISC processors are responsible for the GPU programmable calculations and depending on the manufacturer, they are denoted as streaming multiprocessors (SM) in NVIDIA GPUs [7] or computing units (CU) in AMD GPUs [8].

(a) Chip block diagram, example with 4 Compute Engines (RISC multi-processors), each with 16 NCU (Compute Units)

Figure 2.1: AMD's Graphics Core Next logical organization.

As it was referred before, one of the significant benefits of GPUs is, the ability to concurrently execute multiple threads. To accomplish that, each SM or CU is made up of hundreds of execution units. However, to manipulate such number of threads, it is necessary to have a significantly large and fast memory system, not only to save the context of each thread, but also to provide low-overhead context switching between the different sets of threads being executed. In that sense, modern GPU architectures include a large register file on each SM/CU (when compared to the number of registers presented in a CPU core). For reference, in the AMD GNC architecture, each CU has 49,152 (32-bit) registers [9].

In terms of memory, both the AMD and the NVIDIA GPUs present a 3 level hierarchy system: a global memory, accessible by all SM/CU (generally referred to as video memory); a shared memory associated to each SM or CU, accessible by the threads running on that SM or CU; and a set of read-only caches for constants and textures, specific to each execution unit.

A GPU device from AMD will be used to conduct the experimental part of this dissertation. For that reason, the terminology used by AMD will be adopted herein. However, the presented work is independent of the hardware and terminology itself, and could equally be applied to NVIDIA GPUs.

#### 2.1.2 GPU programming model

The development of CUDA [10] (by NVIDIA) and OpenCL [11] (by Khronos Group) were the driving force to using GPUs in general programming. CUDA and OpenCL are both parallel computing platforms and application programming interfaces (API) that allow developers to create GPU-accelerated applications, splitting the computations between the CPU and GPU. The first versions of these frameworks treated the GPU as an accelerating slave device, providing a set of directives that allow the CPU (master device) to transfer data, synchronize and control the GPU. Though, to take full advantage of the GPU architecture and create a true heterogeneous system, the CPU and GPU have to collaborate more efficiently. The creation of the Heterogeneous System Architecture (HSA) [12] framework acts on improving this problem by acting as a low-level intermediary API to provide improved coordination and communication for heterogeneous computing systems. More recently, AMD introduced the Radeon Open Computing platform (ROC) [13]. Like CUDA and OpenCL, ROC provides a set of tools that allow developers to create heterogeneous applications. Being a newer software stack, already built on the notions and added benefits of HSA runtime API, ROC allows the use of a wider set of programming frameworks like OpenCL<sup>1</sup>, HCC<sup>2</sup>, and HIP<sup>3</sup>.

This programming model is rather similar across the different platforms, with developers traditionally programming the GPUs using general-purpose languages like C, C++ and Fortran. More recently, the manufacturers are also starting to provide direct access to the GPU through higher-level languages like Python<sup>4</sup>, allowing for an easier development and adoption of GPUs as accelerating devices.

Overall, when executing a program on GPUs, using either of the previously mentioned platforms, a kernel is invoked on the GPU, that will execute across several parallel threads. Following this work split, the frameworks expose three levels of abstraction: *threads, thread blocks* and *block grid*. The number of *threads* to be executed can be explicitly defined by the programmer, or implicitly set by the compiler. The *threads* are grouped in *thread blocks* containing an amount of *threads*, and the *thread blocks* are in turn arranged in a *block grid*. When the Kernel is executed, the scheduler maps each *thread block* onto a CU. Due to this mapping, *threads* within a *thread block* are able to communicate over the CU shared memory and their execution is synchronized through programable directives.

During the execution of each *thread*, an identifier presents the location of the running *thread* within the *thread blocks* - ThreadIdx and within the *block grid* - BlockIdx. The *thread block* size can be obtained with the BlockSize directive.

### 2.2 CMOS Circuit Characterization

For the last 40 years, CMOS (Complementary metal-oxide-semiconductor) has been the most used technology in the creation of digital circuits and processors in general [14].

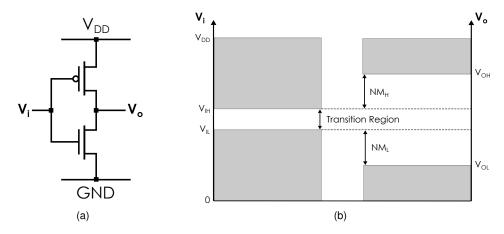

There are two defined logic levels in digital circuits: logic level 0 and 1, each represented by an analog voltage range. To ensure its operations, the circuit requires a DC voltage value  $V_{DD}$ . The logic gates are excited through an input voltage  $V_i$  and an output voltage  $V_o$ , corresponding to the logic level resulting from their logic function (see Figure 2.2(a)). As it is illustrated in Figure 2.2(b), the

<sup>&</sup>lt;sup>1</sup>github.com/RadeonOpenCompute/ROCm-OpenCL-Runtime

<sup>&</sup>lt;sup>2</sup>github.com/RadeonOpenCompute/hcc

<sup>&</sup>lt;sup>3</sup>github.com/ROCm-Developer-Tools/HIP

<sup>&</sup>lt;sup>4</sup>developer.nvidia.com/how-to-cuda-python

voltage range at the input of the logic gates is correctly interpreted if it falls inside a given range. Logic level 0 corresponds to the interval between GND (0V) to  $V_{IL}$ , while logic level 1 corresponds to the interval between  $V_{IH}$  to  $V_{DD}$ . In turn, the output is considered 0 if it goes from GND (0V) to  $V_{OL}$  and logic level 1 from  $V_{OH}$  to  $V_{DD}$ . The limits of the input and output logic levels depend on the intrinsic characteristics of the transistors, such as their dimensions and transconductance values. In addition to the transistors characteristics and operating voltage, any digital circuit is also characterized by their frequency of operation.

Figure 2.2: a) CMOS inverter. b) Noise margin definitions:  $NM_L = V_{IL} - V_{OL}$  and  $NM_H = V_{OH} - V_{IH}$ .

The remaining of this section provides an introduction to the effects of voltage and frequency scaling on the transistor and circuit level operation.

#### 2.2.1 Propagation delay and circuit critical path

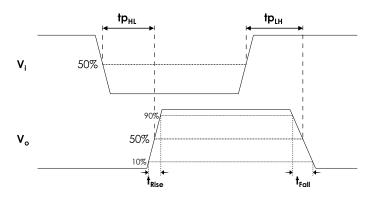

The propagation delay of a logic gate (e.g., inverter) corresponds to the time interval (calculated at 50% of low/high transition) between the application of an input signal and corresponding output switching, as illustrated in Figure 2.3. Considering both transitions low to high and high to low, the logic gate propagation time (tp) corresponds to the average value of the two propagation delays, as defined in Equation 2.1.

Figure 2.3: Logic gate propagation delay:  $tp_{HL}$  - propagation delay high to low;  $tp_{LH}$  - propagation delay low to high.

$$tp = tp_{avg} = \frac{tp_{HL} + tp_{LH}}{2}$$

(2.1)

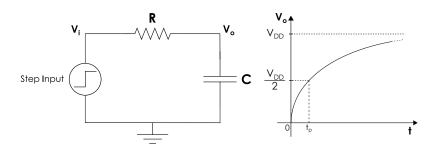

This metric is related to the time that the logic gate takes to switch its output logic level ( $t_{Fall}$  for the high to low transition and  $t_{Rise}$  for the low to high transition). This transition can be modeled as a first-order RC circuit (see Figure 2.4) with the transient response following Equation 2.2, where  $\tau$  corresponds to the time constant. This time constant reflects the intrinsic characteristics of the transistors that make up the logic gate, being  $\tau = RC$ , where R represents the average output resistance of the transistor when it is turned 'ON' and C the output capacitance that the logic gate is driving.

Figure 2.4: First order RC circuit and its corresponding temporal response to step input.

$$V_o = V_{DD} \cdot (1 - e^{-t/\tau})$$

(2.2)

By solving Equation 2.2 for  $V_o = \frac{V_{DD}}{2}$ , it is observed that the propagation delay is a function of the supplied voltage and  $\tau$  (with  $\tau = RC$ ), as depicted in Equation 2.3.

$$t_p = -ln\left(1 - \frac{V_{DD}}{2 \cdot V_{DD}}\right) \cdot \tau = -ln(0.5) \cdot \tau = ln(2) \cdot \tau$$

(2.3)

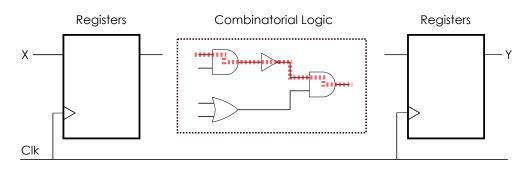

From all the logic paths (sequence of logic gates) that connect any two registers, the one which presents the largest sum of the propagation delay limits the overall maximum frequency that the CMOS circuit can operate, establishing itself as the critical path of the circuit (see Figure 2.5). However, in the particular case of a microprocessor circuit, depending on the operation (instruction) being performed (and so, of the used architectural component), the circuit's critical path can change.

Figure 2.5: Critical path between two registers (red dashed line).

In this way, when scaling the circuit's operating frequency, it is only possible to increase it until it matches the inverse of the critical path propagation delay. When raising the frequency ahead of this value, the critical path is violated, meaning that when the next clock cycle starts, the output of the combinatorial logic may not be the correct one.

### 2.2.2 Voltage guardband, PVT Variation and Aging

After the release of the digital circuit, silicon vendors often deal with variations of their devices' specifications. On the design stage of the circuit, these variations need to be correctly predicted and accounted for, guaranteeing the correct operation of the circuit throughout time and range of conditions that the circuit will be exposed to.

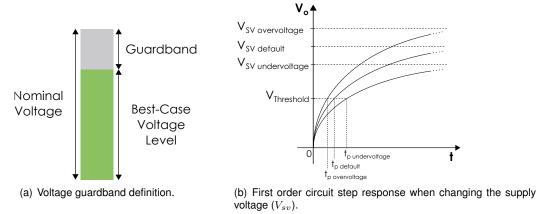

Process, voltage and temperature (PVT) variation and aging impact the circuit in different manners and the solution for all is to put in place a voltage guardband, as defined in Figure 2.6(a). This voltage guardband increases the circuit nominal voltage from the best-case operating voltage selected from the transistors and gates' intrinsic characteristics. In Equation 2.3, the propagation delay is now obtained by considering the ratio between the best-case operating voltage<sup>5</sup>. Hence, when the silicon vendor opts to put in place a voltage guardband, increasing the supplied voltage (overvoltage), the propagation delay will follow Equation 2.4, where  $V_{Threshold}$  depends on the transistors (and so, it does not depend on the supply voltage value) and  $V_{Supply Voltage}$  is the supplier controlled parameter. Figure 2.6(b) illustrates the logic gate step response for over and undervoltage. Increasing the supply voltage will make the transistors switch faster, while decreasing it, reduces the switching pace.

Figure 2.6: Voltage guardband ensures reliability by making the transistors switching faster.

#### Process variation and aging

Process variation and aging impact the circuit in different ways. Process variation is related to the modern fabrication process of silicon. It results from imperfections in the lithography and dopant diffusion, affecting the transistors' dimensions (for example, length and oxide thickness). This dimensionality change between the transistors can occur either intra-die, when devices from the same die present different features depending on their locations, inter-die, meaning that devices from one die can present different traits from devices from another batch of dies. The process variation affects the speed of transistors and the overall circuit characteristics, by varying the device voltage threshold and speed [15, 16]. Such variations are inherent to the fabrication process. Even though silicon manufacturers try to reduce

<sup>&</sup>lt;sup>5</sup>(Threshold voltage) and the considered supply voltage

this impact, such variation will always occur as a *static* variation after the release of the chip to the market.

Aging of the CMOS circuits is a result of ongoing chip temperature variation and supply voltage change. The continuous variation of these two factors induces *Bias Temperature Instability* (BTI) and *Hot Carrier Injection* (HCI). BTI causes threshold voltage shifts over long periods due to the presence of voltage stress at the transistors' gate. On the other side, HCI is caused by the acceleration of carriers (electrons/holes) under lateral electric fields in the channel of MOS devices. The acceleration can get up to the point where the carriers gain enough energy and momentum to cause damage, degrading mobilities and again, changing the threshold voltages [17].

The occurrence of these phenomenons raises the possibility of the circuit not meet its original specifications. Hence, a circuit that is dimensioned without any headroom (not sufficiently large voltage guardband) may not be able to cope with such a process variation - producing a not working circuit; or stopping to work overtime due to aging.

#### Voltage variation

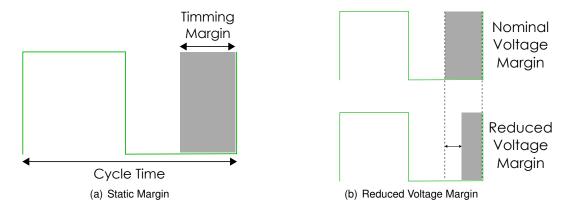

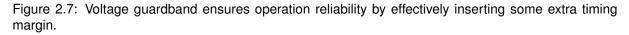

As it was previously observed, running the circuit at an increased voltage compared to the required voltage at the target frequency for typical workloads results in a faster circuit. This increment in performance allows for inserting an extra timing margin in each clock cycle, as described in Figure 2.7.

This timing margin is of extreme importance to cope with voltage noise, the leading cause of voltage variation during the circuit execution. Voltage noise is mainly induced by di/dt droop. This phenomenon makes the actual measured voltage that is applied to the circuit components (as formulated in Equation 2.5), depend on the rate of change of the current being drawn.

$$V_{actual} = V_{DD} - L * \frac{di}{dt}$$

(2.5)

The runtime workload intensity variation induces the di/dt droop due to the rapid and significant change in current demand from the various circuit functional blocks [16]. Thus, in the case of processors, the workload type can directly impact voltage noise. As a result, a program that induces a bigger di/dt droop will need to have a bigger voltage guardband.

#### **Temperature variation**

Temperature variation occurs both due to changes on the environmental temperature, and due to changes in the temperature that is dissipated as heat by the transistors on the circuit. The temperature affects the transistors by changing the carriers' mobility ( $\mu [\frac{cm^2}{V \cdot s}]$ ), and threshold voltage ( $V_t$ )[18].

The carriers' mobility  $\mu$  describes the drift velocity of a particle in an applied electric field, thus the transistor's capability to drive electric current. Usually, the carrier mobility of MOS transistors presents a very complex temperature dependence. However, in general, the mobility is said to decrease with temperature increase.

In the case of threshold voltage, its rate of change also follows the same principle of the carriers mobility. However, it usually has a more straightforward dependency of decreasing linearly with temperature increase.

The work of Freijado *et al.* [19] presents a model that tries to encompass all these variations and test the impact that temperature has on the propagation delay. The designed model predicts that the propagation delay increases linearly with the temperature increase, which would imply that the size of the voltage guardband reduces when the temperature increases.

#### 2.2.3 Power Consumption

On a CMOS circuit, the total consumed power is decomposed into the dynamic and static parts

$$P_{CMOS} = P_{dynamic} + P_{static}.$$

(2.6)

The dynamic power relates to the power that is consumed by the transistors flipping stages (inverting the logic values), and corresponds to the power of charging and discharging the internal net capacitances. This value is proportional to the frequency that this change occurs. Equation 2.7 represents the general formulation of the dynamic power, where *a* represents the device utilization factor, *C* the total capacitance of the circuit, *V* the circuit supply voltage, and *f* the frequency of operation [20].

$$P_{dynamic} = aCV^2 f \tag{2.7}$$

On the other hand, the static part of the power consumption comprehends three components:  $P_{leakage}$ ,  $P_{short-circuit}$  and  $P_{DC}$  [21]. The leakage power is independent of the transistors flip, and it represents the flow of electrons between the transistors' source, drain, and gate, known as leakage current. The short-circuit power comes from the instantaneous short-circuit connection between the supply voltage and the ground when the transistor flips. Finally, the Direct Current (DC) power corresponds to the power needed for powering the circuit. Equation 2.8 represents the expression with all static power consumption components.

$$P_{static} = P_{leakage} + P_{short-circuit} + P_{DC}$$

(2.8)

Usually, the dynamic power dominates the total power consumption of a circuit. However, with the current tendency to reduce the manufacturing size of transistors, the static power is becoming a more significant part [22, 23]. Nevertheless, as a common reference, and due to the usually dominant

weight of the dynamic power on the total power consumption, the power used by a CMOS circuit usually changes linearly with the clock frequency and quadratically with the supplied voltage.

### 2.3 Dynamic Voltage and Frequency Scaling

The widespread use of GPUs in both supercomputers and personal computing machines comes at the cost of a significant increase in power consumption. While a typical modern CPU consumes about 50 to 100W, it is common to see GPUs consuming between 200 and 300W of power. With these figures, the use of energy efficiency techniques to try to reduce power consumption becomes a vital issue.

As stated in Section 2.2.3, the power consumption of a CMOS circuit increases linearly with the operating frequency and quadratically with the supplied voltage. Thus, a direct manner of reducing this figure is by directly acting on these two parameters. A common approach of achieving this is the application of Dynamic Voltage and Frequency Scaling (DVFS), consisting on a power management technique which performs "on the fly" control of frequency and voltage. In particular,DVFS allows for an energy efficiency improvement by matching voltage and frequency settings to the GPU utilization. When the GPU is idle, the frequency is lowered, and when it is active, the frequency is increased. As presented in the previous section, the frequency scaling also implies a consequent change in voltage, to accommodate the fulfillment of the critical path timing constraints.

In general, the applied voltage level V is a function of the current operating frequency f, in the form of V(f). However, by properly controlling the clock frequency, the required voltage level for stable operation of the circuit can also be maintained or even reduced, leading to further power savings.

In general, modern GPU boards offer an independent control over two pairs of frequency and voltage. Each pair (or domain) acts on a distinct part of the GPU, intending to maximize the performance or reduce the power consumption. The first domain concerns the GPU core, acting on all SM/CUs, the cache, and the interconnection fabric. The second affects the DRAM chips that compose the video memory.

The clock frequency is an independently controlled (within the physical possibilities of the CMOS manufacturing process) variable, and its change directly reflects on the performance that is achieved by the GPU. An increase in the clock frequency of the core results in an improvement of the SM/CU execution speed, while the same change in the memory frequency will increase the DRAM I/O throughput [21]. The voltage level of each domain is dependent on the clock frequency being used and it is usually defined based on tests performed by the manufacturer to ensure the correct operation of the circuit, independently of the workload.

The two major GPU silicon vendors, AMD and NVIDIA, adopted the concept of performance levels on their products. Each performance level is a pair of frequency and voltage that can be applied to each GPU DVFS domains. These vary from low power and performance levels to high power and performance ones. The idea of having multiple performance levels is to allow the application to have the best point of operation. In the case of the first GPU device (AMD Vega 10 Frontier Edition) that is going to be used in the experimental phase of this dissertation, the GPU core has eight performance levels, while the memory has only four. Table 2.1 shows the reference values (for the pairs of frequency and voltage) for each of the core and memory performance levels. The frequency and voltage of higher performance levels reflect the expected behaviour, with an increase of the supply voltage to accommodate the frequency boost.

|       | Core            |              | Memory |                 |              |

|-------|-----------------|--------------|--------|-----------------|--------------|

| Level | Frequency [MHz] | Voltage [mV] | Level  | Frequency [MHz] | Voltage [mV] |

| 0     | 852             | 800          | 0      | 167             | 800          |

| 1     | 991             | 900          | 1      | 500             | 900          |

| 2     | 1138            | 950          | 2      | 800             | 950          |

| 3     | 1269            | 1000         | 3      | 945             | 1000         |

| 4     | 1348            | 1050         |        |                 |              |

| 5     | 1440            | 1100         |        |                 |              |

| 6     | 1528            | 1150         |        |                 |              |

| 7     | 1600            | 1200         |        |                 |              |

Table 2.1: GPU core and memory performance levels for the AMD Vega 10 Frontier Edition GPU.

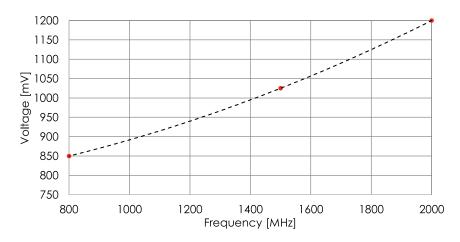

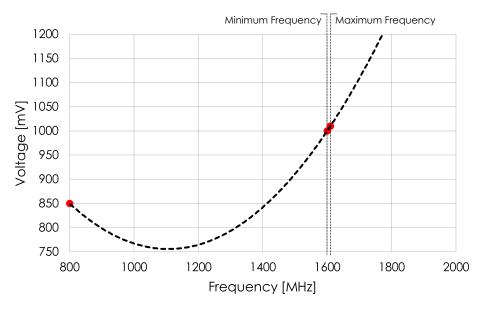

Newer GPU DVFS systems, like the one used on the second GPU under test (AMD Radeon 5700 XT) improve the number of performance levels by allowing for a continuous use of all frequency values within the valid range (versus discretizing the domain into a set number of performance levels). In this case, there are three user-defined frequency-voltage pairs on which a quadratic regression is computed (see Figure 2.8), creating a f(V) function that for every frequency, gives the correspondent voltage value.

Figure 2.8: GPU Core voltage frequency curve, red dots indicate the default user-defined voltage frequency pair - AMD Radeon 5700 XT.

### 2.3.1 Control Mechanism

The correct choice of the most appropriate performance level for each GPU DVFS domain when executing a given application is one of the topics that has deserved a special attention from both manufacturers and researchers, since the design of the DVFS controller has a significant impact on the GPU's performance and energy efficiency.

The first implementations of GPU DVFS controllers took a direct inspiration from the CPU DVFS controllers and can be largely classified into interval-based, inter-task, and intra-task DVFS schemes [24].

#### Interval-based

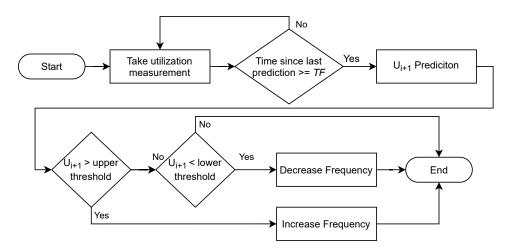

Interval-based algorithms rely on the periodical measurement of the device's utilization, setting the next frequency and voltage levels based on the average measurement of utilization. The utilization  $U_i$  reflects the percentage of working time,  $w_i$ , that was spent by the GPU over the last time frame  $TF_i$  and can be formulated using equation 2.9.

$$U_i = \frac{w_i}{TF_i} \tag{2.9}$$

By applying either a arithmetic, a geometric, a weighted average, or even a more complex metric over the last *n* measurements, the next utilization  $U_{i+1}$  is predicted. If the predicted value surpasses pre-determined upper or lower thresholds, the frequency is adjusted up or down accordingly [25]. A *governor* is a set of parameters (such as frequency and voltage tables), thresholds and a utilization prediction algorithm that controls how the interval-based DVFS works. By choosing a different *governor*, the DVFS system can react differently to the same workload. Figure 2.9 schematizes the periodic procedure executed by the DVFS system [25].

Figure 2.9: Interval-based DVFS procedure.

#### Inter/Intra task-based

The Inter and Intra task-based DVFS algorithms analyze the program source code, as well as some past runs profiling results to determine the optimal frequency/voltage for each task. This type of algorithm is composed of an intra-task and an inter-task analysis [26]. The intra-task part decomposes the process execution into the on-chip computation and off-chip access latencies. Based on the results, the optimal GPU core and memory frequencies are determined accordingly to the ratio between the two types of execution. Inter-task mechanisms utilize the intra-task results, assigning a signature to each type of task/process. By analyzing, in run-time, the GPU components' utilization, and using a lookup table that stores the signatures, the optimal frequency/voltage is selected for the sequence of tasks to be executed.

In general, the challenges of creating a better GPU DVFS mechanism relates to three factors: GPU power management, DVFS performance and power estimation tools and continuous changing architec-

ture. The current GPU devices deliver minimal and simplified power management mechanism, solely relying on controlling the device power cap. The continuous architectural changes introduced on each GPU generation does not allow for the creation and maturation of accurate quantitative GPU DVFS performance and power estimation tools. And again, the complete redo of the architecture on each generation also makes the energy efficiency strategies applied to one architecture design have different outcomes on the next one [21]. The observed results show that strategies like scaling up the processor frequency, race-to-idle [27] or "racing" [28], when a task is launched in the pursuit of finishing it as fast as possible and return to an idle state, prof to increase the energy efficiency of CPUs. However, that assumption not always results in the same outcome for GPUs [28].

#### **AMD/NVIDIA DVFS Mechanism Example**

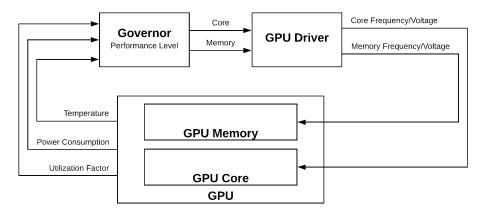

The GPU DVFS control mechanism that is used nowadays by both AMD and NVIDIA, schematized in figure 2.10, is primarily an interval-based one. In particular, the most recent AMD GPU DVFS mechanism is called Adaptive Frequency and Voltage Scaling (AFVS) [29]. It takes into account the voltage levels across the different parts of the GPU, the die temperature, the desired frequency and the total power consumption. In order to maintain the total power consumption within the required power and temperature envelope. Upon launching a new task and within a set power target, the GPU tries to achieve the highest possible frequency (or highest performance level). For that frequency configuration, it also adjusts the voltage level to the one required to ensure the correct operation. Naturally, with the high-est performance level, power and temperature will increase. When one of these parameters achieves the limit, the GPU decreases the frequency (or selecting a more energy-saving performance level) to maintain itself within the power and temperature target.

Figure 2.10: AMD/NVIDIA DVFS control mechanism.

The major drawback of current GPU DVFS implementations is not taking into account the type of tasks that the GPU is executing. The dominant control mechanism still considers the GPU as a black box and controls its DVFS settings by only looking at outside parameters. Even though such a black-box approach enables significant improvements in current hardware, it lacks the optimization of the frequency/voltage to the type of workload. For instance, a given application can be either compute-bound or memory-bound, depending on if the time that it takes to perform the task is limited by the processor performance or by the memory bandwidth and latency. This binary classification of applications also depends on the frequency of the core and memory. The same application can be compute-bounded at

a low core frequency but be memory-bounded at a higher one [30] (the bottleneck switches from the processing elements to the memory). In the case of a compute-bounded application, the limitation can be imposed by different components of the processor architecture, depend on the type of data (integer or floats) and on the intended precision (size of the operands). If one compares the computation with the same type of operands, but with different precision (for instance, 16 vs. 32 bits), even though the GPU uses the same arithmetic unit, the critical path for 32 bits operands is of increased length. Hence, the maximum delay between the input and the operations output increases with the operands' precision. Since no information about the application is provided to the DVFS controller, no adaptation of the V-F settings can be employed. Considering that the manufacturers do not usually tune their devices to the minimum voltage level (to accommodate for manufacturing imprecisions and to leave a safe guardband), there is some space to reduce the operating voltage of the circuits, leading to significant power savings.

Overall, the minimum operating voltage of each performance level is set at a high enough level to ensure the correct operation of the GPU, independently of the type of computations/workload. Nevertheless, it is possible to further fine-tune the voltage and frequency configuration if the type of task being executed is known at run-time.Furthermore, a significant limitation of the voltage-frequency control system is the time it takes to change and stabilize the intended V-F pair. On the case on the AMD Vega 10 Frontier Edition, the mechanism takes approximately 200-500 ms to change between performance levels [29].

#### 2.3.2 GPU DVFS Characterization

To improve the performance and energy efficiency of a GPU, it is important to characterize and analyze the effects of applying DVFS techniques on its operation, with a special emphasis in what concerns the impact of the different parameters on different workload scenarios.

A complete GPU DVFS characterization is explored in the literature using two methodologies. The first refers to experimental studies, where researchers use real GPUs to perform voltage and frequency scaling. However, due to past dominance of NVIDIA over AMD [5, 6] and the fact that this manufacturer only offers limited support for independent voltage scaling tools, the majority of the work act solely on frequency scaling. The second approach uses simulators, like GPGPU-Sim<sup>6</sup> and GPUWattch<sup>7</sup> [31], to simulate various scaling approaches, like GPU core number scaling and per-core DVFS [21]. The benefit of using simulators over real hardware comes on the increased flexibility, enabling the experimentation of scenarios not supported by the frequency/voltage scaling tools provided by the manufacturers. In both methodologies, the studies act on the impact on performance, energy consumption and overall energy efficiency.

The following subsections present a brief overview of some of these works.

#### **Experimental Approach**

Jiao *et al.* [32] scaled the GPU core and memory frequencies of an NVIDIA Tesla GTX 280 GPU using three types of workload: a compute-bounded dense matrix multiplication application; a memory bounded application that performs a dense matrix transpose; and a mixed workload, executing a Fast

<sup>&</sup>lt;sup>6</sup>http://www.gpgpu-sim.org/

<sup>&</sup>lt;sup>7</sup>http://www.gpgpu-sim.org/gpuwattch/

Fourier Transform (FFT) computation. The experimental study showed that for the same core-memory frequency settings, the three applications showed different performance and energy efficiency curves. While a compute bounded application showed to be insensitive to memory frequency scaling, the memory bounded application takes advantage of high memory frequency and low core frequency. At last, the mixed workload FFT application profits from both high core and memory frequency. In general, it was also shown that energy efficiency could be determined by the instructions per cycle (IPC) metric and by the global ratio of memory transactions by computation transactions.

Ge *et al.* [33] explored dense matrix multiplication kernel executions in more detail using an NVIDIA Kepler K20c GPU. The conducted work revealed that for this type of kernel (compute-bounded), the GPU's power and achievable performance is linear to the GPU core frequency and that the total energy consumption had no relation to frequency scaling. In all the used application tests, the energy efficiency has a linear relation with the GPU frequency, with the highest energy efficiency being achieved when the highest clock frequency was employed.

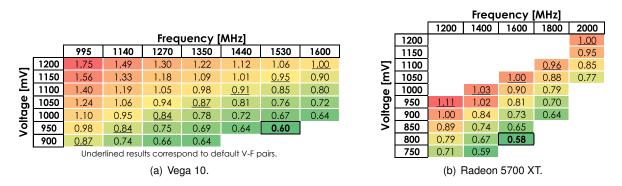

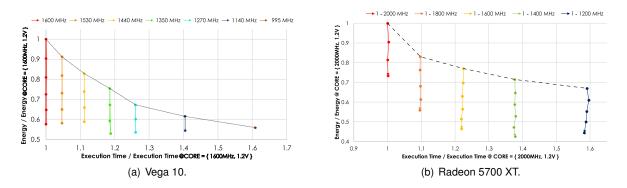

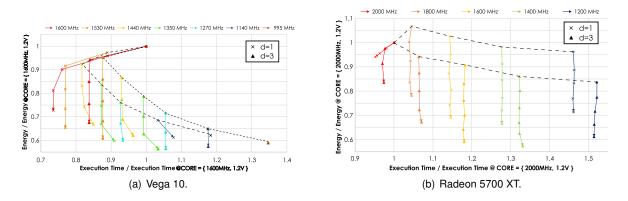

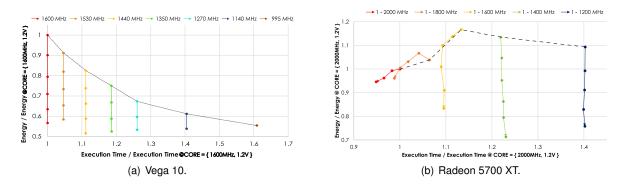

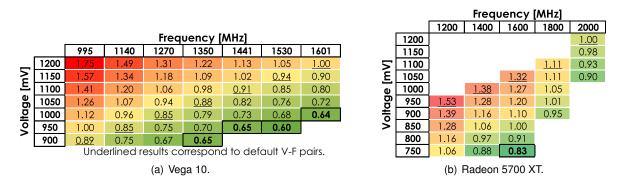

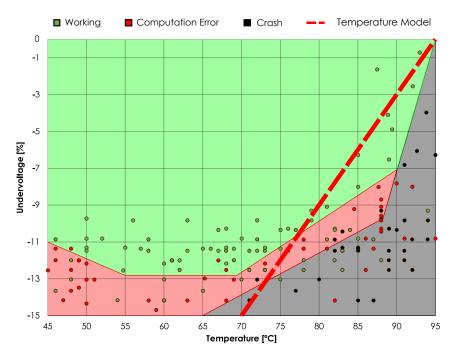

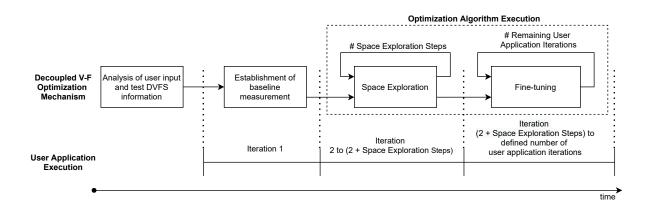

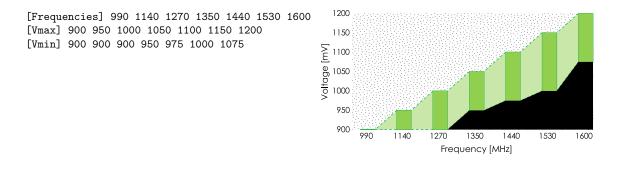

Abe *et al.* [34] introduced a global scaling procedure that combines the GPU core and memory frequency with the host CPU frequency, in order to minimize the energy consumption. The first experiment tried to optimize the computation of dense matrix multiplication with different matrix sizes. By using this global scheme on a small matrix leads to a 28% energy saving, when using low GPU memory frequency and high GPU core frequency. The same procedure was then enlarged to a more diverse set of 33 benchmarks, where all the possible combinations of a low, medium, and high GPU core and memory frequencies were tested to find the optimal working settings. It was found that energy consumption can be reduced as much as 75% with a performance loss of 30% when the best settings were used.